# Saarland University Department of Computer Science

# Low-Level Software Memory Safety Analysis: Attack and Defense

Dissertation zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Fakultät für Mathematik und Informatik der Universität des Saarlandes

> von Jianqiang Wang

> Saarbrücken, 2025

Tag des Kolloquiums: 04. Aug 2025

Dekan: Prof. Dr. Roland Speicher

**Prüfungsausschuss:** Vorsitzender: Prof. Dr. Reinhard Wilhelm Berichterstattende: Prof. Dr. Thorsten Holz

Prof. Dr. Andreas Zeller Prof. Dr. Mathias Payer

Akademischer Mitarbeiter: Dr. Hanwei Zhang

## Zusammenfassung

Low-Level-Software ist, wie der Name schon sagt, eine Art von Software, die enger mit der Hardware zusammenarbeitet als normale Anwendungen. Sie übernimmt in der Regel Aufgaben wie die Initialisierung der Hardware, die Einrichtung der Ausführungsumgebung und die direkte Interaktion mit den Hardware-Komponenten. Aufgrund der entscheidenden Rolle, die Low-Level-Software spielt, benötigt und erlangt sie naturgemäß höhere Hardware-Privilegien als andere Software, was sie zu einem vielversprechenden Ziel für Systemangreifer macht. Um die Hardware bequem zu steuern, verwenden Low-Level-Softwareentwickler häufig speicherunsichere Programmiersprachen wie C und C++. Einerseits erleichtert die direkte Speicherverwaltung den Entwicklungsprozess, andererseits macht sie die Low-Level-Software jedoch anfällig für Speicherverletzungs-Schwachstellen.

Ausgehend von den Ursachen und Folgen von Speicherverletzungs-Schwachstellen demonstriert diese Arbeit, dass Speicherunsicherheit eine Hauptbedrohung für die Sicherheit von Low-Level-Software darstellt. Nachfolgend werden Speicherunsicherheitsprobleme von Low-Level-Software aus offensiver und defensiver Perspektive analysiert und diskutiert. Im offensiven Szenario geht die Arbeit auf die Probleme ein, die die Erkennung von Speicherverletzungs-Schwachstellen noch behindern. Insbesondere wird eine Technik namens Fuzz-Testing angewandt, bei der zufällige Eingaben in die Software eingespeist werden. Dazu wurden maßgeschneiderte Fuzzer entworfen und implementiert, um Speicherverletzungs-Schwachstellen in Low-Level-Software, Firmware eingebetteter Systeme und Bootloadern zu finden. Die Fuzzer zielen darauf ab, möglichst viele Teile der Low-Level-Software zu erkunden und möglichst viele Abstürze auszulösen. In den Experimenten wurden 46 zuvor unbekannte Schwachstellen gefunden, denen 11 CVEs (Schwachstellen-Identifikationsnummern) zugewiesen wurden. Aus einer defensiven Perspektive ist die Bereitstellung eines einfach zu verwendenden Frameworks mit umfangreichen Funktionen für High-Level-Anwendungen bei gleichzeitiger Gewährleistung der Speicher-Sicherheitsgarantien ein wesentlicher Aspekt. Um dieses Problem zu lösen, wurde im Rahmen dieser Arbeit ein Trusted Execution Environment-Framework für die RISC-V-Architektur entworfen und implementiert, das die RISC-V-Hypervisor-Erweiterung und eine bestehende Hardware-Speicherisolationstechnik nutzt. Das Framework bietet vollständige Rückwärtskompatibilität und sicheres I/O, was bedeutet, dass eine unveränderte virtuelle Maschine direkt auf dem Framework ausgeführt werden kann und von einer transparenten sicheren I/O-Übertragung profitiert. Abschließend wird gezeigt, dass das Framework eine ähnliche Leistung wie die AMD-SEV-Erweiterung erreichte und nur minimale Zusatzkosten im Vergleich zur nativen Ausführung verursachte.

## **Abstract**

Low-level software, as the name suggests, is the kind of software that runs more closely with the hardware than normal applications. They usually undertake the responsibilities of initializing the hardware, setting up the execution environment, and directly interacting with the hardware functionalities. Due to the intrinsic features of the key role played by low-level software, it naturally requires and gains higher hardware privilege than other software to run, making it a promising target for system attackers. To conveniently manipulate the hardware, low-level software developers commonly adopt memory-unsafe programming languages such as C and C++. On the one hand, the direct memory access programming language makes the development process easier, on the other hand, however, it makes the low-level software prone to be compromised by memory corruption vulnerabilities.

In this thesis, we start with the causes and consequences of memory corruption vulnerability and then showcase that memory safety issue is a main threat to low-level software security. We discuss and analyze low-level software memory safety issues in terms of both their attack and defense sides. From the perspective of the attack scenario, we tackle the problems that still hinder the detection of memory corruption vulnerability detection. In particular, feeding random inputs to the software—a technique called fuzz testing—is used. Specifically, We designed and implemented tailored fuzzers to find the memory corruption vulnerabilities in the low-level software, embedded system firmware, and bootloader. For each, the fuzzers aim to explore as many parts of the low-level software as well as trigger more crashes as possible. In our experiments, 46 previously unknown vulnerabilities were found, and 11 CVEs were assigned to the findings. From the perspective of defense, providing an easy-to-use framework with rich features for highlevel applications while maintaining the memory safety guarantees is the essential part. To solve this problem, we designed and implemented a trusted execution environment framework for RISC-V architecture by utilizing RISC-V hypervisor extension and an existing hardware memory isolation technique. The framework provides full backward compatibility and secure IO, which means an unmodified virtual machine can run directly on top of the framework and benefit from transparent, secure IO transmission. Our experiment showed that the framework achieved similar performance with AMD SEV extension and trivial overhead compared with native running.

# Background of This Thesis

This thesis is based on the papers mentioned in the following. The author contributed to all papers as the main author.

- A Comprehensive Memory Safety Analysis of Bootloaders (NDSS'25)

- AidFuzzer: Adaptive Interrupt-Driven Firmware Fuzzing via Run-Time State Recognition (Usenix security'24)

- VirTEE: A Full Backward-Compatible TEE with Native Live Migration and Secure I/O (DAC'22)

### Further Contributions of the Author

The author also fully or partially contributed to the following papers.

- SEnFuzzer: Detecting SGX Memory Corruption via Information Feedback and Tailored Interface Analysis (RAID'23)

- RiscyROP: Automated Return-Oriented Programming Attacks on RISC-V and ARM64 (RAID'22)

- NLP-EYE: Detecting Memory Corruptions via Semantic-Aware Memory Operation Function Identification (RAID'19)

# Acknowledgments

I want to thank everyone who helped me during my pursuit of the PhD. My kind and friendly lab mates, paper co-authors, and friends' companions motivated me to work and live in a cozy environment. I want to give special thanks to my supervisor, Thorsten Holz, whose humble, gentle, and kind personality impressed me when I started working in his group. I enjoyed the atmosphere he built for this group and I really appreciate being part of it.

# Contents

| 1 | Inti | roduct  | ion                                                    | 1          |

|---|------|---------|--------------------------------------------------------|------------|

|   | 1.1  | Low-L   | Level Software and Its Risks                           | 3          |

|   | 1.2  | Memo    | ory Safety Issues in Low-Level Software                | 3          |

|   | 1.3  | Resea   | rch Focuses                                            | 7          |

|   | 1.4  |         | s Roadmap                                              | 8          |

| 2 | Tec  | hnical  | Background                                             | 9          |

|   | 2.1  | Hardv   | vare Features                                          | 11         |

|   |      | 2.1.1   | Trusted Execution Environment                          | 11         |

|   |      | 2.1.2   | Hypervisor                                             | 13         |

|   |      | 2.1.3   | Intel PT and VT-x                                      | 14         |

|   |      | 2.1.4   | BIOS and Secure Boot                                   | 15         |

|   | 2.2  | Embe    | dded System                                            | 15         |

|   |      | 2.2.1   | Interrupt                                              | 16         |

|   |      | 2.2.2   | Memory-Mapped I/O                                      | 16         |

|   | 2.3  | Memo    | ory Corruption Vulnerability                           | 16         |

|   |      | 2.3.1   | Exploitation                                           | 16         |

|   |      | 2.3.2   | Mitigation                                             | 17         |

|   | 2.4  | Fuzz 7  | Testing                                                | 18         |

|   |      | 2.4.1   | Black-Box Fuzzing                                      | 18         |

|   |      | 2.4.2   | Code Coverage Feedback                                 | 18         |

|   |      | 2.4.3   | Feedbacks Beyond Code Coverage                         | 19         |

|   |      | 2.4.4   | Fuzzing Modularization                                 | 19         |

|   |      | 2.4.5   | Domain Specific Fuzzing                                | 20         |

| 3 | Boo  | otloade | er: Comprehensive Attack Surfaces Analysis and Generic |            |

|   | Fuz  | zing F  | ramework                                               | <b>2</b> 1 |

|   | 3.1  | Overv   | iew                                                    | 23         |

|   | 3.2  | Syster  | m Boot Process and Bootloader Features                 | 25         |

|   |      | 3.2.1   | PC Firmware                                            | 26         |

|   |      | 3.2.2   | Bootloader Workflow                                    | 27         |

|   |      | 3.2.3   | Runtime Environment                                    | 27         |

|   |      | 3.2.4   | Bootloader Features                                    | 28         |

|   | 3.3  | Bootle  | oader Memory Safety Analysis                           | 29         |

|   |      | 3.3.1   | Survey and Lessons Learned                             | 29         |

|   |      | 3.3.2   | Threat Model                                           | 30         |

# CONTENTS

|   |               | 3.3.3 Target Selection                                    | 31        |

|---|---------------|-----------------------------------------------------------|-----------|

|   |               | 3.3.4 Attack Surface Analysis in Practice                 | 32        |

|   | 3.4           | Generic Bootloader Fuzzing Framework Design               | 35        |

|   |               | 3.4.1 Harness                                             | 35        |

|   |               | 3.4.2 Fuzzing Engine                                      | 37        |

|   |               | 3.4.3 Crash Detection                                     | 37        |

|   | 3.5           | Evaluation                                                | 38        |

|   |               | 3.5.1 Experiment Setup                                    | 39        |

|   |               | 3.5.2 Reproducibility of Known Vulnerabilities (RQ1)      | 39        |

|   |               | 3.5.3 Finding New Vulnerabilities (RQ2)                   | 41        |

|   |               | 3.5.4 Comparison with Other Works (RQ3)                   | 42        |

|   |               | 3.5.5 Manual Effort (RQ4)                                 | 44        |

|   | 3.6           | Discussion                                                | 45        |

|   | 3.7           | Conclusion                                                | 47        |

|   |               |                                                           |           |

| 4 | $\mathbf{Em}$ | bedded System Firmware: Adaptive Interrupt Driven Fuzzing | 49        |

|   | 4.1           | Overview                                                  | 51        |

|   | 4.2           | Arm Cortex-M NVIC Interrupt                               | 53        |

|   |               | 4.2.1 IRQ and Interrupt Vector Table                      | 53        |

|   |               | 4.2.2 NVIC Configuration                                  | 54        |

|   |               | 4.2.3 Types of NVIC Interrupts                            | 54        |

|   |               | 4.2.4 QEMU NVIC Implementation                            | 55        |

|   | 4.3           | Firmware Fuzzing Interrupt Triggering Analysis            | 55        |

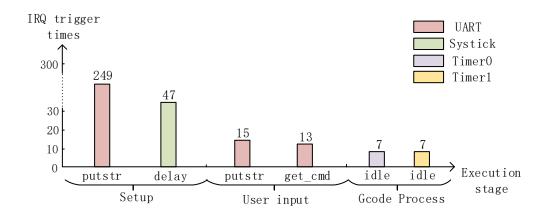

|   |               | 4.3.1 Running Examples                                    | 55        |

|   |               | 4.3.2 Challenges                                          | 58        |

|   |               | 4.3.3 Insights                                            | 58        |

|   | 4.4           | Interrupt-Driven Firmware Fuzzing Design                  | 59        |

|   |               | 4.4.1 Threat Model                                        | 59        |

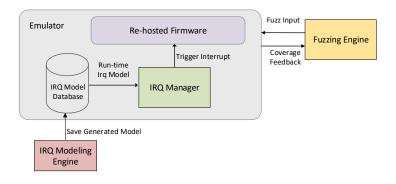

|   |               | 4.4.2 High-Level Overview                                 | 60        |

|   |               | 4.4.3 IRQ Modeling Engine                                 | 60        |

|   |               | 4.4.4 Emulator                                            | 62        |

|   |               | 4.4.5 Fuzzing Engine                                      | 63        |

|   | 4.5           | Evaluation                                                | 64        |

|   |               | 4.5.1 Experiment Setup                                    | 64        |

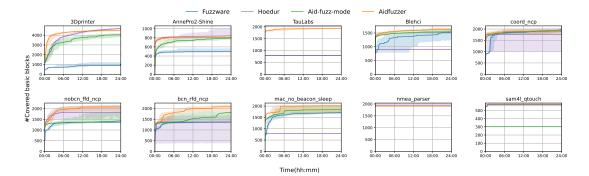

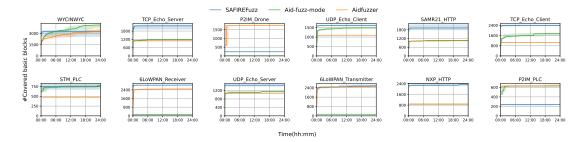

|   |               | 4.5.2 Effectiveness of AidFuzzer (RQ1)                    | 65        |

|   |               | 4.5.3 Soundness of IRQ Modeling (RQ2)                     | 68        |

|   |               | 4.5.4 Overhead (RQ3)                                      | 71        |

|   |               | 4.5.5 IRQ Modeling Comparison with AIM (RQ4)              | 72        |

|   | 4.6           | Discussion                                                | 72        |

|   | 4.7           | Conclusion                                                | 73        |

| _ | (DE)          | E A . P P D L. C                                          |           |

| 5 |               | E Application: Backward Compatible and Secure TEE Design  | <b>75</b> |

|   | 5.1           | Overview                                                  | 77        |

|   | 5.2           | RISC-V Hypervisor Extension                               | 78<br>78  |

|   |               | aza biowev architecture Erivilege Leveis                  | 17        |

# **CONTENTS**

| 5.5 | 5.5.1<br>5.5.2<br>5.5.3                    | Security Monitor       8         Enclave Monitor       8         Enclave Setup       8         ation       8         Experiment Setup       8         Run-time Performance Overhead (RQ1)       8         VirTEE Feature Overhead (RQ2)       8         ssion       8 |

|-----|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5 | 5.4.5<br>5.4.6<br>Evalua<br>5.5.1<br>5.5.2 | Enclave Monitor         85           Enclave Setup         85           ation         84           Experiment Setup         84           Run-time Performance Overhead (RQ1)         85                                                                               |

| 5.5 | 5.4.5<br>5.4.6<br>Evalua<br>5.5.1          | Enclave Monitor                                                                                                                                                                                                                                                       |

| 5.5 | 5.4.5<br>5.4.6<br>Evalua                   | Enclave Monitor         85           Enclave Setup         85           ation         86                                                                                                                                                                              |

|     | 5.4.5<br>5.4.6                             | Enclave Monitor                                                                                                                                                                                                                                                       |

|     | 5.4.5                                      | Enclave Monitor                                                                                                                                                                                                                                                       |

|     |                                            |                                                                                                                                                                                                                                                                       |

|     | 511                                        | C: t M: t                                                                                                                                                                                                                                                             |

|     | 0.2.0                                      | VirTEE Hardware                                                                                                                                                                                                                                                       |

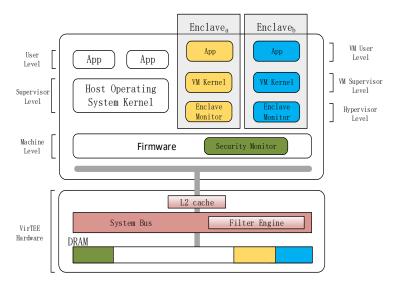

|     | 5.4.2                                      | Design Overview                                                                                                                                                                                                                                                       |

|     | 5.4.1                                      | Adversary Model                                                                                                                                                                                                                                                       |

| 5.4 | Backw                                      | rard Compatible and Secure TEE Design                                                                                                                                                                                                                                 |

|     | 5.3.2                                      | Less Attack Surfaces Security                                                                                                                                                                                                                                         |

|     | 5.3.1                                      | Backward Compatibility                                                                                                                                                                                                                                                |

| 5.3 | Secure                                     | TEE Design Analysis                                                                                                                                                                                                                                                   |

|     | <ul><li>5.3</li><li>5.4</li></ul>          | 5.3.1<br>5.3.2<br>5.4 Backw<br>5.4.1<br>5.4.2<br>5.4.3                                                                                                                                                                                                                |

# List of Figures

| 2.1 | SGX design overview                                                    |

|-----|------------------------------------------------------------------------|

| 2.2 | TrustZone on ARM Cortex-A                                              |

| 2.3 | Type-1 hypervisor                                                      |

| 2.4 | Type-2 hypervisor                                                      |

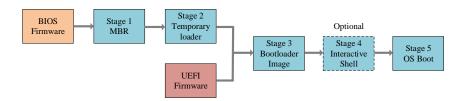

| 3.1 | Schematic overview of bootloader workflow                              |

| 3.2 | Number and root causes of collected bootloader CVEs                    |

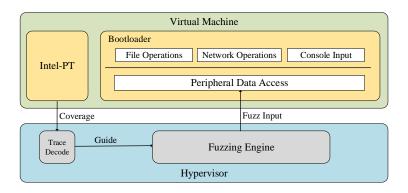

| 3.3 | Bootloader fuzzing overview                                            |

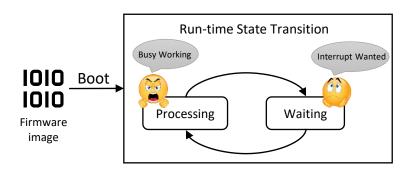

| 4.1 | Firmware run-time state transition cycle                               |

| 4.2 | Design overview of AidFuzzer                                           |

| 4.3 | AidFuzzer basic block coverage compared with state-of-the-art works 68 |

| 4.4 | AidFuzzer basic block coverage compared with SafireFuzz 67             |

| 4.5 | Interrupt triggering in 3Dprinter                                      |

| 5.1 | Design overview of VirTEE                                              |

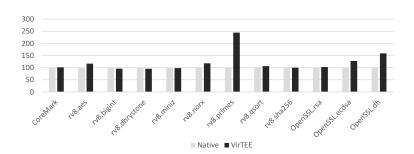

| 5.2 | VirTEE's performance overhead                                          |

# List of Tables

| 3.1  | Number and distribution of collected bootloader CVEs              | 30 |

|------|-------------------------------------------------------------------|----|

| 3.2  | Bootloader analysis targets                                       | 31 |

| 3.3  | Bootloader attack surface analysis for storage device input $(1)$ | 32 |

| 3.4  | Bootloader attack surface analysis for storage device input $(2)$ | 32 |

| 3.5  | Bootloader attack surface analysis for network device input (1)   | 34 |

| 3.6  | Bootloader attack surface analysis for network device input (2)   | 34 |

| 3.7  | Bootloader CVEs reproduction                                      | 38 |

| 3.8  | Number of modified or added lines of code to bootloaders          | 39 |

| 3.9  | Detected bootloader vulnerabilities compared with static analysis | 39 |

| 3.10 | Detected bootloader vulnerabilities information                   | 48 |

| 4.1  | Firmware dataset for AidFuzzer testing                            | 65 |

| 4.2  | Crash analysis for AidFuzzer                                      | 67 |

| 4.3  | AidFuzzer IRQ modeling result                                     | 68 |

| 4.4  | Extra overhead caused by IRQ modeling                             | 71 |

| 4.5  | IRQ modeling compared with AIM                                    | 72 |

# Introduction

### 1.1 Low-Level Software and Its Risks

Modern computer systems provide a wide range of methods to protect end-users from malicious attackers. Hardware mechanisms or extended features directly or indirectly enforce those protections. As the name suggests, low-level software is used by developers to drive the mechanisms and features, which thus runs closely to the hardware. A typical example is the permission control system for users and groups supported by all Linux kernels. Although fully implemented by software, the permission control system implementation in an x86 architecture platform is based on a processor privilege isolation mechanism where the kernel space and user space code run on different privilege levels. The kernel, which functions as low-level software, implements permission control and governs the execution of user-space applications. It is unavoidable for an attacker who resides in user space and aims to bypass the permission control to follow the processor-enforced access control, which states that the user space code cannot directly read or write kernel space memory. Software vulnerability, especially memory corruption in low-level software, plays an important role in the system attack scenario to help attackers achieve their goals.

Memory corruption vulnerabilities can lead to severe effects when exploited properly. For example, the Heartbleed out-of-bound read vulnerability (CVE-2014-0160) in OpenSSL reported in 2014 can leak secret data from a server. A write-to-read-only-memory vulnerability (DirtyCOW) in the Linux kernel (CVE-2016-5195) makes use of a race condition to escalate from user to root privileges. A report by Microsoft demonstrated that around 70 percent of vulnerabilities in their products are memory safety issues [150].

Unfortunately, to gain better performance and manipulate the hardware conveniently, memory-unsafe programming languages such as C and C++ are commonly adopted by low-level software developers. On the one hand, the choice makes the development process easier, however, on the other hand, C and C++ do not automatically prohibit memory corruption, leaving a large number of vulnerabilities in the software. Nowadays, memory-unsafe ones are still the mainstream programming languages [53] in low-level software such as operating system kernels, hypervisors, and bootloaders.

# 1.2 Memory Safety Issues in Low-Level Software

Low-level software is usually responsible for setting up the environment and communicating with the hardware. Naturally, it requires a higher hardware privilege or special access permission to execute, making it an attractive target for attackers. The reasons are straightforward: the earlier or the higher privilege malicious code can get to execute, the more severe consequences the attack can cause. For example, compromising a user-space application might cause a segmentation fault or data leakage within a single process. However, a kernel memory corruption vulnerability can lead to root privilege escalation and affect all system processes. Even worse, if a memory safety issue occurs in the BIOS firmware, the malicious code might remain after reinstalling the operating system.

Attack and defense against memory safety issues in low-level software has been a

cat-and-mouse game for a long time. The battlefields spread across various platforms, hardware mechanisms, processor features, and low-level software. We briefly introduce the current situation based on the rough loading time of the low-level software.

BIOS. Legacy BIOS firmware was replaced by modern UEFI standard firmware, which the researchers focus on nowadays. Finding memory corruption vulnerabilities in system management mode code is a popular topic. Prior works proposed symbolic execution [18], static analysis [237, 188, 51, 52], fuzzing [236, 235], and a mix of them [99] to detect memory safety issues in system management mode interrupt handlers. Memory corruption vulnerabilities and exploitations beyond the system management mode, such as [72, 142, 62, 230, 194] in UEFI firmware were found. Despite the severe effects, software protections such as CFI enforcement and obfuscation against memory corruption vulnerabilities in UEFI firmware are still missing. EDK II [210], the modern, featurerich, cross-platform firmware development environment provides basic address sanitizer features for developers to uncover the issues in the early stage. However, it is far from enough to prohibit them from happening. Surve et al. systematically analyzed UEFI security [198]. Besides memory safety issues, they also pinpoint other attacks, such as credential theft and UEFI firmware image tampering. UEFI memory safety is far from well-investigated due to its complexity. Since static analysis cannot be applied to largescale software because of its performance bottleneck, dynamic analysis is the preferred method. Modern dynamic analysis usually requires the execution environment to gain run-time data. However, the UEFI firmware image is tightly coupled with the processor and platform. The state-of-the-art simulator Qemu [20] supports hundreds of CPU models and platforms—which seems a lot, but still does not satisfy the requirements compared with tens of thousands of real-world CPU models and millions of peripherals. Without a simulated environment, the loss of run-time data, such as function pointers and port register value, hinders the deep analysis of the firmware image. It is still unclear how to simulate the full UEFI firmware run-time environment and perform a memory safety analysis on it.

**Bootloader.** With the legacy BIOS, the bootloader starts from the master boot record (MBR). However, it functions as a UEFI application in the modern epoch. The bootloader is supposed to be the bridge between the firmware and the operating system. The first edition of the popular Linux bootloader GRUB [87] was released in 1995. Originally, it only supported less than ten types of file systems. However, nowadays, bootloaders gradually provide richer features for end-users, such as customized GUI, various file systems, and user authentication. As the code base grows, it inevitably exposes more memory corruption vulnerabilities than before. There are several scattered works targeting bootloader vulnerability detection. Axtens [60] and Starke [157] have proposed fuzzing techniques for GRUB [87] and Das U-Boot [63]. Mobile device bootloaders are usually closed-source and hard to analyze. BootStomp [174] and Roee [93] have only analyzed bootloaders for Android systems, with a specific focus: BootStomp analyzed storage data controlled by the attacker that could compromise the bootloader, while Roee focused exclusively on command line inputs. Despite the efforts made by researchers on the bootloader memory safety analysis, a comprehensive analysis of bootloaders is still missing, which is what we need to address in this thesis.

**Hypervisor.** During the last five years, hypervisor security has been a hot topic.

After the first hypervisor fuzzing work VDF [94] that targets a single Qemu simulated device was introduced, many subsequent types of research such as Truman [137], HY-PERPILL [30], Morphuzz [28], HYPER-CUBE [182], V-shuttle [163], MundoFuzz [154], HyperFuzzer [84] were proposed. Most of them focus on virtual devices, which comprise the majority of the hypervisor code base. The inputs from the virtual machine to the simulated devices consist of two main parts: the port IO and the DMA buffer. The fuzzing works utilize the processor features that the device registers accessing traps the execution into the hypervisor to inject the fuzz input into the hypervisor. Inferring the address of the DMA buffer is tackled case by case. For example, V-shuttle takes advantage of hooking the Qemu function pci dma read. Fuzzing a closed-source hypervisor is tough due to its complex run-time environment. HYPERPILL identifies the universal and general hypervisor-processor interaction behavior, takes a snapshot, and performs fuzzing on the snapshot to overcome the issue. Embedded system hypervisors such as QNX [22] have not been well studied yet. Commercial embedded systems may not allow the user to inspect device states such as physical memory, making it impossible to take a snapshot of the device. Besides, the embedded system peripherals are highly customized, and no public documentation is available. Simulating such a system is not a reasonable way to perform fuzzing. When conducting on-device fuzzing, dealing with other problems, such as coverage feedback and crash reproduction, needs to be considered. The majority of the memory corruption vulnerabilities exist in virtual device implementations. As the virtual devices are implemented purely in software, protection against hypervisor memory corruption vulnerabilities should rely on general protections such as CFI, and ASLR instead of specific methods. The Virtio [158] specification does not mention the security design or implementation that must be followed by developers. Applying mature and general protections such as enforced CFI to virtual devices might be viable in the situation.

OS Kernel. The operating system (OS) kernel has always been the main arena of memory safety attack and defense. The kernel exposes interfaces for user space applications, interacts with devices, and runs multiple threads, making it a complex low-level software. Typical kernel-specific memory corruption vulnerabilities such as double-fetch [222, 233, 223, 184] and race conditions [123, 13, 65, 71, 219, 220, 26, 110] continue to threaten the kernel security. A large amount of kernel fuzzing works target malicious input from user space applications [89, 116, 196, 234, 29, 162, 41, 197, 109, 82, 238, 243, devices [195, 166, 190, 231], or user-specified origins [183, 181]. In addition, static analysis [222, 135, 139, 85], and a mix of them [202, 138, 44] were proposed as well. They focus on different parts of the kernel, such as file systems, device drivers, error handlers, and interrupt service routines, tackling various problems such as system call sequence ordering, input seed generation, device simulation, and system call parameter format reconstruction. Due to the complexity of the kernel, memory safety issues in such an environment are hard to catch and hide in the corner. Static analysis is unsuitable for such large-scale software, and setting up a real or simulated environment is also difficult. The multi-dimensional inputs from user space and device drivers make the problems even harder. Common memory protections have already been integrated into the kernel source code base [207]. Besides, plenty of research protections have been designed for the kernel [239]. However, we believe that there is no silver bullet to handle the problem, and memory corruption vulnerabilities will continue to exist, and new methods will come up by researchers as well.

Embedded System Firmware. There are two main types of embedded system firmware: POSIX-compatible Unix-like systems and Real-Time Operating Systems (RTOS). A Real-Time Operating System (RTOS) is used in low-power embedded devices because it is lightweight, allows for direct peripheral manipulation, and requires little memory. The Unix-like system provides a fully featured kernel and user space applications. Emulating the full or part of the system in a virtual environment poses challenges. Researchers proposed analyzing Unix-like systems by fuzzing them in a partially or fully simulated environment (FIRM-AFL [246], Firmadyne [34], Firmae [117], Greenhouse [203], EQUAFL [247], FIRMWIRE [96], FirmSolo [3]), fuzzing them ondevice (IotFuzzer [38]), static analysis (Feng et al. [76], DTaint [42], Firmxray [226], Lara [244], PASAN [118]), LLM-assisted analysis (mGPTFuzz [136]), and symbolic execution (Firmusb [95]). Analyzing RTOS firmware often involves a technique called rehosting as the low-power devices are not designed for high-throughput executions. Researchers proposed specific rehosting-based fuzzing for RTOS firmware such as P2IM [74], HALucinator [46], DICE [144], D-Box [143], SHiFT [145], CO3 [130], Fuzzware [177], Hoedur [178], Safirefuzz [185], MultiFuzz [43] PERRY [124], Sfuzz [39]. Detecting embedded system firmware memory corruption is challenging. The complex closed-source peripheral standard makes the situation even worse. An example is the interrupt-triggering problem. If the peripheral interrupt is not triggered properly when rehosting an RTOS firmware, the fuzzing process might be hindered. In this thesis, we solve this problem by proposing an adaptive interrupt-driven firmware fuzzing technique. Moreover, the question of how to analyze the embedded system's high-level protocol logic, such as Bluetooth and TCP/IP or application layer protocol stacks, has not been well addressed vet.

**TEE Application.** For the Trusted Execution Environment (TEE), researchers focus more on the design and implementation of a robust TEE system. Penglai [75] and Keystone [121] provided their solutions to build a new TEE system based on the existing physical memory isolation mechanism, such as RISC-V PMP. LibOS based solutions such as Graphene [211], Occlum [189], SGX-LKL-OE [170], Fortanix [125], SCONE [6] try to port unmodified legacy applications to Intel SGX. Chen et al. [36, 35, 107, 37] proposed potential attestation issues and their countermeasures for TEE applications. However, the memory safety issue is also a non-negligible aspect. Lee [122], Bulck [216], Checkoway [33], and Biondo [21] mentioned that memory corruption vulnerabilities and the exploitation methods do not disappear within the TEE environment. Even worse, SmashEx [58] showed that the majority of the officially provided TEE SDKs are all vulnerable to a kind of exception-handling-driven attack. To detect memory corruption vulnerabilities in TEE applications, model checking [14], symbolic execution [115, 47] and fuzzing [59, 48, 240, 224, 40] were introduced by researchers. To protect the TEE applications from memory corruption, Poster [67] and Wang et al. [221] proposed to use the memory-safe Rust language to rewrite the enclave code. BesFS [192] presented an Iago-safe API specification to defend against Iago attacks. MPTEE [245] used bound check to add flexible page permission to enclave memory. SGXPecial [152] extended the Edger8r tool of the Intel SGX SDK to generate more restricted ECALL/OCALL interfaces. Intel has abandoned SGX and will not include it in new processors, which indicates the end of application-based TEE systems. The future of mainstream TEEs will be dominated by virtual machine-integrated design systems. Memory safety issues will continue to exist in the TEE applications as long as they communicate with normal applications. However, analyzing virtual machine-integrated TEE applications leaves more challenges, such as a hard-to-setup environment, to researchers. In this thesis, we propose a fully backward-compatible secure TEE framework based on a RISC-V hypervisor extension. We address the TEE memory safety issues by combining an unmodified OS kernel and a lightweight hypervisor shim that provides the necessary interfaces for the OS.

### 1.3 Research Focuses

In this thesis, we focus on three typical low-level software, bootloader, embedded system firmware, and TEE application, to analyze their memory safety issues in terms of both attack and defense.

- 1. Bootloader. A bootloader is loaded into memory and gets executed at the early stage during the system boot process. During the secure boot process, it undertakes the responsibility of verifying the integrity of the next component, usually the operating system kernel image. If the kernel is not signed with a valid key, then it rejects loading. Due to the important role played by the bootloader, it is supposed to be designed and implemented securely. However, during the last decades, the bootloader has provided the end-users with rich features, and thus, its code base is getting larger and larger. However, a comprehensive memory safety analysis against the bootloader and a framework for detecting bootloader memory corruption vulnerabilities is still missing. In this thesis, we propose a comprehensive memory safety analysis against nine modern bootloaders. We thoroughly analyze the attack surfaces and how an attacker could exploit the vulnerabilities found to gain system privilege. Based on our observation, we design and implement a universal fuzzing framework to detect memory corruption vulnerabilities in various bootloaders. The framework is compatible with the majority of modern bootloaders despite their implementation details. We found 39 new vulnerabilities and five CVEs were assigned to our findings.

- 2. Embedded System Firmware. RTOS is widely used in embedded systems. Fuzzing has proven to be an efficient and effective method to detect RTOS memory corruption vulnerabilities. However, low-powered and slow-speed embedded devices are not designed for fuzzing due to their small throughput. Therefore, prior fuzzing works targeting RTOS run it in a simulated environment—a technique called re-hosting. The re-hosting environment simulates the processor, memory, and necessary peripherals to support the RTOS image execution. However, prior works rarely considered the peripheral interrupt triggering problem, which is a fundamental part of RTOS re-hosting and fuzzing. Without a proper interrupt-triggering mechanism, the RTOS may crash or get stuck in a very early stage. The fuzzing effectiveness can also be hindered due to improper interrupt triggering.

We observe that to solve the interrupt-triggering problem, identifying the RTOS run-time state is the key point. The correct execution of RTOS demands an interrupt only when it is in a specific run-time state. Based on this insight, we designed and implemented a fuzzing framework, Aidfuzzer, to tackle the interrupt-triggering problem in RTOS fuzzing. Aidfuzzer identifies the RTOS runt-time state dynamically, and triggers interrupts when necessary. Our experiments show that Aidfuzzer outperforms the state-of-the-art works in coverage and vulnerability detection. Our experiments found eight new vulnerabilities, and five CVEs were assigned.

3. **TEE Design.** Existing application-based TEE schemes such as SGX do not provide full backward compatibility, which means developers are required to design and implement the new application from scratch. Virtual machine-based TEE schemes such as CCA contain large code bases that expose more attack surfaces. In this thesis, we propose VirTEE, a full backward-compatible TEE that utilizes a RISC-V hypervisor extension and prior hardware memory isolation work to address the existing TEE shortcomings. VirTEE puts a hypervisor shim in the TEE, which exposes necessary TEE functionalities such as attestation and transparent, secure IO to the virtual machine so that an unmodified operating system can run directly in it. In the meantime, we keep the hypervisor shim as small as possible, making it less vulnerable to memory corruption vulnerabilities. In our experiments, VirTEE achieves comparable performance with the existing virtual machine-based TEE scheme.

The three targets all choose the memory-unsafe programming language C. Our analysis reveals that nowadays, memory corruption vulnerability is still a main threat to low-level software security. When designing and implementing low-level software, developers are supposed to pay more attention to it.

# 1.4 Thesis Roadmap

In this thesis, we present the overall high-level technical background in Chapter 2. In Chapter 3 4 5, we introduce our memory safety analysis details against the three targets. Note that the detailed technical background for each specific target is included in the specific chapter for clearance. In chapter 6, we present the related works about low-level memory safety analysis and the security mechanism that takes advantage of hardware features. In Chapter 7, we conclude the thesis and propose our future works.

# Technical Background

In this chapter, we present the hardware features provided by the processors that are closely related to the works in this thesis. In particular, the processor features TEE, hypervisor, Intel PT, Intel VT-x, and secure boot are introduced. Embedded system basic processor mechanisms such as interrupt and Memory-mapped I/O (MMIO) are related to the embedded firmware fuzzing and thus also included in the chapter. Further, the type, causes, and consequences of memory corruption vulnerability are demonstrated. Finally, a technique used to detect software memory corruption called fuzz testing (fuzzing) is presented.

## 2.1 Hardware Features

In this section, we introduce hardware features provided by the processors. Note that we only illustrate the general concepts of the feature. The specific feature details are presented in each target analysis chapter.

#### 2.1.1 Trusted Execution Environment

A Trusted Execution Environment (TEE) is a secure region of a processor that ensures sensitive data and operations remain protected from unauthorized access, even if the rest of the system is compromised. Unlike traditional computing environments where the entire OS and applications share the same memory and execution resources, TEEs segregate secure operations into separate environments. This segregation protects sensitive operations from privileged software like the OS and hypervisor. TEE operates as an isolated execution area, providing confidentiality, integrity, and authentication for critical code and data. The processor vendors propose such a feature to address the threat model where the end-user application runs in an untrusted environment such as a cloud server. TEE guarantees that the end-user data is protected against a malicious attacker with the highest privilege who has full control over the system. The key characters [54] of TEE are:

- **Isolation.** TEE ensures that operations inside the TEE are separate from the rest of the system.

- Confidentiality. Prevents unauthorized access to data within the TEE, even with the highest privilege.

- Integrity. TEE ensures the correctness and protection of both code and data during execution, which means memory-write from non-TEE is automatically discarded by the processor.

There are two types of TEE design schemes: application-based TEE and virtual machine-based TEE.

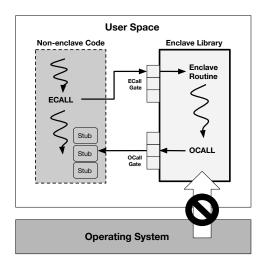

Application-Based TEE. A typical application-based TEE example is Intel SGX [103]. The secure region in TEE is called the enclave. Developers wrap the code that needs to run in the trusted environment as a library. The whole SGX application runs as a single process. As shown in Figure 2.1, the enclave library runs in enclave

Figure 2.1: SGX design overview

memory, which is located in the user space. Compared with the conventional processor memory access permission that privileged OS can read and write any physical memory, the enclave memory is only accessible to the enclave code. Naturally, the processor does not allow a direct jump from the non-enclave to the enclave and vice versa. Especially, SGX provides a set of instructions such as *EENTER* and *EEXIT* to perform the controlled context switch between the two regions.

Similar to system calls, to use the functionalities provided by the enclave library, non-enclave code performs a special context switch from non-enclave to enclave (i.e., ECALL in Figure 2.1). The transition is confined and checked by the processor. Only when the target address is a valid entry located in the enclave metadata the transition permission will be granted.

The SGX design prevents access from the privileged OS to the enclave. On the other hand, the enclave code cannot directly invoke the system calls. To have access to OS functionalities, the enclave code has to first transit to the non-enclave (i.e., OCALL in Figure 2.1). Some predefined functions that are regarded as stubs in the non-enclave memory are responsible for forwarding requests to the OS. When the system calls return, the enclave code reads the return value and buffers from the stubs to the enclave memory.

Application-based TEE is lightweight but does not provide compatibility with the existing libraries. Developers start from scratch with the SDK provided by Intel. However, it has been proven that application-based TEE cannot be accepted by the industry.

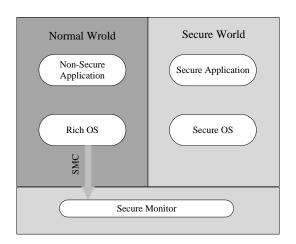

Virtual Machine-Based TEE. Putting the whole virtual machine in the TEE eliminates the manual effort of developing the TEE applications from scratch, and it has been a popular TEE scheme nowadays. Intel TDX [104], ARM Trust Zone [5], and AMD SEV [134] are well-known virtual machine-based schemes. As shown in Figure 2.2, ARM TrustZone [5, 156] split the system into two parts: a normal world and a secure world. A

Figure 2.2: TrustZone on ARM Cortex-A

rich OS serves the normal world, while a lightweight, secure OS serves the secure world. The two worlds communicate via a secure monitor, which acts like a context switch. Normal world software can only use the services provided by the secure world by using a hardware interrupt, an external abort signal, or the software instruction SMC. The hardware interrupts and aborts are asynchronous and only support a full-world switch, while SMC also supports message passing without a complete changeover. Secure world software can use these methods or write directly to the CPSR. Secure monitor code executes with interrupts disabled due to volatility concerns.

Virtual machine-based TEE provides backward compatibility. Developers only need to focus on the TEE application logic implementation instead of worrying about the library dependency. It has proven to be the TEE scheme accepted by most processor vendors and communities.

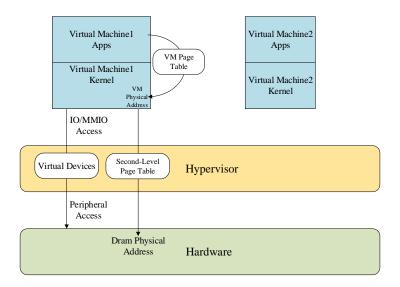

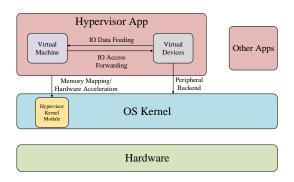

### 2.1.2 Hypervisor

A hypervisor (also known as a Virtual Machine Monitor or VMM) is a software or hardware layer that creates and manages virtual machines (VMs) by abstracting the underlying physical hardware. It enables multiple operating systems to run concurrently on a single physical machine, sharing resources like CPU, memory, storage, and peripherals. Hypervisors are a critical component in virtualization technology and play a significant role in cloud computing, development environments, and server consolidation. There are two types of hypervisors. Type one 2.3 hypervisors such as Microsoft Hyper-V [149] and VMware ESXi [218] run directly on the hardware and manage guest operating systems. They directly manage the hardware resources and the communication between virtual machines. Type two 2.4 hypervisors such as VMware Workstation [217] and Oracle VirtualBox [159] run inside a booted operating system. They rely on the host OS to manage the hardware resources.

**Second Level Page Table.** The Second Level Page Table is a hardware-assisted memory virtualization feature used by hypervisors to manage guest virtual memory efficiently. In a virtualized environment, a guest operating system assumes it has

Figure 2.3: Type-1 hypervisor

direct access to the hardware memory. However, the hypervisor must manage the translation of the guest's memory access to the actual physical memory of the host machine. The second-level page table simplifies this process by adding another level of page tables, reducing the need for software-based translation. The guest's virtual address is translated into the guest's physical address via the guest page table, which is further translated into the host's physical address via the second-level page table. The translation process happens automatically in the memory management unit of the processor, making the translation overhead negligible. As reported by kAFL [183], with Intel-VTx that enables second-level page table acceleration, virtualized applications can achieve 45 times faster than QEMU software memory translation.

**Device Simulation.** Device simulation refers to the process of emulating or virtualizing hardware devices within a virtualized environment, allowing guest operating systems and applications to interact with virtual devices as if they were physical hardware. The hypervisor is responsible for simulating these devices and managing their interactions with the host system's actual hardware. The device access via the IO port or MMIO can be trapped into the hypervisor, which allows the hypervisor to intercept the peripheral-OS communication. A virtual machine running in a para-virtualized environment is aware of the hypervisor and communicates with it via low overhead virtio devices.

#### 2.1.3 Intel PT and VT-x

Intel PT [102] and Intel VT-x [106] technologies are two Intel processor features that enable program trace and hypervisor.

Intel PT. Intel PT (Processor Trace) is a hardware feature for fine-grained tracing of program execution. It enables developers and security researchers to capture detailed information about how software executes on the CPU. Intel PT is widely used in

Figure 2.4: Type-2 hypervisor

debugging, performance analysis, and reverse engineering. It can be used to capture control flow changes (e.g., branches, jumps, calls, and returns) in the program execution. Due to its low overhead and selective tracing mode, coverage feedback-driven fuzzing can benefit from this feature, which we will discuss later in the chapter.

Intel VT-x. Intel VT (Virtualization Technology) is a suite of hardware-assisted virtualization features that enable the efficient execution of virtual machines. It reduces the performance overhead of traditional software-only virtualization by offloading key tasks to the CPU. It can virtualize CPU, memory, IO, and interrupt resources. Intel processors provide *VMEXIT* and *VMETER* instructions to switch into and out of a virtual environment. KVM relies on this feature in an Intel processor to create a virtual machine environment.

### 2.1.4 BIOS and Secure Boot

BIOS (Basic Input/Output System) is firmware embedded in a computer's motherboard (usually in the SPI flash memory in an IBM-compatible computer) that initializes hardware during the booting process and provides runtime services for operating systems and applications. It is the first code executed when a PC is powered on and plays a key role in the startup sequence. The legacy BIOS does the Power-On Self Test (POST), initializes the hardware, invokes the bootloader, and then simply exits. Modern predecessor BIOS standard UEFI provides more features than legacy BIOS. After loading the bootloader, UEFI remains in the memory and provides runtime service to the bootloader and the operating system.

Secure boot [105] is a security feature implemented in UEFI firmware to ensure that only trusted software is loaded during the boot process. It protects against malicious software, such as rootkits or bootkits, that could compromise the system at startup. Secure boot functions as a chain of trust; the former component verifies the next one and decides whether or not to load the next component.

# 2.2 Embedded System

An embedded system is a specialized computing system designed to perform dedicated functions or tasks. Unlike general-purpose computers, embedded systems are optimized

for specific applications, often with strict constraints on performance, power consumption, and size. Real-Time Operating System (RTOS) is a kind of lightweight OS that usually contains a simplified task scheduler, peripheral access wrapper, and necessary standard library. RTOS is designed for embedded systems due to its small code base, which can fit into a small physical memory.

### 2.2.1 Interrupt

An interrupt is a mechanism in computing that temporarily halts the execution of the current program to address an event or request that requires immediate attention. Once the interrupt is handled, the system resumes the execution of the interrupted program. Interrupts are essential for responsive and efficient system behavior, allowing the processor to respond promptly to asynchronous events, such as hardware signals or software exceptions. In an embedded system, interrupts are handled in a way that minimizes latency while maintaining deterministic behavior.

### 2.2.2 Memory-Mapped I/O

In a reduced instruction set processor, peripherals are accessed by uniformed memory access called Memory-Mapped I/O (MMIO). In MMIO, hardware devices such as peripheral controllers are mapped into the same address space as the system's RAM. This allows the CPU to interact with hardware devices using standard memory access instructions. When a large amount of data needs to be transferred from peripherals to the DRAM, Direct Memory Access (DMA) is used. When configured, DMA allows peripherals to use the bus for data transferring without CPU interception.

# 2.3 Memory Corruption Vulnerability

Szekeres et al. [200] mentioned that memory corruption vulnerability has existed for over 30 years. Memory corruption vulnerability begins with a memory error. Depending on the type of the error, de-referencing an out-of-bound pointer is called spatial error, while de-referencing a dangling pointer is called temporal error. The naming methodology is straightforward. An out-of-bound pointer does not point to the intended location, while the dangling pointer once points to a valid memory however, it becomes invalid when de-referencing. A typical spatial error is stack overflow, by overwriting the return address of the current function hijacks the control flow execution. Use-after-free is a common temporal memory error, which usually refers to a heap memory being used after the memory is deallocated. Attackers exploit memory corruption vulnerabilities to change the intended behavior of the target.

### 2.3.1 Exploitation

The attacker's goal is to change the application's normal execution behavior. The main method to achieve their goal is to alter the application control flow but not confined to it. Shellcode. Shellcode is a sequence of machine instructions that is crafted to execute a specific payload on a target system, often as part of an exploit, giving attackers control of a compromised system. A typical shell code can be injected by the attack to the target application to swap a new shell process. In certain circumstances, shellcode might be detected by intrusion detection mechanisms, some interesting works [141] generate ASCII character shellcode, printable shellcode, or even English shellcode. However, modern shellcodes can perform a wide range of tasks beyond launching a shell, including downloading files, injecting processes, or escalating privileges. The crafting of shellcode depends on the specific platform and environment.

Code Reuse. Code reuse attacks exploit vulnerabilities in software to execute malicious actions by reusing existing code (called gadget) within the target application or system rather than injecting new code. These attacks circumvent security measures such as Data Execution Prevention (DEP), which marks certain memory regions as non-executable, preventing traditional code injection. Prominent examples of code reuse attacks include Return-to-Libc (ret2libc), Return-Oriented Programming (ROP) [169], and Jump-Oriented Programming (JOP) [24]. These techniques are widely used by attackers to compromise systems while evading detection and mitigation. Theoretically, the larger the code base is, the more gadgets the attacker could use to launch the attack.

Data Only Attack. When control flow hijacking is not possible, attackers can solely modify the application data and reuse the application logic to alter the application behavior. The attacker's goal can be achieved without modifying data that is explicitly related to control flow. For example, the attacker might exploit a buffer overwrite vulnerability to change an integer, which indicates the current user's permission to gain higher privilege than normal execution. Hu et al. proposed Data-Oriented Programming (DOP) [98] to construct expressive non-control data exploits for arbitrary x86 programs. They show that the attack can construct a Turning-complete attack in two out of nine real-world programs.

### 2.3.2 Mitigation

The security community has appealed to programmers to carefully consider the memory safety problems when coding. However, memory safety issues are still threatening the application execution. To enforce and eliminate the application memory safety. Several mitigation methods are proposed to prevent it from happening.

Canary. Canary protection is a security mechanism designed to detect and prevent stack-based buffer overflows. This technique is widely used in modern operating systems and compilers (e.g., GCC's Stack Smashing Protector) to protect programs from attacks that exploit stack memory to overwrite critical data such as return addresses or function pointers. A canary value is placed between the local variables and the control-sensitive data (e.g., return address, saved frame pointer) on the stack. This ensures that any overflow attempting to overwrite the return address must first modify the canary. Before a function returns, the program checks whether the canary's value has changed. If the canary is intact, the program continues execution normally otherwise, it terminates or takes predefined defensive actions.

**ASLR.** Address Space Layout Randomization (ASLR) is a security mechanism that

enhances program resilience against memory corruption attacks by randomizing the memory addresses of critical program components. By making the locations of the stack, heap, libraries, and other sections unpredictable, ASLR mitigates attacks that rely on a known address of the target code. Since the attacker needs to hijack the control flow of the target, ASLR makes the target address unpredictable, making the application crash immediately instead of behaving abnormally. Lu et al. proposed ASLR-Guard [133] to further augment the protection by separating the data and code region and decoding the pointer when they are translated to the other.

**NX.** NX (No-eXecute), also known as Data Execution Prevention (DEP), is a hardware and software-based security feature designed to prevent the execution of malicious code (intended to be data such as shell code) in non-executable memory regions (usually by putting the data in non-executable pages). By enforcing the separation of code and data, NX protection mitigates many types of memory corruption attacks, including stack-based buffer overflows and heap exploitation.

CFI. Control Flow Integrity (CFI) ensures that the program's execution adheres to a predefined, legitimate control flow. CFI effectively prevents attackers from redirecting execution to malicious or unintended code. There are many prior CFI works published in the last decades [32, 232, 114]. As claimed by Becker et al. [19], CFI has not been deployed by the majority of the binaries, making them suffer from control flow hijacking. However, most CFI rely on static compile-time data to guide the run-time control flow destination address check. It makes the CFI policy somewhat unsound and can be bypassed by carefully crafted control flow hijacking.

# 2.4 Fuzz Testing

Fuzz testing, or *fuzzing*, is a technique used to discover bugs in the software. The original methodology is straightforward: feed random inputs, execute the target software as an oracle, and get a report from the running result. If a crash is reported, a potential vulnerability might exist. Nowadays, fuzzing has evolved several times from black-box fuzzing (also called *dumb mode*) to the current feedback-driven fuzzing. As a popular research topic these years, various parts of fuzzing, such as input scheduling, feedback, and seed generation, have been discussed and solved.

### 2.4.1 Black-Box Fuzzing

During the early ages of fuzzing, fuzzing solely interacts with the target application via the command line, file, and APIs. The workflow is simple: generate the initial inputs, mutate the input, feed the input to the target application and run the target, wait for the target to exit and collect the exit result, and check if the input can cause a crash to the target. Without additional information, the method is low-efficient however, it can still detect vulnerabilities at that time.

## 2.4.2 Code Coverage Feedback

In 2013, AFL [147] was invented by Zalewski, which signifies a milestone in fuzzing research. The key insight of AFL is that the explored code of an input can be used as a

metric to drive the fuzzing process. When an input can trigger a path that has not been discovered previously by other inputs, it is regarded as an *interesting* input and saved in the *corpus*. The inputs in the corpus will be used as seeds to be mutated in the following rounds of fuzzing. The methodology is straightforward: a vulnerability can only be detected when the vulnerable code is executed, that said, the more code the fuzzing can explore, the more vulnerabilities a fuzzer can detect. Saving the interesting inputs in the corpus breaks the long-distance and hard-to-reach program execution point into several short-distance and easy-to-reach segments. After that, based on path coverage feedback, many works regarding seed generation [190], mutation strategies [108], input schedules [25], value predicting [9], exploration navigation [8], and a mix of them [80] were proposed.

# 2.4.3 Feedbacks Beyond Code Coverage

Researchers found that path coverage feedback does not always reflect how interesting the input is. For example, when fuzzing a protocol that implements a finite state machine, the state of the protocol logic is more important than how many paths an input can cover. More feedback such as state coverage [243, 224, 167, 241, 10] and data coverage [225, 78] are proposed to reflect the diversity of the quality of the input.

# 2.4.4 Fuzzing Modularization

Fioraldi et al. [81] proposed LibAFL, a modularized fuzzing framework that can be customized by the developers, which we believe pinpoints the development future of fuzzing. They split a fuzzer into several interconnected components: Observer, Executor, Feedback, Input, Corpus, Mutator, Generator, Stage. An observer provides the execution information, such as how many edges an input can trigger. An executor is responsible for launching the target. The executor can be as simple as a function as well as a complex enough process such as a fork server. The fuzzer treats it like an unseparated oracle to simply run the target once. The feedback determines if an input is interesting or not. Once the input is determined interesting, it is added to the corpus. Note that several feedbacks can be assigned, and the results are unified to determine the result. Feedback is usually bound with an observer, however, it is not always. For example, edge coverage feedback needs the coverage observer to provide the edge information during the execution, however, to determine if the input is interesting, the feedback also needs to maintain the previously explored paths. An input is input fed to the target application. The format of the input can be a sequence of bytes or a grammar-based string. A corpus is a collection of inputs bound with meta-data, which can be stored in memory, disk, or disk and also cached in memory. The mutator mutates one input according to its format. A bytes stream input may involve mutation strategies such as bit-flit and byte-shuffle operations. The generator generates initial inputs for fuzzing. However, researchers commonly choose to provide their initial seeds, which gain better performance. The stage reflects a single operation on an input selected from the corpus. For example, a mutational stage mutates an input from a corpus, executes the target with the mutated input several times, and checks if the input is interesting. The modularization models the fuzzing process into several components that allow the user

to customize. It clearly defines what each component should perform and provides a universal interface to extend them. We believe LibAFL will be accepted and extended by the community, and a more robust framework will come out soon.

# 2.4.5 Domain Specific Fuzzing

LibAFL defines a general model for fuzzing despite their detailed implementation. However, to overcome the specific problems when fuzzing the applications that are hard to harness, tailored methods are required. For example, when fuzzing the Linux kernel, even with powerful computing resources and carefully manually crafted system call specifications [89], it is still hard to detect the hard-to-trigger race condition vulnerabilities. Therefore, prior work such as ExpRace [123] proposed interrupt-triggering to tackle this problem. When fuzzing closed-source applications, it is hard to instrument the binary to collect the path coverage. Static binary rewritings such as Retrowrite [66] and MULTIVERSE [16] either work in limited environments or are not sound enough. Dynamical run-time binary writing works such as Intel Pin [151] and DynamoRIO [68] can accurately instrument the target. However, they are not coherently designed for fuzzing and, therefore, incur high-performance overhead. Besides, they are not able to fuzz system-level applications such as operating systems and hypervisor. Embedded system software designed to be executed in low-powered MCUs is not fuzzable in a native high-performance native environment. LibAFL QEMU [140] and Afl Qemu-mode were proposed to run the target in a simulated environment to solve these problems. Thanks to the Qemu instruction translation mechanism, the target instructions are translated into intermediate code and further translated into native instructions. This allows easy instrumentation during the translation process and gains a high performance by maintaining the translation result cached in memory. In addition to instruction translation, Qemu provides detailed introspection of the running target, allowing reading and modifying any internal state of the target, such as interrupt, physical memory, and peripheral register values.

# 3

Bootloader: Comprehensive Attack Surfaces Analysis and Generic Fuzzing Framework

# 3.1 Overview

As mentioned before, low-level software is executed in the early stage of system booting or requires high hardware privilege to run. A bootloader is a program executed during the early stage of system booting. Its purpose is to initialize a preparatory environment for loading the operating system (OS) from a storage device into memory. After powering on a computer, the firmware is loaded first and performs the necessary power-on self-test (POST). Once the firmware completes its tasks, it hands control to the next component—the bootloader. The bootloader then continues setting up the remaining environment, including the CPU, memory, and peripheral devices, for the next component, usually the OS. Obviously, the bootloader is a typical low-level software that plays an important role during the boot process, as it connects two crucial components: the firmware and the operating system.

Modern computers commonly adopt a security mechanism called secure boot [105] to prevent malicious or modified software from being loaded. This mechanism functions as a chain of trust: each component checks and verifies the next component to ensure it is signed by a valid digital signature. If a component fails this check, the next layer is not loaded. During the booting process, the bootloader is responsible for examining and validating the OS. A malicious or tampered OS can break this security guarantee and make the system vulnerable, hence secure boot plays a central role when building trustworthy systems. As a key part of the secure boot chain, the bootloader is responsible for verifying the operating system, loading its image into memory, and launching it. Therefore, the bootloader must be designed and implemented securely. However, bootloaders have increasingly provided more features and functionalities for end users. As the code base grows, bootloaders inevitably expose more attack surfaces. For instance, the popular Linux bootloader GRUB [87] supports more than 20 types of file systems. Additionally, it allows users to customize the background image, font, and keyboard layout, as well as downloading files from HTTP or TFTP servers. Other bootloaders, such as Das U-Boot [63] and barebox [15], face the same situation. The larger the code base becomes, the more vulnerable it gets.

In recent years, vulnerabilities, particularly memory safety violations, have been discovered in various bootloaders. Some of these vulnerabilities can lead to denial of service or even bypass secure boot protections. Roee [93] discovered a variety of vulnerabilities in Android device bootloaders. Due to the limited physical access to mobile devices, communication with the device is confined to fast boot commands [2]. However, the command line parsing logic has caused more than ten vulnerabilities in Android bootloaders. While physically accessing a Personal Computer (PC), such as plugging in an extra USB stick, is easier than accessing mobile devices, PC bootloaders face more attack surfaces. Researchers recently reported secure boot bypass vulnerabilities in bootloaders affecting hundreds of consumer and enterprise-grade x86 and ARM models from various vendors, including Intel, Acer, and Lenovo [62]. The vulnerability originates from an image-parsing library, giving the attacker full control over the system. Similarly researchers reported an HTTP implementation vulnerability [208] in shim [173]: an attacker can exploit an out-of-bound memory write to compromise the entire system. Other bootloader vulnerabilities, such as BootHole [69], CVE-2022-30790,

CVE-2022-30552, and CVE-2023-20064, continue to threaten system security.

Although bootloaders for desktop and server computers play a security-sensitive role, a comprehensive and systematic memory safety analysis of them is still missing. Existing studies either do not address such bootloaders or only focus on a single attack vector. For example, BootStomp [174] and Roee [93] have only analyzed bootloaders for mobile devices, with a specific focus: BootStomp analyzed storage data controlled by the attacker that could compromise the bootloader, while Roee focused exclusively on command line inputs. Although bootloaders for desktop and server computers expose more attack surfaces compared to bootloaders for mobile devices, they have been less scrutinized so far. Axtens [60] and Starke [157] have proposed fuzzing techniques for GRUB [87] and Das U-Boot [63]. However, their analysis was limited to command-line parsing logic. The attack surfaces of bootloaders go far beyond command-line parsing.

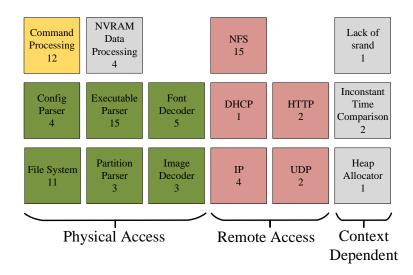

In this thesis, we perform the first comprehensive and systematic memory safety analysis of bootloaders and focus on the various attack surfaces that an attacker can exploit to compromise them. We start with a survey of previous bootloader vulnerabilities, which shows that attacks can primarily originate from peripheral inputs. Without the support of a rich OS environment, bootloaders must implement their standalone infrastructures, including drivers, task schedulers, timers, network protocol stacks, and more. For example, the bootloader must perform storage device reads, partition detection, file system parsing, file handler management, and file parsing to support file parsing. Since the storage data can be controlled by attackers, each layer represents a potential point of attack. Our analysis identified three types of peripheral inputs with the most attack surfaces: storage, network, and console.

**Storage.** To allow users to boot from different storage devices and file systems and to support other custom features, bootloaders implement a whole stack of file operations, including block device drivers, file system operations, and different types of file parsers. The implementation logic at each level is complex and error-prone. An attacker can easily compromise the bootloader by inserting a malicious storage device, such as a USB flash drive.

**Network.** To support booting over the network, such as PXE boot, bootloaders implement a complete network operations stack, including network controller drivers, the TCP/IP protocol, and application layer protocols. Some bootloaders even allow users to test the network status by sending ICMP packets. An attacker can hijack and manipulate network traffic or corrupt the server to send malicious packets to the bootloader. These network packets are processed by each layer of the network protocol stack, again increasing the attack surface.

Console. Some bootloaders provide users with an interactive interface, such as a command line console. An attacker who has physical access to the bootloader can exploit console parsing vulnerabilities by entering malicious command line strings into the console.

In addition to these three main types of peripherals, bootloaders also support other peripherals, including LED lights, power adapters, and video controllers. However, these peripherals usually do not have complex high-level parsing logic and provide less attacker-controllable data compared to the three main types discussed above.

To address the security challenges of bootloaders identified in our analysis, we

developed an automated approach to test them for potential vulnerabilities. More specifically, we develop a fuzzing framework for bootloaders, building on the proven effectiveness of fuzzing in detecting memory corruption vulnerabilities. Unfortunately, no existing solutions can be directly applied to bootloader fuzzing and we found that two main challenges need to be solved:

- Bootloaders run in a bare metal environment, which means that simple fuzzing frameworks like AFL [147] libFuzzer [132] cannot be directly deployed. Moreover, existing sanitizers cannot be used due to compatibility issues. Previous work [157] which compiles the bootloader into a native application indicates that crashes cannot be reproduced in the real bootloader because of environmental inconsistencies. Therefore, it is necessary to fuzz the bootloader in a real environment.

- In contrast to common user applications, bootloaders offer numerous attack surfaces. Fuzzing some of these interfaces requires dual operations. For example, when fuzzing a file system, file operations are required to trigger the parsing of the file system, while the fuzz input must be fed by intercepting the storage device data access.

To address these challenges, we simulate a virtual machine (VM) running in a hypervisor to create a real environment for the bootloader. Using a consistent operating environment helps to reduce false positives. We assume that the bootloader source code is available. Based on this, we designed a custom heap sanitizer specifically targeting bootloaders to detect heap overflow vulnerabilities. In addition, the observation that the malicious input origins are limited allows us to identify the universal interfaces and operations to intercept peripheral access and trigger device data processing. With the help of the simulated environment, the customized heap sanitizer, and the test harnesses, we can effectively fuzz the most important attack surfaces of bootloaders.