# **Traversing large graphs in realistic settings**

# Deepak Ajwani

Max-Planck-Institut für Informatik Saarbrücken, Germany

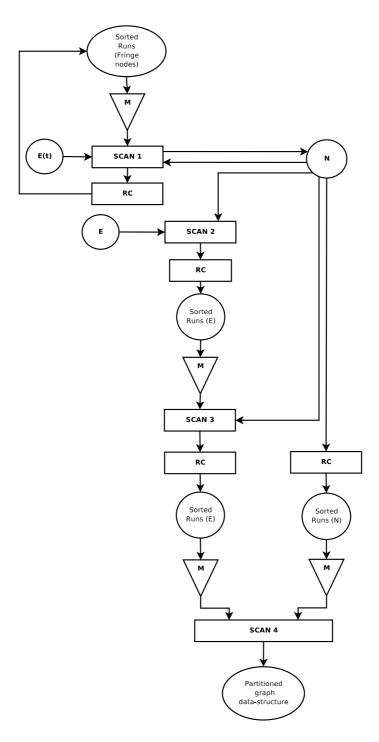

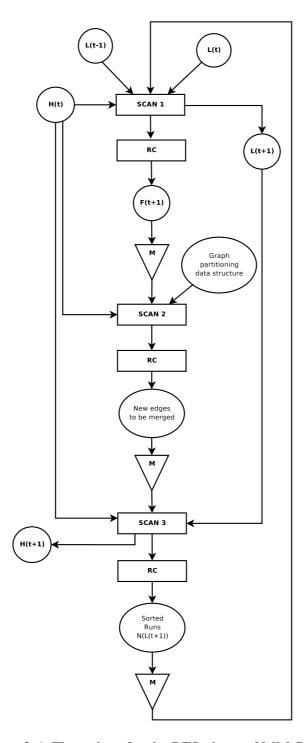

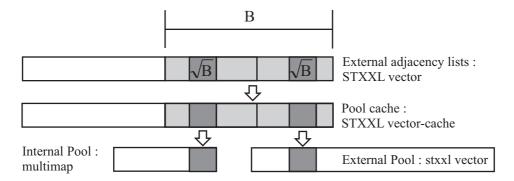

Dissertation zur Erlangung des Grades Doktor der Ingenieurwissenschaften(Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten I der Universität des Saarlandes

#### **Betreuender Hochschullehrer – Supervisor**

Prof. Dr. h. c. Kurt Mehlhorn, Max-Planck-Institut für Informatik, Saarbrücken, Germany

#### **Gutachter – Reviewers**

Prof. Dr.-Ing. Ulrich Meyer, Institut für Informatik, Goethe-Universität, Frankfurt am Main, Germany

Gerth Brodal, Ph.D., Department of Computer Science, Aarhus University, Århus, Denmark

#### Vorsitzender des Prüfungsausschusses - Chairman of the Examination Board

Prof. Dr. Raimund Seidel, Universität des Saarlandes, Saarbrücken, Germany

#### Beisitzer – Observer

Dr. Stefan Canzar, Max-Planck-Institut für Informatik, Saarbrücken, Germany

#### Dekan – Dean

Prof. Dr. Joachim Weickert, Universität des Saarlandes, Saarbrücken, Germany

#### Datum des Kolloquiums - Date of Defense

21. Dezember 2008 – December 21st, 2008

Deepak Ajwani MADALGO – Center for Massive Data Algorithmics, IT-parken, Åbogade 34, DK-8200 Århus N, Denmark ajwani@madalgo.au.dk

# **Abstract**

The notion of graph traversal is of fundamental importance to solving many computational problems. In many modern applications involving graph traversal such as those arising in the domain of social networks, Internet based services, fraud detection in telephone calls etc., the underlying graph is very large and dynamically evolving. This thesis deals with the design and engineering of traversal algorithms for such graphs.

We engineer various I/O-efficient Breadth First Search (BFS) algorithms for massive sparse undirected graphs. Our pipelined implementations with low constant factors, together with some heuristics preserving the worst-case guarantees makes BFS viable on massive graphs. We perform an extensive set of experiments to study the effect of various graph properties such as diameter, initial disk layouts, tuning parameters, disk parallelism, cache-obliviousness etc. on the relative performance of these algorithms.

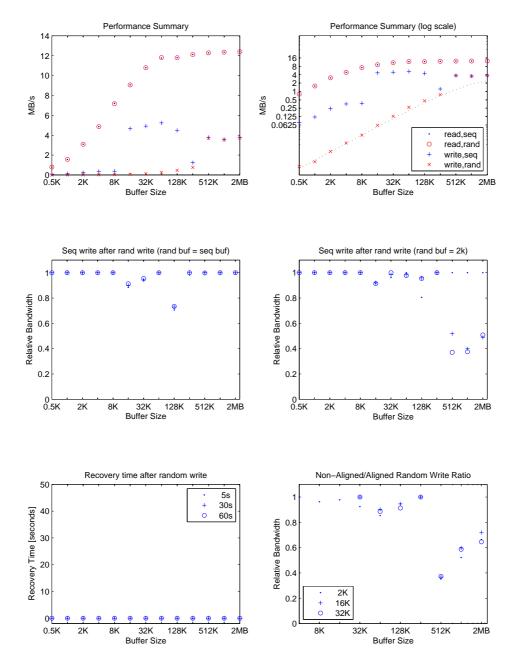

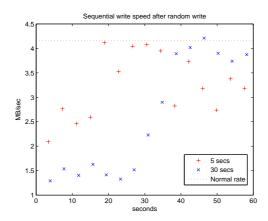

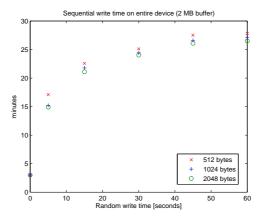

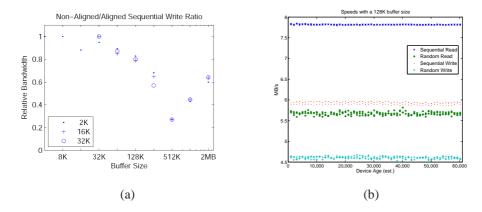

We characterize the performance of NAND flash based storage devices, including many solid state disks. We show that despite the similarities between flash memory and RAM (fast random reads) and between flash disk and hard disk (both are block based devices), the algorithms designed in the RAM model or the external memory model do not realize the full potential of the flash memory devices. We also analyze the effect of misalignments, aging, past I/O patterns, etc. on the performance obtained on these devices. We also consider I/O-efficient BFS algorithms for the case when a hard disk and a solid state disk are used together.

We present a simple algorithm which maintains the topological order of a directed acyclic graph with n nodes under an online edge insertion sequence in  $O(n^{2.75})$  time, independent of the number m of edges inserted. For dense DAGs, this is an improvement over the previous best result of  $O(\min\{m^{\frac{3}{2}}\log n, m^{\frac{3}{2}} + n^2\log n\})$ . While our analysis holds only for the incremental setting, our algorithm itself is fully dynamic.

ii Abstract

We also present the first average-case analysis of online topological ordering algorithms. We prove an expected runtime of  $O(n^2 \operatorname{polylog}(n))$  under insertion of the edges of a complete DAG in a random order for various incremental topological ordering algorithms.

# Kurzfassung

Die Traversierung von Graphen ist von fundamentaler Bedeutung für das Lösen vieler Berechnungsprobleme. Moderne Anwendungen, die auf Graphtraversierung beruhen, findet man unter anderem in sozialen Netzwerken, internetbasierten Dienstleistungen, Betrugserkennung bei Telefonanrufen. In vielen dieser Anwendungen ist der zugrunde liegende Graph sehr gross und ändert sich kontinuierlich.

Wir entwickeln mehrere I/O-effiziente Breitensuch-Algorithmen für massive, dünnbesiedelte, ungerichtete Graphen. Im Zusammenspiel mit Heuristiken zur Einhaltung von Worst-Case-Garantien, ermöglichen unsere pipeline-basierten Implementierungen die Praktikabilität von Breitensuche auf massiven Graphen. Wir führen eine Vielfalt an Experimente durch, um die Wirkung unterschiedlicher Grapheigenschaften zu untersuchen, wie z.B. Graph-Durchmesser, anfängliche Belegung der Festplatte, Tuning-Parameter, Plattenparallelismus.

Wir charakterisieren die Leistung von NAND-Flash basierten Speichermedien, einschliesslich vieler solid-state Disks. Wir zeigen, dass trotz der Ähnlichkeiten von Flash-Speicher und RAM (schnelle wahlfreie Lese-Zugriffe) und von Flash-Platten und Festplatten (beide sind blockbasiert) Algorithmen, die für das RAM-Modell oder das Externspeicher-Modell entworfenen wurden, nicht das volle Potential der Flash-Speicher-Medien ausschöpfen. Zusätzlich analysieren wir die Wirkung von Ausrichtungsfehlern, Alterung, vorausgehenden I/O-Mustern, usw., auf die Leistung dieser Medien. Wir berücksichtigen auch I/O-effiziente Breitensuch-Algorithmen für die gleichzeitige Nutzung von Festplatten und solid-state Disks.

Wir stellen einen einfachen Algorithmus vor, der beim Online-Einfügen von Kanten die topologische Ordnung von einem gerichteten, azyklischen Graphen (DAG) mit n Knoten beibehält. Dieser Algorithmus hat eine Laufzeitkomplexität von  $O(n^{2.75})$  unabhängig von der Anzahl m der eingefügten Kanten. Für dichte DAGs ist dies eine Verbesserung des besten, vorherigen Ergebnisses von  $O(\min\{m^{\frac{3}{2}}\log n, m^{\frac{3}{2}} + n^2\log n\})$ . Während die Analyse nur im inkrementellen Szenario gütlig ist,

iv Kurzfassung

ist unser Algorithmus völlständig dynamisch.

Ferner stellen wir die erste Average-Case-Analyse von Online-Algorithmen zur Unterhaltung einer topologischen Ordnung vor. Für mehrere inkrementelle Algorithmen, welche die Kanten eines kompletten DAGs in zufälliger Reihenfolge einfügen, beweisen wir eine erwartete Laufzeit von  $O(n^2 \text{ polylog}(n))$ .

# **Acknowledgements**

First of all, I would like to thank my two supervisors Kurt Mehlhorn and Ulrich Meyer for their generous support. In particular, I would like to thank Uli for his guidance, not only in scientific affairs, but also in practical matters of everyday life. At the same time, he gave me considerable scientific freedom to work on many different topics at the same time, thereby providing me ample opportunities to develop my own ideas and grow as an independent researcher. He has been very patient with me, as the engineering projects in this dissertation took much longer than expected.

I would also like to thank my co-authors Saurabh Ray, Roman Dementiev, Tobias Friedrich, Khaled Elbassioni, Hans Raj Tiwary, Sathish Govindarajan, Vitaly Osipov and Raimund Seidel. I learnt a lot while working with them. I am also grateful to Norbert Zeh for sharing valuable insights and many helpful discussions. Thanks are also due to Andreas Beckmann for his great help with organizing and debugging the external memory implementations.

I am also grateful to the members of my thesis examination committee who carefully read this thesis and raised many interesting questions during my defense.

My friends Shirley, Sky, Imran, Rali, Joisy and Chris made the life in Saar-bruecken so much fun. I always looked forward to having discussions with the lunch-group of the Databases and Information Retrieval group, in particular Fabian, Gjergji, Julia, Gerard and Mouna.

I would also like to acknowledge the International Max-Planck Research School (IMPRS), Deutsche Forschungsgemeinschaft (DFG) and Max-Planck Society for their financial support in the past years. MPII has been an incredibly nice place to work. Its transparent building and the beautiful nature surrounding it add to its charms. The bureacracy here is almost hidden – the ease of procuring new hardware and getting it installed is truly amazing.

I am indebted to my parents, who made sure that I get the best possible education and let me pursue my career abroad.

And last but not the least, I would like to thank my wife Georgiana Ifrim for her unflinching love through the thick and thin. She had been encouraging and understanding, even as I had been mentally immersed in my work.

# **Contents**

| 1 | Intro                                    | oduction                                                   | 1  |  |  |  |

|---|------------------------------------------|------------------------------------------------------------|----|--|--|--|

|   | 1.1                                      | Large graphs                                               | 2  |  |  |  |

|   | 1.2                                      | Realistic setting for traversing large graphs              | 5  |  |  |  |

|   | 1.3                                      | Our contribution                                           | 7  |  |  |  |

|   | 1.4                                      | Organization of the thesis                                 | 9  |  |  |  |

| 2 | Basic tools and techniques               |                                                            |    |  |  |  |

|   | 2.1                                      | Preliminary definitions                                    | 11 |  |  |  |

|   | 2.2                                      | Basic probability theory                                   | 14 |  |  |  |

|   | 2.3                                      | Random Graph Model                                         | 15 |  |  |  |

|   | 2.4                                      | Computation models capturing memory hierarchies            | 17 |  |  |  |

|   | 2.5                                      | Basic tools for designing external memory graph traversal  |    |  |  |  |

|   |                                          | algorithms                                                 | 24 |  |  |  |

|   | 2.6                                      | Tools and techniques for engineering external memory graph |    |  |  |  |

|   |                                          | traversal algorithms                                       | 29 |  |  |  |

| 3 | Breadth first search on massive graphs 3 |                                                            |    |  |  |  |

|   | 3.1                                      | Related prior work                                         | 32 |  |  |  |

|   | 3.2                                      | Basic building blocks                                      | 35 |  |  |  |

|   | 3.3                                      | Algorithms                                                 | 40 |  |  |  |

|   | 3.4                                      | Engineering MR_BFS                                         | 43 |  |  |  |

|   | 3.5                                      | Engineering MM_BFS_R                                       | 50 |  |  |  |

|   | 3.6                                      | Engineering MM_BFS_D                                       | 54 |  |  |  |

|   | 3.7                                      | A heuristic for maintaining the pool                       | 57 |  |  |  |

|   | 3.8                                      | External memory graph generator                            | 58 |  |  |  |

|   | 3.9                                      | External memory BFS decomposition verifier                 | 62 |  |  |  |

|   | 3.10                                     | BFS software package                                       | 63 |  |  |  |

|   | 3.11                                     | Results of our experimental study                          | 66 |  |  |  |

|   |                                          | Recent work related to EM BFS                              | 79 |  |  |  |

|   | 2 12                                     | D' '                                                       | 07 |  |  |  |

viii CONTENTS

| 4 | Chai | racterizing the performance of Flash memory storage devices       | 89  |

|---|------|-------------------------------------------------------------------|-----|

|   | 4.1  | Basics of flash memory disks                                      | 92  |

|   | 4.2  | Implications of flash devices for algorithm design                | 93  |

|   | 4.3  | Characterization of flash memory devices                          | 95  |

|   | 4.4  | Designing algorithms to exploit flash when used together with a   |     |

|   |      | hard disk                                                         | 110 |

|   | 4.5  | Conclusion                                                        | 112 |

| 5 | Dyna | amic topological ordering                                         | 113 |

|   | 5.1  | Related work                                                      | 115 |

|   | 5.2  | Algorithm                                                         | 117 |

|   | 5.3  | Correctness                                                       |     |

|   | 5.4  | Runtime                                                           | 123 |

|   | 5.5  | Bucket data structure                                             | 127 |

|   | 5.6  | Empirical comparison                                              | 128 |

|   | 5.7  | Towards a tighter analysis of our algorithm                       | 131 |

|   | 5.8  | Dynamic topological ordering in external memory                   | 135 |

|   | 5.9  | Average-case analysis of online topological ordering algorithms . | 137 |

|   | 5.10 | Recent advances in online topological ordering algorithms         | 145 |

|   | 5.11 | Conclusion                                                        | 146 |

# Chapter 1 Introduction

A theory must be tempered with reality.

— Jawaharlal Nehru

A graph is one of the most useful objects in discrete mathematics. It can be used to represent physical networks such as electrical circuits, roadways or organic molecules as well as less tangible interactions as might occur in ecosystems, sociological relationships, databases or in the flow of control in a computer program. It therefore comes as no surprise that graph theory finds applications in physics, chemistry, communication science, computer science, electrical and civil engineering, architecture, operational research, genetics, psychology, sociology, economics, anthropology and linguistics. The theory is also intimately related to many branches of mathematics, including group theory, matrix theory, numerical analysis, probability, topology, and combinatorics. In fact, graph theory serves as a mathematical model for any system involving a binary relation.

The notion of graph traversal is nearly as old and as important as the notion of a graph itself. One of the most celebrated results in graph traversal dates back to 1736 when Leonhard Euler solved the famous *Seven Bridges of Königsberg problem* using a graph traversal technique called Euler tour. A surprisingly large number of optimization problems from many different domains can be reduced to traversing graphs in a structured way.

Graph traversal algorithms have therefore received considerable attention in the computer science literature. Simple linear time algorithms have been developed for Breadth-First Search (BFS), Depth-First Search (DFS), computing connected and strongly connected components on directed graphs, and topological ordering of directed acyclic graphs [51]. Also, there exist near-linear time algorithms for computing Minimum Spanning Trees (MST) [45, 88, 128] of undirected graphs. Dijkstra's algorithm [61] with Fibonacci heaps [71] can solve the Single-Source Shortest-Paths (SSSP) [61, 71] problem on directed graphs with non-negative weights in  $O(m+n\log n)$ , where n is the number of nodes and m is the number of edges in the graph. For All-Pair Shortest-Paths (APSP), the naïve algorithm of computing SSSP from all nodes takes  $O(m \cdot n + n^2 \log n)$ . It has been improved to  $O(m \cdot n + n^2 \log \log n)$  [127] for sparse graphs and  $O(n^3/\log n)$  [44] for dense graphs.

# 1.1 Large graphs

In many applications involving graph traversal, the underlying graph is too big to fit in the internal memory of the computing device. Consider the following examples:

• The World Wide Web (WWW) can be looked upon as a massive graph where each web-page is a node and the hyperlink from one page to another is a directed edge between the nodes corresponding to those pages. As of August 2008, it is estimated that the indexed web contains at least 27 billion webpages [53].

Typical problems in the analysis (e.g., [35, 95]) of WWW graphs include computing the diameter of the graph, computing the diameter of the core of the graph, computing connected and strongly connected components and other structural properties such as computing the correct parameters for the power law modeling of WWW graphs. There has also been a lot of work on understanding the evolution of such graphs.

Computing Page rank [36] (the basis of the Google search engine) is considered to be a very important problem with respect to webgraphs, owing to its immense usage in search engines, classification and many other machine learning applications. A key challenge here is that since the webgraph is continuously evolving, recomputing Page rank every time there is a minor modification in the webgraph is considered to be "increasingly infeasible" [59].

Social networking websites such as Facebook, Orkut, MySpace, LinkedIn etc. also provide massive and continuously evolving graphs. The nodes here refer to the profiles of people and an edge refers to an acknowledgement of acquaintance between two people. Typical problems on these graphs are computing similarity based clustering to find communities of people.

- Citation graphs of scientific papers from specific domains, where nodes are the publications and a directed edge from one paper to the other reflects a citation is yet another such graph class. The main problem here is to understand the nature of scientific collaboration and identify communities.

- Automatic classification of data items, based on training samples, can be boosted by considering the neighborhood of data items in a graph structure [16]. This is particularly useful when the objects to be classified are images (in web-sites such as Flickr) or videos (in web-sites such as YouTube). The tags associated with these pictures and videos are hardly enough for their classification. The graph structure containing the likings and dislikings of different users provides important clues that can improve the classification accuracy significantly. Such graphs can often be quite huge. For example, the online photo sharing network Flickr that started in 2004 had more than two billion pictures as of November 2007 [70] and claims that three to five million photos are updated daily on its network.

- There have also been attempts (e.g., [98]) to improve the results of web search by using the implicit feedback obtained from query logs. The underlying assumption behind these approaches is that by clicking (or ignoring) the results provided by the search engines for a particular query, users mark the relevance of clicked (or ignored) pages with respect to their query. The graph here is huge as the set of nodes consists not only of the web-pages, but also of all the queries posted by users to the search engine. There is an edge between a node representing a query q and a node representing a web-page w if a user searches for the query q, the search engine shows him/her the web-page w as a result, and he/she clicks on it.

- Telephone call graphs: Telephone call graphs have the telephone numbers operated by a company as nodes and there is a directed edge between two nodes if and only if there has been a call from one to another in a certain time-frame. The call graphs managed by telecom companies like AT&T can be massive. Typical problems on telephone call graphs are fraud detection and searching for local communities (e.g., by detecting maximum cliques [1]).

- GIS terrain data: Remote sensing has made massive amounts of high resolution terrain data readily available. Terrain analysis is central to a range of important geographic information systems (GIS) applications concerned with the effects of topography. Typical problems in this domain involve flow routing and flow accumulation [22].

- Route planning on small PDA devices [76, 141]: The PDA devices used to compute the shortest/fastest routes have very small main memory. Although the street maps of even continents are only a few hundred MBs in size, they are too large to fit into the small main memory of these devices.

- State space search in Artificial Intelligence [64]: In many applications of model checking, the state space that needs to be searched is too big to fit in the main memory. In these graphs, the different configuration states are the nodes and the edge between two nodes represent the possibility of a transition from one state to another in the course of the protocol/algorithm being checked. Typical problems in this domain are reachability analysis (to find out if a protocol can ever enter into a wrong state) [84], cycle detection (to search for liveness properties) [63], or just finding some path to eventually reach a goal state (action planning).

- Semantic graphs (e.g., [99]), where the nodes represent entities and the edges represent relationship between two entities can also be quite huge. Typical problems in the analysis of semantic graphs include determining the nature of the relationship between nodes in the graph. Such queries can be answered by finding shortest paths or computing Steiner trees. Another key area of interest on semantic graphs is community analysis.

- Purchase graph from electronic commerce (e-commerce) companies such as the online book-shop Amazon is yet another example of massive and continuously evolving graph. Here, the bipartite graph consists of the products (such as books) and the buyers as the nodes and a purchase as an edge. There has been a lot of work in building a personalized recommendation system to show those products to users that they may also like. This is typically based on their past purchases. The key idea here is to identify other users whose purchasing behavior is similar and recommend the appropriately weighted sum of their other purchases.

- Frameworks for keyword querying of relational databases (e.g., [28]) may also involve traversing large graphs.

- Many problems arising in VLSI design, XML query processing, querying

ontology DAGs, Delaunay triangulation of meshes in computer graphics, visualization of biological networks such as protein-protein interactions, and molecular data mining also involve traversing large graphs.

While some solutions for these problems are based on sparse-matrix dense-vector multiplications, or approximating the solution using integer linear programming, a large number of solutions rely on traversing graphs. For example, a community detection algorithm by Newman and Girman [119] uses all-pair BFS as a subroutine to identify edges with high "betweenness", where betweenness is some measure that favors edges that lie between communities and disfavors those that lie inside communities. Removal of these edges reveal the inherent "natural" division of the network into groups.

# 1.2 Realistic setting for traversing large graphs

Since, the standard linear or near-linear time algorithms for graph traversal are also reasonably simple, it is tempting to use them directly in real applications involving large and massive graphs as well. Unfortunately, the real world offers many more challenges than the ones for which our simple algorithms are designed.

First and foremost, these algorithms are designed and analyzed in the von Neumann or RAM model of computation. This model assumes a unit cost access to any memory location. In reality, the computer architecture is far more complex. There is a sophisticated memory hierarchy (cf. Section 2.4.2) and the cost of data access depends on the level of memory where the data is currently residing. In particular, the cost of accessing the data from the disk is about a million times more than that of accessing it from the L1 cache.

As the storage requirements of the input graph reaches and exceeds the size of the main memory available, the running time of the simple linear or near-linear time algorithms deviates significantly from their predicted asymptotic performance in the RAM model. Furthermore, on massive graphs (with a billion or more edges), these algorithms are simply non-viable as they require many *months or years* for the requisite graph traversal. The main cause for such a poor performance of these algorithms on massive graphs is the number of I/Os (transfer of data from/to the external memory) they incur.

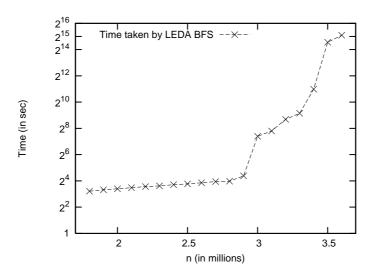

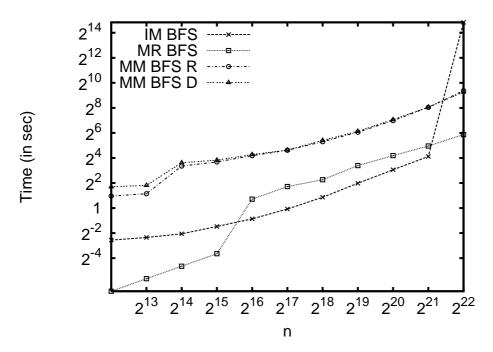

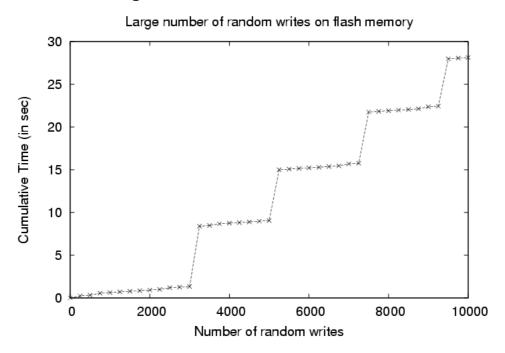

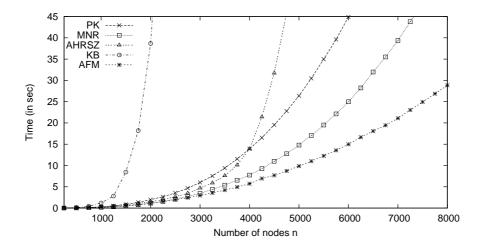

Figure 1.1 displays the results of experiments with the commonly used BFS rou-

Figure 1.1: Time (in seconds) required by BFS from the LEDA graph package on random graphs with m = 4n edges.

tine of the LEDA [107] graph package on random graph [66, 67] G(n,m) with m=4n. These experiments were done on a machine with Intel Xeon 2.0 GHz processor, 1 GB RAM and 2 GB swap space on a Seagate Baracuda hard-disk [142]. On random graphs with 3.6 million nodes (and 14.4 million edges), it takes around 10 *hours* as compared to just 10 *seconds* for graphs with 1.8 million nodes (and 7.2 million edges).

With the advent of solid state disks and other flash memory based storage mediums, the memory hierarchy is likely to become even more sophisticated as the read-write characteristics of these devices can be very different from the traditional hard disks. Since the storage devices significantly affect the practical performance of traversal algorithms when running on large graphs, we would like to exploit the I/O characteristics of these devices to design graph traversal algorithms that perform better in practice. For this, it is important to first properly characterize these disks.

Another important challenge when dealing with real world applications is that the input graphs are often dynamically changing. For instance, the World Wide Web graph, social networking graphs, purchase graphs, and scientific collaboration graphs are all continuously evolving. The telephone call graphs are also continuously changing. Even the street maps for route planning applications which may seem static most of the time are actually quite dynamic once the traffic jam and other road-block information is accounted in. The naïve way of recomputing all the information every time there is a minor modification in the original

1.3 Our contribution 7

graph is inefficient and for large and massive graphs, often impractical. Ideally, we would like to bound the amount of work needed to recompute the required traversal-related solution by a function of some measure of change done in the input graphs and the change in the output solution [132]. Since this is not always possible, our next best hope is to bound the required work in an amortized sense. In other words, while some updates may necessiate a lot of work, we would like to bound the sum of the time required for recomputing the solution over a sequence of graph updates.

While most of the algorithm design is done keeping the worst case complexity in mind, the worst case graphs for many of these algorithms are quite rare. Most application requirements are already met if an algorithm performs good on average.

In short, the simple graph traversal algorithms are often inappropriate for real applications involving massive graphs owing to the problems with the computation model, the noise and dynamicity of the input and the need for a different complexity measure (worst-case vs. average case).

Since most static algorithms analyzed for worst-case RAM complexity are impractical for massive graphs, one often relies on heuristics, pre-computations or exploiting special graph properties of underlying graphs. Such solutions are usually tailored for particular domains and are often application-specific. For each new application, one needs to design and implement different heuristics from the scratch. There is clearly a need for algorithms that will not only give nice theoretical guarantees for general graphs (without assuming any domain-specific knowledge), but also perform good in practise. This thesis focuses on the design, analysis and engineering of such algorithms.

# 1.3 Our contribution

The main contributions of this thesis are:

• We consider the problem of I/O-efficient Breadth-First Search (BFS) on massive sparse undirected graphs. We engineer the MR\_BFS algorithm by Munagala and Ranade [115] into a practical implementation with low constant factors in the I/O complexity. Our pipelined implementation based on the external memory library STXXL can use multiple disks to further alleviate the I/O bottleneck. With this implementation, we are able to compute the BFS level decomposition of a web-crawl based graph of around 130 million nodes and 1.4 billion edges in less than 3 hours, using 4 disks.

We also engineer the o(n)-I/O MM\_BFS algorithm [106] by Mehlhorn and Meyer. Our experiments suggest that while on small diameter graphs, MR\_BFS performs quite well, MM\_BFS performs significantly better on moderate to large diameter graphs. The usage of some heuristics further improves the running time of the faster variant of MM\_BFS, while at the same time preserving the worst-case asymptotic I/O-complexity of MM\_BFS. Demonstrating the viability of our BFS implementations [7, 9, 13] on various synthetic and real world benchmarks, we show that BFS level decompositions for large graphs (around a billion edges) can be computed on a cheap machine in a *few hours*, even if the underlying graph has large diameter.

We also present the design and engineering of simple I/O-efficient algorithms for generating large input graphs (of various graph classes) and a BFS decomposition verifier. As a part of our BFS implementations, we also look into the past engineering efforts on list ranking, Euler tour, minimum spanning forest and connected components, and adapt some of these implementations to the faster STXXL framework.

Furthermore, we compare the building blocks of our implementation with their corresponding cache-oblivious implementations and demonstrate that in the context of BFS on massive graphs, the cache-oblivious implementation is likely to be at least a factor of 4-5 slower than our implementation.

The key engineering ideas in our implementations also form the starting-point for implementing other I/O-efficient algorithms like Single-Source Shortest-Paths and Dynamic BFS. A significant chunk of our code is likely to be re-used for these implementations.

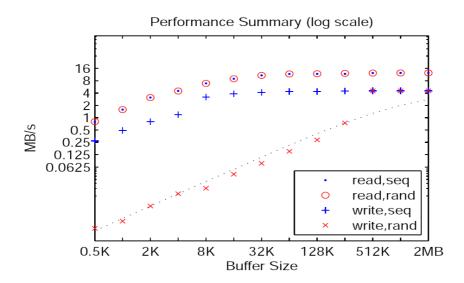

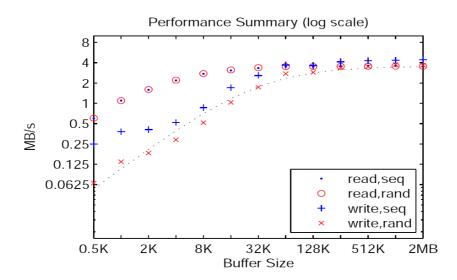

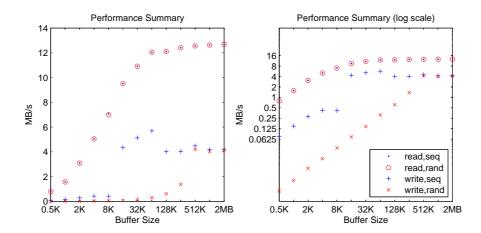

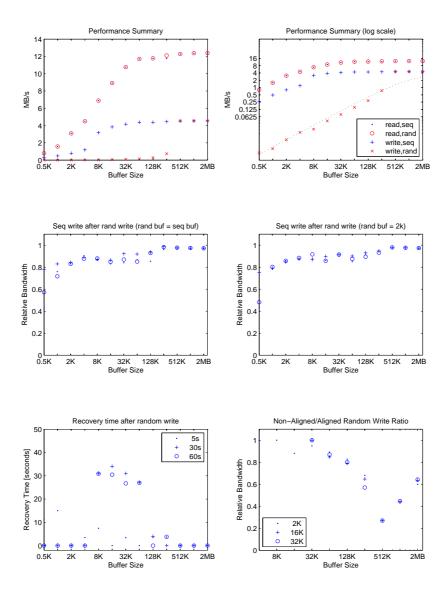

• Flash memory is fast becoming the dominant form of end-user storage in mobile computing. Since storage devices play a crucial role in the performance of (traversal) algorithms when the input (graph) data does not fit in the main memory, it is important to understand the I/O-characteristics of the storage devices to be able to predict the real running times of these algorithms. Such an understanding can also be exploited to design algorithms that are faster in practice. We characterize [10, 11] the performance of NAND flash based storage devices, including many solid state disks. We show that these devices have better random read performance than hard disks, but much worse random write performance. We also analyze the effect of misalignments, aging, past I/O patterns, etc. on the performance obtained on these devices. We show that despite the similarities between flash memory and RAM (fast random reads) and between flash disk and hard disk (both are block based devices), the algorithms designed in the

RAM model or the external memory model do not realize the full potential of the flash memory devices.

In the scenario when a solid state disk is used as an additional secondary storage rather than replacing the traditional hard disk, we engineer the I/O-efficient BFS implementation to exploit the comparative advantages of both the disks. We show that this is at least 25% faster than randomly striping the data on the two disks.

• We present a simple algorithm [8, 12] which maintains the topological order of a directed acyclic graph with n nodes under an online edge insertion sequence in  $O(n^{2.75})$  time, independent of the number m of edges inserted. For dense DAGs, this is an improvement over the previous best result of  $O(\min\{m^{\frac{3}{2}}\log n, m^{\frac{3}{2}} + n^2\log n\})$  by Katriel and Bodlaender [91]. While our analysis holds only for the incremental setting, our algorithm itself is fully dynamic.

We also provide an empirical comparison of our algorithm with other algorithms for dynamic topological sorting.

The externalization of our algorithm provides interesting new results for dynamic topological ordering in external memory.

We also present the first average-case analysis [5, 6] of online topological ordering algorithms. We prove an expected runtime of  $O(n^2 \operatorname{polylog}(n))$  under insertion of the edges of a complete DAG in a random order for the algorithms of Alpern et al. [15], Katriel and Bodlaender [91], and Pearce and Kelly [124].

# 1.4 Organization of the thesis

The rest of this thesis is organized as follows: Chapter 2 formally defines a graph and various notations used in the remaining chapters. It also shows the various computation models used to capture memory hierarchy and presents the basic tools and techniques for the design and engineering of I/O-efficient algorithms. Chapter 3 presents our work in engineering the I/O-efficient BFS algorithms. We also describe the related design and engineering of I/O-efficient algorithms for list ranking, Euler tour, directed breadth-first search, depth-first search, and topological ordering, and undirected connected components, minimum spanning forest, single-source shortest paths, dynamic BFS, and diameter approximation.

In Chapter 4, we show the characterization of flash memory devices including solid state disks. We also describe our efforts for tuning our I/O-efficient BFS algorithms to handle the case when the computing machine uses both the traditional hard disks as well as solid state disks for storage.

In Chapter 5, we present our  $O(n^{2.75})$  algorithm for online topological ordering. We also show some open problems that can help tighten the analysis of our algorithm. Also, we show how to externalize our algorithm to obtain interesting new results on dynamic topological ordering in external memory. Furthermore, we present our results for the average-case analysis of the online topological ordering. We show that the algorithms by Alpern et al. [15], Katriel and Bodlaender [91], and Pearce and Kelly [124] require an expected runtime of  $O(n^2 \cdot polylog(n))$  for maintaining the topological ordering, when edges of a complete DAG are inserted in a random order. We also briefly describe some recent advances in improving our bounds for this problem.

# **Chapter 2**

# **Basic tools and techniques**

Intelligence is the faculty of making artificial objects, especially tools to make tools.

— Henri Bergson

We start this chapter (Section 2.1) by giving the formal definitions and notations used in the remaining chapters. Section 2.2 provides some basic facts about probability theory and Section 2.3 presents some random graph models. Section 2.4 describes the real architecture and various computational models used to capture the memory hierarchy and Sections 2.5 and 2.6 present the tools and techniques used in the design and engineering of I/O-efficient algorithms. A reader familiar with the standard graph terminology, basic probability theory, random graph models, and the computation models capturing memory hierarchies may wish to skip sections 2.1, 2.2, 2.3 and 2.4, respectively.

# 2.1 Preliminary definitions

Formally, a graph G is an ordered pair of disjoint sets (V, E) such that E is a subset of the set of unordered pairs of V. In this manuscript, we only consider finite graphs, that is V and E are always finite (though they are often very large). The set V is the set of *vertices* and E is the set of *edges*. If G is a graph then

V = V(G) is the vertex set of G and E = E(G) is the edge set. An edge  $\{x,y\}$  is said to *join* the vertices x and y. The vertices x and y are the *end-vertices* of this edge. If  $\{x,y\} \in E$ , then x and y are *adjacent* or *neighboring* vertices of G and the vertices x and y are *incident* with the edge  $\{x,y\}$ . Two edges are *adjacent* if they have exactly one common end-vertex. We also use the notation G(V,E) to refer to a graph G = (V,E) and  $G(V,E,w(\cdot))$  to refer to a weighted graph G = (V,E), where each edge  $e := \{x,y\} \in E$  is associated with a weight w(e) (or w(x,y)).

The set of neighbors of a vertex v in G is denoted by  $N_G(v)$ , or briefly by N(v). More generally for  $U\subseteq V$ , the neighbors in  $V\setminus U$  of vertices in U are called neighbors of U; their set is denoted by N(U). The degree d(v) of a vertex v is the number |E(v)| of edges at v; this is equal to the number of neighbors of v. A vertex of degree 0 is isolated. The number  $\delta(G):=\min\{d(v)|v\in V\}$  is the minimum degree of G, the number  $\Delta(G):=\max\{d(v)|v\in V\}$  denotes its maximum degree. The number  $d(G):=\frac{1}{|V|}\sum_{v\in V}d(v)=\frac{2|E|}{|V|}$  is the average degree of G. Clearly,  $\delta(G)\leq d(G)\leq \Delta(G)$ .

An independent set in G = (V, E) is a set of nodes  $V' \subseteq V$  such that if  $u, v \in V'$ ,  $\{u, v\} \notin E$  i.e., no two nodes of V' are adjacent in G. A maximal independent set is an independent set which is not contained in any larger independent set.

We say that G' = (V', E') is a *subgraph* of G = (V, E) if  $V' \subseteq V$  and  $E' \subseteq E$ . In this case, we write  $G' \subseteq G$ . If G' contains all edges of G that join two vertices in V' then G' is said to be the subgraph induced by V' and is denoted by G[V']. A subgraph G' of G is an *induced subgraph* if G' = G[V(G')].  $G' \subseteq G$  is a *spanning subgraph* of G if G' is an induced subgraph of G'. We say G' spans G.

A *self-loop* is an edge that connects a vertex to itself. A *simple graph* is an undirected graph that has no self-loops and no more than one edge between any two different vertices. In this thesis, we will only be dealing with simple graphs. A complete graph is a simple graph in which every pair of distinct vertices is connected by an edge. An empty graph on n nodes consists of n isolated nodes with no edges.

A path P from u to w in a graph G is a node sequence  $(v_0, v_1, \ldots, v_k)$  for some  $k \ge 1$ , such that the edges  $\{v_0, v_1\}, \{v_1, v_2\}, \ldots, \{v_{k-1}, v_k\}$  are part of E,  $v_0 = u$ , and  $v_k = w$ . If all nodes  $v_i$  on P are pairwise distinct then we say that the path is *simple*. Cycles are those paths where the starting point and the endpoint are identical. The *weight* of a path  $P = (v_0, \ldots, v_k)$  from u to v in a weighted graph  $G(V, E, w(\cdot))$  is defined to be  $\sum_{i=0}^{k-1} w(v_i, v_{i+1})$ .

A non-empty graph G is called *connected* if any two of its vertices are linked

by a path in G. A maximal connected subgraph of G is called a *component* or a *connected component* of G. An acyclic graph, one not containing any cycles, is called a *forest*. A connected forest is called a *tree*. The vertices of degree 1 in a tree are its *leaves*. The weight of a forest (tree) is defined to be the sum of the weights of all the edges in the forest (tree). A forest F (tree T) that spans G is a *spanning forest* (*spanning tree*) of G. A spanning forest (spanning tree) of minimum weight is called *minimum spanning forest* (*minimum spanning tree*).

The distance d(x,y) in G (also referred as  $d_G(x,y)$ ) of two vertices x,y is the minimum weight of a path from x to y in G; if no such path exists, we set  $d(x,y) := \infty$ . The greatest distance between any two vertices in G is the diameter of G, denoted by diam(G). Sometimes it is convenient to consider one vertex of a tree as special; such a vertex is then called a *root* of this tree. A tree with a fixed root is a *rooted tree*.

An edge set E of a directed graph consists of ordered pairs of nodes: an edge e from node u to node v is denoted by e = (u, v). Here u is also called the tail, v the head, and both nodes are called endpoints of (u, v). Furthermore, (u, v) is referred to as one of u's outgoing edges or one of v's incoming edges, as an edge leaving u or an edge entering v. The number of edges leaving (entering) a node is called the out-degree (in-degree) of this node. The degree of a node is the sum of its in-degree and out-degree.

A path P from u to w in a directed graph G is a node sequence  $(v_0, v_1, \ldots, v_k)$  for some  $k \ge 1$ , such that the edges  $(v_0, v_1), (v_1, v_2), \ldots, (v_{k-1}, v_k)$  are part of E,  $v_0 = u$ , and  $v_k = w$ . The nodes  $v_0$  and  $v_k$  are called the starting point and endpoint of P, respectively. If all nodes  $v_i$  on P are pairwise distinct then we say that the path is *simple*. Cycles are those paths where the starting point and the endpoint are identical. A graph is called *acyclic* if it does not contain any directed cycle.

A linear order is a relation that is reflexive, transitive, antisymmetric, and total. A topological order T of a directed graph G(V,E) is a linear ordering of its nodes such that for all directed paths from  $x \in V$  to  $y \in V$  ( $x \neq y$ ), it holds that T(x) < T(y). A directed graph has a topological ordering if and only if it is acyclic.

A *walk* is an alternating sequence of vertices and edges, beginning and ending with a vertex, in which each vertex is incident to the two edges that precede and follow it in the sequence, and the vertices that precede and follow an edge are the end vertices of that edge. A walk is *closed* if its first and last vertices are the same, and *open* if they are different.

A trail is a walk in which all the edges are distinct. A closed trail is called a tour

or a *circuit*. *Euler tour* is a tour which contains all the edges exactly once. A graph that contains an Euler tour is an *Eulerian graph*.

Graph traversal refers to the problem of visiting all the nodes in a graph in a particular (structured) manner. Popular examples of graph traversal are Breadth-First Search, Depth-First Search, A\*, and Dijkstra's algorithm. Tree traversal is a special case of graph traversal. Examples of tree traversal include pre-order, post-order, and in-order traversal. A pre-order traversal visits all nodes of a tree by processing the root, then recursively processing all subtrees rooted at its children from left to right. A post-order traversal first recursively processes all subtrees from left to right and then processes the node. An in-order traversal on binary trees first processes the left subtree, then the root and finally the right subtree.

# 2.2 Basic probability theory

In this section we review a few basic definitions and facts for the probabilistic analysis of algorithms.

The *sample space*, often denoted  $\Omega$  of an experiment or random trial is the set of all possible outcomes. Any subset  $\varepsilon \subseteq \Omega$  of the sample space is usually called an *event*. A *probability measure* P is a function that satisfies the following three conditions:  $0 \le P[\varepsilon] \le 1$  for each  $\varepsilon \subseteq \Omega$ ,  $P[\Omega] = 1$ , and  $P[\cup_i \varepsilon_i] = \sum_i P[\varepsilon_i]$  for pairwise disjoint events  $\varepsilon_i$ . A sample space together with its probability measure build a *probability space*. For a problem of size n, we say that an event  $\varepsilon$  occurs with high probability (w.h.p.) if  $P[\varepsilon] \ge 1 - O(n^{-\alpha})$  for an arbitrary but fixed constant  $\alpha \ge 1$ . The *conditional probability*  $P[\varepsilon_1|\varepsilon_2] = \frac{P[\varepsilon_1 \cap \varepsilon_2]}{P[\varepsilon_2]}$  refers to the probability of an event  $\varepsilon_1$  to occur when we already know that another event  $\varepsilon_2$  happens. Two events  $\varepsilon_1$  and  $\varepsilon_2$  are called *independent* if  $P[\varepsilon_1|\varepsilon_2] = P[\varepsilon_1]$ .

Any real valued numerical function  $X=X(\Omega)$  defined on a sample space  $\Omega$  may be called a *random variable*. If X maps elements in  $\Omega$  to  $\mathbb{R}_+ \cup \{0\}$  then it is called a *nonnegative* random variable. A *discrete* random variable only takes isolated values with nonzero probability. Typical representatives for discrete random variables are *binary* random variables, which map elements in  $\Omega$  to  $\{0,1\}$ . Two random variables X and Y are called *independent* if, for all  $x,y\in\mathbb{R}$ , P[X=x|Y=y]=P[X=x].

The *expectation* of a discrete random variable X is given by  $E[X] = \sum_{x \in \mathbb{R}} x \cdot P[X = x]$ . Here are a few important properties of the expectation for arbitrary random variables X and Y:

• If *X* is nonnegative, then E[X] > 0.

- $|E[X]| \le E[|X|]$ .

- $E[c \cdot X] = c \cdot E[X]$  for any  $c \in \mathbb{R}$ .

- E[X + Y] = E[X] + E[Y] (Linearity of expectation).

- If *X* and *Y* are independent, then  $E[X \cdot Y] = E[X] \cdot E[Y]$ .

Frequently, we are interested in the probability that random variables do not deviate too much from their expected values. The *Markov Inequality* for an arbitrary nonnegative random variable X states that  $P[X \ge k] \le \frac{E[X]}{k}$  for any k > 0. The *Chebyshev Inequality* states that if a random variable X has an expected value  $\mu$  and finite variance  $\sigma^2$ , then for any real number k > 0,

$$P[|X - \mu| \ge k \cdot \sigma] \le \frac{1}{k^2}.$$

In our average case analysis of online topological ordering algorithms, we will use an alternative formulation of this inequality:

$$P[|X - \mu| \ge v] \le \frac{\sigma^2}{v^2}.$$

More powerful tail estimates exist for the sum of independent random variables. Here is one version of the well-known *Chernoff bound*: Let  $X_1, \ldots, X_k$  be independent binary random variables and  $\mu = E[\sum_{j=1}^k X_j]$ . Then it holds for all  $\delta > 0$  that

$$P[\sum_{i=1}^{k} X_j \ge (1+\delta) \cdot \mu] \le e^{-\min\{\delta^2, \delta\} \cdot \mu/3}.$$

Furthermore, it holds for all  $0 < \delta < 1$  that

$$P[\sum_{j=1}^k X_j \le (1-\delta) \cdot \mu] \le e^{-\delta^2 \cdot \mu/2}.$$

# 2.3 Random Graph Model

Random graph models are important tools for the average-case analysis of graph traversal algorithms. Furthermore, since most real-world phenomenon have a random component, many important properties of real-world graphs are similar to those of random graphs. For instance, our experiments suggests that the performance of various external memory BFS algorithms on webgraphs is similar to that on random graphs.

Erdős and Rényi [66, 67] introduced and popularized random graphs. They defined two closely related models: G(n,p) and G(n,m). The G(n,p) model (0 < p < 1) consists of a graph with n nodes in which each edge is chosen independently with probability p. On the other hand, the G(n,m) model assigns equal probability to all graphs with n nodes and exactly m edges. Each such graph occurs with a probability of  $1/\binom{N}{m}$ , where  $N := \binom{n}{2}$ .

For our study of online topological ordering algorithms, we use the random DAG model of Barak and Erdős [26]. They obtain a random DAG by directing the edges of an undirected random graph from lower to higher indexed vertices. Depending on the underlying random graph model, this defines the DAG(n, p) and DAG(n, M) model.

The set of all DAGs with n nodes is denoted by  $DAG^n$ . For a random variable f with probability space  $DAG^n$ ,  $\mathbf{E}_M[f]$  and  $\mathbf{E}_p[f]$  denotes the expected value in the DAG(n,M) and DAG(n,p) model, respectively.

The following theorem shows that in most investigations the models G(n, p) and G(n, m) are practically interchangeable, provided m is close to  $p \cdot N$ .

**Theorem 1** Given a function  $f: G^n \to [0,a]$  with a > 0 and  $f(G) \le f(H)$  for all  $G \subseteq H$  and functions p and m of n with 0 , <math>q := 1 - p,  $N := \binom{n}{2}$ , and  $m \in \mathbb{N}$ .

1. If

$$\lim_{n\to\infty} pqN = \lim_{n\to\infty} \frac{pN-m}{\sqrt{pqN}} = \infty$$

, then  $\mathbf{E}_M[f] \le \mathbf{E}_p[f] + o(1)$ .

2. If

$$\lim_{n\to\infty} pqN = \lim_{n\to\infty} \frac{m-pN}{\sqrt{pqN}} = \infty$$

, then  $\mathbf{E}_p[f] \leq \mathbf{E}_M[f] + o(1)$ .

A closer look at the proof for it given by Bollobás [33] reveals that the probabilistic argument used to show the close connection between G(n,p) and G(n,M) can be applied in the same manner for the two random DAG models DAG(n,p) and DAG(n,M).

**Theorem 2** Given a function  $f: DAG^n \to [0,a]$  with a > 0 and  $f(G) \le f(H)$  for all  $G \subseteq H$  and functions p and m of n with 0 , <math>q := 1 - p,  $N := \binom{n}{2}$ , and  $m \in \mathbb{N}$ ,

1. If

$$\lim_{n\to\infty} pqN = \lim_{n\to\infty} \frac{pN-m}{\sqrt{pqN}} = \infty$$

, then  $\mathbf{E}_M[f] \leq \mathbf{E}_p[f] + o(1)$ .

2. If

$$\lim_{n\to\infty} pqN = \lim_{n\to\infty} \frac{m-pN}{\sqrt{pqN}} = \infty$$

, then  $\mathbf{E}_p[f] \leq \mathbf{E}_M[f] + o(1)$ .

# 2.4 Computation models capturing memory hierarchies

We start this section by describing the RAM model which is one of the most popular computation models for designing algorithms.

#### 2.4.1 RAM model or von Neumann model

The running time of an algorithm is traditionally analyzed by counting the number of executed primitive operations or "instructions" as a function of the input size n. The implicit underlying model of computation is the one-processor, random-access machine (RAM) model. The RAM model or the "von Neumann model of computation" consists of a computing device attached to a storage device (or "memory"). The following are the key assumptions of this model:

- Every instruction takes the same amount of time, at least up to small constant factors.

- Unbounded amount of available memory.

- Memory stores words of size  $O(\log n)$  bits where n is the input size.

- Any desired memory location can be accessed in unit time.

The above assumptions greatly simplify the analysis of algorithms and allow for expressive asymptotic analysis.

#### 2.4.2 Real Architecture

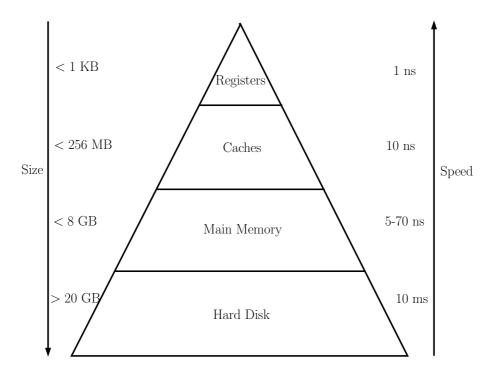

Unfortunately, modern computer architecture is not as simple. Rather than having an unbounded amount of unit-cost access memory, we have a hierarchy of storage devices (Figure 2.1) with very different access times and storage capacities. Modern computers have a microprocessor attached to a file of *registers*. The *first level* (L1) cache is usually only a few kilobytes large and incurs a delay of a few clock cycles. Often there are separate L1 caches for instructions and data. Nowadays, typical *second level* (L2) cache has a size of about 32-64 KB and access latencies around ten clock cycles. Some processors also have a rather expensive *third level* (L3) cache of up to 256 MB made of fast static random access memory cells. A

Figure 2.1: Memory Hierarchy in modern computer architecture.

cache consists of *cache lines* that each store a number of memory words. If an accessed item is not in the cache, it and its neighbor entries are fetched from the main memory and put into a cache line. These caches usually have limited associativity, i. e. an element brought from the main memory can be placed only in a restricted set of cache lines. In a *direct-mapped* cache the target cache line is fixed and only based on the memory address, whereas in a *full-associative* cache the item can be placed anywhere. Since the former is too restrictive and the latter is expensive to build and manage, a compromise often used is a *set-associative* cache. There, the item's memory address determines a fixed set of cache lines into which the data can be mapped, though within each set, any cache line can be used. The typical size of such a set of cache lines is a power of 2 in the range from 2 to 16. For more details about the structure of caches the interested reader is referred to [122] (in particular its Chapter 7).

The *main memory* is made out of dynamic random access memory cells. These cells store a bit of data as a charge in a capacitor rather than storing it as the state of a flip-flop which is the case for most static random access memory cells. It requires practically the same amount of time to access any piece of data stored in the main memory, irrespective of its location, as there is no physical movement (e. g. of a reading head) involved in the process of retrieving data. Main memory

is usually volatile, which means that it loses all data when the computer is powered down. At the time of writing this thesis, the main memory size is usually between 512 MB and 8 GB and a typical RAM memory has an access time of 5 to 70 nanoseconds.

Magnetic *hard disks* offer cheap non-volatile memory with an access time of 10 ms, which is 10<sup>6</sup> times slower than a register access. This is because it takes very long to move the access head to a particular track of the disk and wait until the disk rotates into the seeked position. However, once the head starts reading or writing, data can be transfered at the rate of 35-105 MB/s [80]. Hence, reading or writing a contiguous block of hundreds of KB takes only about twice as long as accessing a single byte, thereby making it imperative to process data in large chunks.

Apart from the above mentioned levels of a memory hierarchy, there are instruction pipelines, an instruction cache, logical/physical pages, the translation lookaside buffer (TLB), magnetic tapes, optical disks and the network, which further complicate the architecture.

The reasons for such a memory hierarchy are mainly economical. The faster memory technologies are costlier and, as a result, fast memories with large capacities are economically prohibitive. The memory hierarchy emerges as a reasonable compromise between the performance and the cost of a machine.

#### **Disadvantages of the RAM Model**

The beauty of the RAM model lies in the fact that it hides all the messy details of computer architecture from the algorithm designer and at the same time, it encapsulates the comparative performance of algorithms remarkably well. It strikes a fine balance by capturing the essential behavior of computers while being simple to work with. The performance guarantees in the RAM model are not architecture-specific and therefore robust. However, this is also the limiting factor for the success of this model. In particular, it fails significantly when the input data or the intermediate data structure is too large to reside completely within the internal memory.

For most (traversal) problems on large (graph) data sets, the dominant part of the running time of algorithms is not the number of "instructions", but the time these algorithms spend waiting for the data to be brought from the hard disk to internal memory. The I/Os or the movement of data between the memory hierarchies (and in particular between the main memory and the disk) are not captured by the RAM

model and hence, the predicted performance on the RAM model may increasingly deviate from the actual performance.

#### **Future Trends**

The problem is likely to aggravate in the future. In following with the Moore's law, the number of transistors double every 18 months. As a result, the CPU speed continues to improve at nearly the same pace, i.e., an average performance improvement of 1% per week. Besides, the usage of parallel processors and multicores makes the computations even faster. On the other hand, random access memory speeds and hard drive seek times improve at best a few percentages per year. Although the capacity of the random access memory doubles about every two years, users double their data storage every 5 months. The Internet applications like social networks and e-commerce companies (cf. Section 1.1) are also extending their user and product base at a very fast pace.

# 2.4.3 External Memory Model

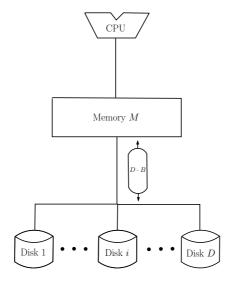

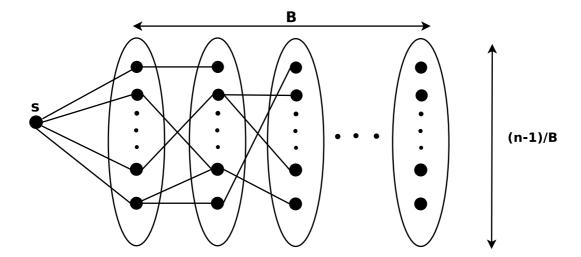

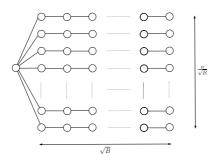

Figure 2.2: The external memory model

The I/O model or the external memory (EM) model (depicted in Figure 2.2) as introduced by Aggarwal and Vitter [3] assumes a single central processing unit and two levels of memory hierarchy. The internal memory is fast, but has a limited size of M words. In addition, we have an external memory which can only be accessed

using I/Os that move B contiguous words between internal and external memory. For graph traversal problems, the notation is slightly altered: we assume that the internal memory can have up to M data items of a constant size (e.g., vertices or edges), and in one I/O operation, B contiguous data items move between the two memories. At any particular time, the computation can only use the data already present in the internal memory. The measure of performance of an algorithm is the number of I/Os it performs. An algorithm A is better than another algorithm A' if A requires less I/Os than A'.

Although we mostly use the sequential variant of the external memory model, it also has an option to express disk parallelism. There can be *D* parallel disks and in one I/O, *D* arbitrary blocks can be accessed in parallel from the disks. The usage of parallel disks helps us alleviate the I/O bottleneck.

#### 2.4.4 Parallel Disk Model

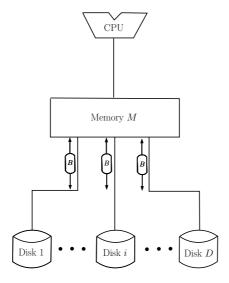

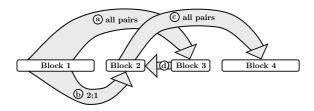

Figure 2.3: Parallel Disk Model

The parallel disk model (depicted in Figure 2.3) by Vitter and Shriver [152] is similar to the external memory model, except that it adds a realistic restriction that only one block can be accessed per disk during an I/O, rather than allowing D arbitrary blocks to be accessed in parallel. The parallel disk model can also be extended to allow parallel processing by allowing P parallel identical processors each with M/P internal memory and equipped with D/P disks.

Sanders et al. [140] gave efficient randomized algorithms for emulating the external memory model of Aggarwal and Vitter [3] on the parallel disk model.

#### 2.4.5 Ideal Cache Model

In the external memory model we are free to choose any two levels of the memory hierarchy as internal and external memory. For this reason, external memory algorithms are sometimes also referred to as cache-aware algorithms ("aware" as opposed to "oblivious"). There are two main problems with extending this model to caches: limited associativity and automated replacement. As shown by Sen and Chatterjee [143], the problem of limited associativity in caches can be circumvented at the cost of constant factors. Frigo et al. [73] showed that a regular algorithm causes asymptotically the same number of cache misses with LRU or FIFO replacement policy as with optimal off-line replacement strategy. Intuitively, an algorithm is called regular if the number of incurred cache misses (with an optimal off-line replacement) increases by a constant factor when the cache size is reduced to half.

Similar to the external memory model, the ideal cache model assumes a two level memory hierarchy, with the faster level having a capacity of storing at most M elements and data transfers in chunks of B elements. In addition, it also assumes that the memory is managed automatically by an optimal off-line cache-replacement strategy, and that the cache is fully associative.

#### 2.4.6 Cache-Oblivious Model

In practice, the model parameters B and M need to be finely tuned for an optimal performance. For different architectures and memory hierarchies, these values can be very different. This fine-tuning can be at times quite cumbersome. Besides, we can optimize only one memory hierarchy level at a time. Ideally, we would like a model that would capture the essence of the memory hierarchy without knowing its specifics, i.e. values of B and M, and at the same time be efficient on all hierarchy levels simultaneously. Yet, it should be simple enough for a feasible algorithm analysis. The cache oblivious model introduced by Frigo et al. [73] promises all of the above. In fact, the immense popularity of this model lies in its innate simplicity and its ability to abstract away the hardware parameters.

The cache-oblivious model also assumes a two level memory hierarchy with an internal memory of size M and block transfers of B elements in one I/O. The performance measure is the number of I/Os incurred by the algorithm. However, the algorithm does not have any knowledge of the values of M and B. Consequently, the guarantees on I/O-efficient algorithms in the cache-oblivious model hold not only on any machine with multi-level memory hierarchy but also on all levels of

the memory hierarchy at the same time. In principle, they are expected to perform well on different architectures without the need of any machine-specific optimization.

The cache-oblivious model assumes full associativity and optimal replacement policy. However, as we argued for the ideal cache model (cf. Section 2.4.5), these assumptions do not affect the asymptotics on realistic caches.

However, note that cache-oblivious algorithms are usually more complicated than their cache-aware I/O-efficient counterparts. As a result, the constant factors hidden in the complexity of cache-oblivious algorithms are usually higher and on large external memory inputs, they are slower in practice.

# 2.4.7 Various streaming models

In the data stream model [116], input data can only be accessed sequentially in the form of a data stream, and needs to be processed using a working memory that is small compared to the length of the stream. The main parameters of the model are the number p of sequential passes over the data and the size s of the working memory (in bits). Since the classical data stream model is too restrictive for graph algorithms and even the undirected connectivity requires  $s \times p = \Omega(n)$  [82] (where n is the number of nodes in a graph), less restrictive variants of streaming models have also been studied. These include stream-sort model [4] where sorting is also allowed, W-stream model [58] where one can use intermediate temporary streams and semi-streaming model [68], where the available memory is  $O(n \cdot polylog(n))$  bits.

# 2.4.8 Other memory hierarchy models

Recently, Arge et al. [23] have proposed Parallel External-Memory model as a natural parallel extension of the external-memory model of Aggarwal and Vitter [3], to private-cache chip multiprocessors.

There are still a number of issues not addressed by these models that can be critical for performance in practical settings, e. g. branch mispredictions [87], TLB misses etc. For other models on memory hierarchies, refer to [4, 25, 94, 114, 131].

# 2.5 Basic tools for designing external memory graph traversal algorithms

Many different tools and techniques have been developed for graph algorithms in external memory in the last couple of decades. In this Section, we describe some of the commonly used building blocks for the design of I/O-efficient graph traversal algorithms.

# 2.5.1 Parallel scanning

Scanning many different streams (of data from the disk) simultaneously is one of the most basic tools used in I/O-efficient algorithms. This can be used, for example, to copy some information from one stream to the other. Sometimes, different streams represent different sorted sets and parallel scanning can be used to compute various operations on these sets such as union, intersection, or difference.

Given k = O(M/B) streams containing a total of O(n) elements, we can scan them "in parallel" in scan(n) = O(n/B+k) I/Os. This is done by simply keeping O(1) blocks of each stream in the internal memory. When we need a block not present in the internal memory, we remove (or write back to the disk) the existing block from the corresponding stream and load the required block from the disk.

# 2.5.2 Sorting

Sorting is fundamental to many I/O-efficient graph traversal algorithms. In particular, sorting can be used to rearrange the nodes on the disk so that a graph traversal algorithm does not have to spend  $\Omega(1)$  I/Os for loading the adjacency list of each node into the internal memory.

Sorting n elements in the external memory requires  $\operatorname{sort}(n) = \Theta(\frac{n}{B}\log_{\frac{M}{B}}\frac{n}{B})$  I/Os [3]. There exist many different algorithms for I/O-efficient sorting. The most commonly used external memory sorting algorithm is based on (M/B)-way merge sort. It first scans through the input data, loading M elements at a time, sorting them internally and writing them back to disk. In the next round, we treat each of these chunks as a stream and merge O(M/B) streams at a time using "parallel scanning" to produce sorted chunks of size  $O(M^2/B)$ . By repeating this process for  $O(\log_{\frac{M}{B}}\frac{n}{B})$  rounds, we get all the elements sorted.

External memory libraries such as STXXL [56, 57] and TPIE [21] provide fast implementations of external memory sorting routines. STXXL also has specialized functions for sorting elements with integer keys and sorting streams.

In the cache-oblivious setting, funnel-sort [73] and lazy funnel-sort [39], also based on a merging framework, lead to sorting algorithms with the same I/O complexity of  $\Theta(\frac{n}{B}\log_{\frac{M}{B}}\frac{n}{B})$  I/Os. Brodal et al. [41] show that a careful implementation of this algorithm outperforms several widely used library implementations of quick-sort on uniformly distributed data. For the largest instances in the RAM, this implementation outperforms its nearest rival std::sort from the STL library included in GCC 3.2 by 10-40% on many different architectures like Pentium III, Athlon and Itanium 2.

#### 2.5.3 PRAM simulation

A Parallel Random Access Machine (PRAM) is a basic model of computation that consists of a number of sequential processors, each with its own memory, working synchronously and communicating between themselves through a common shared memory.

Simulating a PRAM algorithm [48] on the external memory model is an important tool in the design of I/O-efficient graph algorithms. A PRAM algorithm that uses p processors and O(p) (shared memory) space and runs in time T(p) can be simulated in  $O(T(p) \cdot \text{sort}(p))$  I/Os.

Each step taken by a PRAM involves each processor independently reading a data element, computing on it and writing some output. In order to simulate it on the external memory model, the read requests of all the processors are sorted according to the location of the required data. Afterwards, one scan of the entire data of the shared memory is enough to fetch all the requisite data. This is then sorted back according to the processor ids. Thereafter, in one scan of the fetched data, we perform all the computations by all the processors and collect the output data (together with its location) that would have been produced by each processor. This is then sorted according to the memory location and written back to the disk. Thus, each step of the O(p)-processor PRAM algorithm requiring O(p) space can be simulated by a constant number of sorts and scans, i.e., O(sort(p)) I/Os.

PRAM simulation is particularly appealing as it translates a large number of PRAM-algorithms into I/O-efficient and sometimes I/O-optimal algorithms.

Even without directly using the simulation, I/O-efficient algorithms can be obtained by appropriately translating PRAM algorithms, as many of the ideas ap-

plied in parallel computing for reducing a problem into many independent subproblems are also useful for designing external memory algorithms. For many problems, the bounds obtained by appropriately translating PRAM algorithms are much better than those obtained by direct simulation.

# 2.5.4 Algorithms on trees

Efficient external memory algorithms are known for many different problems on undirected trees. These include rooting a tree, computing pre-order, post-order or in-order traversal, computing the depth of each node, least common ancestor queries, etc. Most of these algorithms (e.g., the tree traversal algorithms in [48]) are efficient translations of their PRAM counterparts.

# 2.5.5 Priority queues

A priority queue is an abstract data structure that stores an ordered set of keys and allows efficient insertion, search of the minimum element (find\_min) and deletion of the minimum element (delete\_min). Sometimes operations such as deleting an arbitrary key and decreasing the value of the key are also supported. Priority queues are fundamental to many graph traversal algorithms, particularly for computing single-source shortest-paths.

One way of implementing efficient external memory priority queues is using buffer trees [17]. Buffer trees are useful for batched operations, i.e., when the answers to the queries are not required immediately but eventually.

A buffer tree has degree  $\Theta(M/B)$ . Each internal node is associated with a buffer containing a sequence of up to  $\Theta(M)$  updates and queries to be performed in its subtree. Leaves contain  $\Theta(B)$  keys. Updates and queries are simply performed by inserting the appropriate signal in the root node buffer. If the buffer is full, the signal buffer is flushed to its children. This process may need to be repeated all the way down to the leaves. Since flushing the buffer requires  $\Theta(M/B)$  I/Os (which is done after inserting  $\Theta(M)$  signals) and the tree has  $O(\log_{M/B} n/B)$  levels, the amortized cost of the update and query operations is  $O((1/B) \cdot \log_{M/B} (n/B))$  I/Os. It can be shown that the re-balancing operations for maintaining the tree can also be done within the same bounds.

In order to use buffer trees as a priority queue, the entire buffer of the root node together with the O(M/B) leftmost leaves (all the leaves of the leftmost internal

node) is kept in internal memory. We maintain the invariant that all buffers on the path from the root to the leftmost leaf are empty. Thus, the element with the smallest priority always remains in internal memory. The invariant is maintained by flushing out all buffers in the leftmost path whenever the root buffer is flushed, at a total cost of  $O((M/B) \cdot \log_{M/B}(n/B))$  I/Os. The amortized cost of updates and queries still remains  $O((1/B) \cdot \log_{M/B}(n/B))$  I/Os.

Note that the buffer tree based priority queue can not efficiently perform a decrease\_key of an element, if we do not know its old key. For efficient but lazy decrease\_key operations, we can use tournament trees [93]. On an I/O-efficient tournament tree with n elements, any sequence of z operations each of them being either a delete, delete\_min or an update, requires at most  $O((z/B) \cdot \log_2{(n/B)})$  I/Os. The update operation referred here is a combined insert and decrease\_key operation.

Cache-oblivious priority queues with amortized  $O((1/B) \cdot \log_{M/B}(n/B))$  I/O insertion, deletion and delete\_min operations have also been developed [20, 38]. The cache-oblivious bucket heap based priority queue [40] provides amortized  $O((1/B) \cdot \log_2(n/B))$  update, delete and delete\_min operations, where the update operation is similar to the one provided by tournament trees.

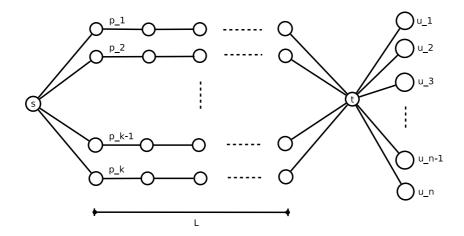

## 2.5.6 Time forward processing

Time forward processing [17, 48] is an elegant technique for solving problems that can be expressed as a traversal of a directed acyclic graph (DAG) from its sources to its sinks. Let G be a DAG and  $\phi(v)$  be a label associated with the node v. The goal is to compute another labelling  $\psi(v)$  for all nodes  $v \in G$ , given that  $\psi(v)$  can be computed from labels  $\phi(v)$  and  $\psi(u_1), \ldots, \psi(u_k)$ , where  $u_1, \ldots, u_k$  are the in-neighbors of v.

Time forward processing on an n-node DAG can be solved in external memory in  $O(\operatorname{sort}(n))$  I/Os if the following conditions are met:

- 1. The nodes of G are stored in topologically sorted order.

- 2.  $\psi(v)$  can be computed from  $\phi(v)$  and  $\psi(u_1), \dots, \psi(u_k)$  in  $O(\operatorname{sort}(k))$  I/Os.

This bound is achieved by processing the nodes in the topologically sorted order and letting each node pass its label  $\psi$  to its out-neighbors using a priority queue. Each node u inserts  $\psi(u)$  in the priority queue for each out-neighbor v with the key being the topological number of v, T(v). We ensure that before we process v,

we extract all the nodes with priority T(v) and therefore, get all the necessary information to compute  $\psi(v)$ .

## 2.5.7 Graph contraction

The key idea in graph contraction is to reduce the size of the input graph G while preserving the properties of interest. Such a procedure is often applied recursively till either the number of edges or the number of nodes are reduced by a factor of O(B) or the number of nodes is reduced to O(M). In the first case, the algorithm can afford to spend O(1) I/Os per remaining node to solve the problem. In the latter case, an efficient semi-external algorithm is used to solve the problem.

Graph contraction is particularly useful for problems like connected components and minimum spanning forests, where the connectivity information is preserved (see e.g. [18]) during the edge contraction steps.

## 2.5.8 Graph clustering

Clustering a graph refers to decomposing the graphs into disjoint clusters of nodes. Each cluster contains the adjacency lists of a few nodes. These nodes should be close in the original graph. Since each cluster is connected and small, if a node of the cluster is visited during BFS, SSSP or APSP, the other nodes of the cluster will also be visited "shortly". This fact can be exploited to design better algorithms (see e.g. [106], [112]) for these problems.

## 2.5.9 Ear decomposition

An ear decomposition  $\varepsilon = (P_0, P_1, P_2, \dots, P_k)$  of a graph G = (V, E) is a partition of E into an ordered collection of edge-disjoint simple paths  $P_i$  with endpoints  $s_i$  and  $t_i$ . Ear  $P_0$  is an edge. For  $1 \le i \le k$ , ear  $P_i$  shares its two endpoints  $s_i$  and  $t_i$ , but none of its internal nodes, with the union  $P_0 \cup \dots P_{i-1}$  of all previous ears. A graph has an ear decomposition if and only if it is two-edge connected, i.e., removing any edge still leaves a connected subgraph.

An ear decomposition of a graph can be computed in  $O(\operatorname{sort}(n))$  I/Os in external memory [103].

# 2.6 Tools for engineering external memory graph traversal algorithms

In the last decade, many techniques have evolved for engineering external memory graph traversal algorithms. Libraries specifically containing fundamental algorithms and data structures for external memory have been developed. Techniques such as pipelining can save some constant factors from the I/O complexity of the external memory implementations, which can be significant for making the implementation viable. In this section, we describe some of these tools and techniques.

## 2.6.1 External memory libraries

External memory libraries play a crucial role in engineering algorithms running on large data-sets. These libraries not only reduce the development time for external memory algorithms, but also speed up the implementations themselves. The former is done by abstracting away the details of how an I/O is performed and providing ready-to-use building blocks including algorithms such as sorting and data structures such as priority queues. The latter is done by offering frameworks such as pipelining (described ahead in this section) that can reduce the constant factors in the I/O complexity of an implementation. Furthermore, the algorithms and data structures provided are optimized and perform less internal memory work.

#### **STXXL**

STXXL [56, 57] is an implementation of the C++ standard template library STL [147] for external memory computations. Since the data-structures and algorithms in STXXL have a well known generic interface similar to STL interface, it is easy to use and the existing applications based on STL can be easily made to work with STXXL. STXXL supports parallel disks, overlapping between disk I/O and computation and the *pipelining* technique that can save a significant fraction of the I/Os. It provides I/O-efficient implementations of various containers (stack, queue, deque, vector, priority queue,  $B^+$ -tree, etc.) and algorithms (scanning, sorting using parallel disks, etc.). It is being used both in academic and industrial environments for a range of problems including text processing, graph algorithms, computational geometry, Gaussian elimination, visualization, and analysis of microscopic images, differential cryptographic analysis, etc.

#### **TPIE**

TPIE [21] or "Transparent Parallel I/O Environment" is another C++ template library supporting out-of-core computations. The goal of the TPIE project has been to provide a portable, extensible, flexible, and easy to use programming environment for efficiently implementing I/O-efficient algorithms and data structures. Apart from supporting algorithms with a sequential I/O pattern (i.e., algorithms using primitives such as scanning, sorting, merging, permuting and distributing) and basic data structures such as  $B^+$ -tree, it supports many more external memory data structures such as (a,b)-tree, persistent B-tree, Bkd-tree, K-D-B-tree, R-tree, EPS-tree, CRB-tree etc. It is used for many geometric and GIS implementations.

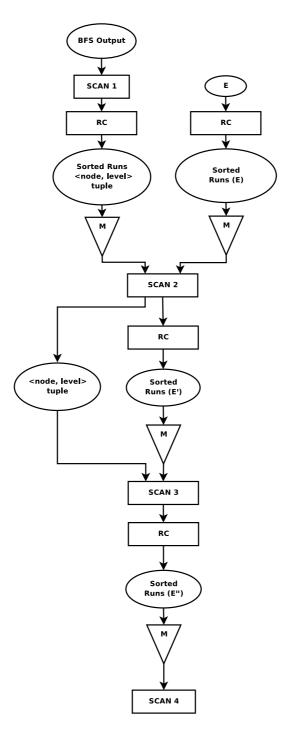

## 2.6.2 Pipelining