# Retargetable Postpass Optimisation by Integer Linear Programming

#### Dissertation

Zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultät I der Universität des Saarlandes

von

Diplom-Informatiker **Daniel Kästner**

Oktober, 2000

Tag des Kolloquiums: 22.12.2000

Dekan: Prof. Dr. R. Schulze-Pillot

Gutachter: Prof. Dr. R. Wilhelm

Prof. Dr.-Ing. L. Thiele

Vorsitzender: Prof. Dr.-Ing. P. Slusallek

#### Abstract

Embedded Systems are subject to severe cost restrictions but impose high performance requirements on typical applications. This has lead to the development of specialised irregular hardware architectures for which traditional code generation and optimisation techniques fail to achieve a satisfactory code quality. Therefore assembly programming is still common practice. One reason for this is the interdependence of code generation phases, the socalled phase-coupling problem. Integer linear programming (ILP) allows to integrate several phases in a homogeneous problem description and to solve them simultaneously. In this thesis, two well-structured ILP formulations for the problem of global phasecoupled code optimisation for irregular architectures are presented. The relationship between the design of the hardware architecture and the appropriate ILP modelling style is investigated. In order to speed up the computations, ILP-based approximations are developed that provide a very high solution quality and reduce the computation time significantly compared to the exact solution. The optimisations are implemented in a retargetable framework for postpass optimisations and analyses, called Propan. The relevant properties of the target architecture are concisely specified in a novel architecture description language TDL. From the TDL description a hardware-sensitive postpass optimiser is automatically generated that performs efficiency-increasing transformations on assembly code using integer linear programming. The system has been retargeted to several representative standard digital signal processors. Practical experiments demonstrate the applicability of this approach.

### Zusammenfassung

Eingebettete Systeme unterliegen engen Kostenschranken, typische Anwendungen stellen jedoch hohe Leistungsanforderungen. Dies hat zur Entwicklung spezialisierter irregulärer Hardwarearchitekturen geführt, für die traditionelle Codeerzeugungsund -optimierungsverfahren keine zufriedenstellenden Ergebnisse erzielen. Anwendungsprogramme für eingebettete Systeme werden daher oft in Assembler programmiert. Eine Ursache hierfür ist die gegenseitige Abhängigkeit der Codeerzeugungsphasen, das sogenannte Phasenkopplungsproblem. Ganzzahlige lineare Programmierung (ILP) jedoch ermöglicht es, verschiedene Teilprobleme in einer homogenen Problembeschreibung zu integrieren und gemeinsam zu lösen. In der vorliegenden Arbeit werden zwei strukturierte ILP-Formulierungen zur globalen, phasengekoppelten Codeoptimierung für irreguläre Architekturen vorgestellt. Der Zusammenhang zwischen dem Hardwareentwurf der Zielarchitektur und der geeigneten Modellierungsmethode für ganzzahlige lineare Programme wird herausgestellt. Zur Beschleunigung der Berechnungen werden ILP-basierte Approximationen entwickelt, die eine sehr hohe Codequalität erzielen und die Berechnungszeit im Vergleich zur exakten Lösung deutlich senken. Die Optimierungen wurden in einem retargierbaren System für Postpassoptimierungen und -analysen, genannt Propan, implementiert. Eine neue Architekturbeschreibungssprache TDL ermöglicht eine kurze und prägnante Spezifikation der relevanten Hardwareeigenschaften der Zielarchitektur. Aus der TDL-Beschreibung wird ein hardwaresensitiver Postpassoptimierer generiert, der durch Einsatz ganzzahliger linearer Programmierung effizienzsteigernde Transformationen von Assemblercode durchführt. Das System wurde für verschiedene repräsentative Standardprozessoren retargiert. Die experimentellen Ergebnisse belegen die Anwendbarkeit dieses Verfahrens.

## **Extended Abstract**

During the last years, the markets for telecommunication, embedded systems, and multimedia applications have been rapidly growing. The distinct cost sensitivity of these markets in connection with the stringent time constraints of real-time applications have led to the development of specialised, irregular hardware architectures designed to efficiently execute typical applications of digital signal processing. In the area of general-purpose processors, compiler technology has reached a high level of maturity. For irregular architectures however, the code quality achieved by traditional high-level language compilers is often not satisfactory. Generating efficient code for irregular architectures requires highly optimising techniques that have to be aware of specific hardware features of the target processor. Since such techniques are usually not provided by standard compilers, many digital signal processing applications are developed in assembly language. The increasing complexity of typical applications and the shrinking design cycles of embedded processors render this approach increasingly unacceptable. Therefore, there is an urgent need for retargetable code generation and optimisation techniques that can be quickly adapted to different target architectures and can provide a high code quality.

In this thesis the Propan system is presented as a retargetable framework for high-quality code optimisations and machine-dependent program analyses at assembly level. In the past, research on retargetability has mainly focused on closed compilation systems. Using such a system in industry however mostly requires replacing the existing compiler infrastructure which causes high costs. Thus the use of retargetable compilers in industry is rare. To the best of our knowledge, Propan is the first postpass framework where the issues of easy retargetability and of high-quality code optimisations have been combined. Due to the postpass orientation, Propan can be integrated in existing tool chains with moderate effort and allows to improve the code quality of existing compilers. Thus the costs associated with changing the compiler infrastructure in a company can be avoided. The retargetability concept of Propan is based on a combination of generic and generative mechanisms. We have developed a new machine description language called TDL which allows to specify the hardware resources of the target processor, its instruction set, and its assembly language in a concise way. Apart from the assembly orientation the main innovation of TDL is the generic modelling of irregular hardware constraints that allows them to be exploited in generic searchbased optimisation algorithms. From the TDL description a parser for the assembly

language and an architecture database are generated. The architecture database consists of a set of ANSI C files containing data structures representing all relevant information about the target architecture and functions to initialise, access and manipulate this information. The core system of Propan has been implemented in a generic, i.e., machine-independent way; if target-specific information is required, the generated architecture database is referenced. For each target architecture the architecture database is linked with the generic core system yielding a dedicated hardware-sensitive postpass optimiser.

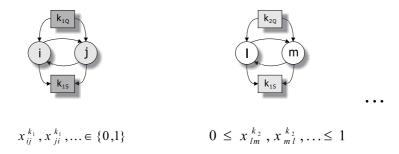

Generating high-quality code for irregular architectures requires taking the phase-coupling problem into account. In general, the code generation process is subdivided into several phases. For complexity reasons they are usually addressed separately by heuristic methods. While the heuristic approaches perform well for regular architectures, suboptimal combinations of suboptimal partial results can lead to poor code quality for irregular architectures. In this thesis a new approach is presented that unifies a well-known subset of the code generation phases at assembly level. The use of integer linear programming allows a generic homogeneous modelling of the problem of phase-coupled code optimisation taking into account irregular hardware characteristics of individual target architectures. The theory of integer linear programming has lead to sophisticated solution techniques such that powerful tools are available for computing solutions of integer linear programs. In our work we have developed extensions of two well-structured ILP formulations for phase-coupled instruction scheduling, register assignment and resource allocation. We have investigated the structure of both ILP formulations and the relationship between ILP modelling styles and hardware architectures. One formulation is based on an order-indexed modelling. It supports an efficient integration of the register assignment task for architectures with severely restricted instruction-level parallelism. The other formulation uses a time-indexed modelling. It provides an efficient integration of the problems of instruction scheduling and resource allocation. It is well suited for architectures where a large amount of alternative functional units has to be taken into account. In contrast to most other exact code generation methods the scope of the optimisations presented in this thesis is not restricted to single basic blocks. In order to speed up the computation process we have developed dedicated ILP-based approximations. Thus the generated integer linear programs can be solved either exactly providing provably optimal solutions, or by the use of the approximative methods. The basic idea of the approximations is the iterative solution of partial relaxations of the original problem. They allow to reduce the computation time significantly and still provide a very high solution quality.

The Propan framework has been retargeted to a wide range of architectures. It has been used to generate ILP-based postpass optimisers for two widely used modern digital signal processors with considerably different hardware characteristics, the Analog Devices ADSP-2106x [Ana95] and the Philips TriMedia TM1000 [Phi97]. Propan can also be used as a platform for generic program analyses and user-supplied hardware-dependent program optimisations. It is integrated in

a framework for calculating worst-case execution time guarantees for real-time systems [FKL<sup>+</sup>99]; in this context a TDL specification of the Infineon TriCore  $\mu$ C/DSP [Inf00] has been developed. For the Infineon C16x [Sie96] microprocessor family Propan has been used as a platform for implementing hardware-sensitive postpass optimisations that are part of a commercial postpass optimiser [Abs00a]. Various aspects of this thesis have been presented in a number of publications [KL98, KL99, Käs99a, KW99, FKL<sup>+</sup>99, Käs00a, Käs00b].

# Ausführliche Zusammenfassung

Innerhalb der letzten Jahre hat ein starkes Wachstum der Märkte für Telekommunikation, eingebettete Systeme und Multimediaanwendungen stattgefunden. Die ausgeprägte Kostensensitivität dieser Märkte in Verbindung mit strengen Zeitschranken, denen Realzeitanwendungen unterliegen, haben zur Entwicklung spezialisierter, irregulärer Hardwarearchitekturen geführt. Diese werden speziell zur effizienten Ausführung von Algorithmen der digitalen Signalverarbeitung entworfen. Auf dem Gebiet der Allzweckprozessoren hat die Compilertechnologie eine hohe Reife erreicht. Für irreguläre Architekturen jedoch ist die von traditionellen Hochsprachencompilern erzeugte Codequalität in der Regel nicht ausreichend. Die Erzeugung effizienten Maschinencodes für irreguläre Architekturen erfordert hochoptimierende Techniken, die an spezielle Hardwareeigenschaften des Zielprozessors angepaßt sein müssen. Da solche Verfahren in Standardcompilern üblicherweise nicht eingesetzt werden, werden viele Anwendungen der digitalen Signalverarbeitung in Assembler programmiert. Aufgrund der steigenden Komplexität typischer Anwendungsprogramme und der schrumpfenden Produktzyklen eingebetteter Prozessoren wird dies jedoch zunehmend inakzeptabel. Daher besteht ein dringender Bedarf an retargierbaren Codeerzeugungs- und -optimierungstechniken, die schnell an unterschiedliche Zielarchitekturen angepaßt werden können und in der Lage sind, eine hohe Codequalität zu erreichen.

In der vorliegenden Arbeit wird das Propan-System als ein retargierbares System für hochleistungsfähige Codeoptimierungen und maschinenabhängige Programmanalysen auf Assemblerebene vorgestellt. In der Vergangenheit hat sich die Forschung im Bereich retargierbarer Techniken hauptsächlich auf geschlossene Ubersetzungssysteme konzentriert. Der industrielle Einsatz solcher Systeme impliziert jedoch in der Regel einen Austausch der Compilerinfrastruktur, was mit hohen Kosten verbunden ist. Daher sind retargierbare Compiler in der Industrie kaum anzutreffen. Unserer Kenntnis nach ist Propan das erste postpass-orientierte System, das die Ziele leichter Retargierbarkeit und suchbasierter Codeoptimierungstechniken kombiniert. Aufgrund der Postpassorientierung kann Propan mit geringem Aufwand in existierende Toolketten integriert werden und ermöglicht die Verbesserung der Codequalität existierender Compiler. Dadurch werden die mit dem Austausch der Compilerinfrastruktur verbundenen Kosten vermieden. Das Retargierbarkeitskonzept von Propan beruht auf der Kombination generischer und generativer Techniken. Im Rahmen dieser Arbeit wird eine neue Maschinenbeschreibungssprache, TDL, vorgestellt, die die Spezifikation der Hardwareressourcen eines Zielprozessors, seines Instruktionssatzes und der verwendeten Assemblersprache in kurzer und prägnanter Form ermöglicht. Abgesehen von der Assemblerorientierung besteht die wichtigste Innovation von TDL in der generischen Modellierung irregulärer Hardwareeigenschaften, die es ermöglicht, diese in generischen suchbasierten Optimierungsalgorithmen zu berücksichtigen. Aus der TDL-Beschreibung wird ein Parser für die spezifizierte Assemblersprache und eine Architekturdatenbank in Form von ANSI-C Dateien generiert. Darin werden Datenstrukturen definiert, in denen alle relevanten Informationen über die Zielarchitektur repräsentiert sind sowie Funktionen zum Zugriff, zur Initialisierung und zur Manipulation dieser Datenstrukturen. Das Kernsystem von Propan ist generisch, d. h. maschinenunabhängig implementiert. Werden architekturspezifische Informationen benötigt, wird die generierte Architekturdatenbank referenziert. Für jede Zielarchitektur wird die Architekturdatenbank mit dem generischen Kernsystem zusammengelinkt und es ergibt sich ein spezieller hardwaresensitiver Postpassoptimierer.

Zur Erzeugung einer hohen Codequalität für irreguläre Architekturen ist die Berücksichtigung des Phasenkopplungsproblems erforderlich. Im allgemeinen wird der Codeerzeugungsprozeß in verschiedene Teilaufgaben untergliedert. Aus Komplexitätsgründen werden diese üblicherweise getrennt voneinander durch heuristische Verfahren gelöst. Die Codequalität der heuristischen Verfahren ist für reguläre Architekturen in der Regel ausreichend. Bei irregulären Architekturen jedoch kann es aufgrund der suboptimalen Kombination suboptimaler Teillösungen zur Erzeugung ineffizienten Maschinencodes kommen. In der vorliegenden Arbeit wird ein neuer Ansatz vorgestellt, der verschiedene Teilaufgaben der Codeerzeugung auf Assemblerebene vereinigt. Die Verwendung ganzzahliger linearer Programmierung ermöglicht eine generische homogene Modellierung des Problems der phasengekoppelten Codeoptimierung unter Berücksichtigung irregulärer Hardwareeigenschaften der jeweiligen Zielarchitektur. Die Theorie der ganzzahligen linearen Programmierung hat zu hochentwickelten Lösungstechniken geführt, so daß leistungsfähige Tools zum Lösen ganzzahliger linearer Programme verfügbar sind. Im Rahmen dieser Arbeit werden Erweiterungen zweier strukturierter ILP-Formulierungen für phasengekoppelte Instruktionsanordnung, Registerzuteilung und Ressourcenallokation vorgestellt. Die Struktur beider ILP-Formulierungen wird untersucht und der Zusammenhang zwischen ILP-Modellierung und Hardwareentwurf der Zielarchitektur herausgestellt. Eine Formulierung basiert auf einer reihenfolge-bezogenen Indizierung. Sie ermöglicht eine effiziente Modellierung des Registerzuteilungsproblems und ist besonders für Architekturen mit eingeschränkten Parallelverarbeitungskapazitäten geeignet. Die andere Formulierung verwendet eine zeitpunktbezogene Modellierung. Sie erlaubt eine effiziente Koppelung von Instruktionsanordnung und Ressourcenallokation und ist für Architekturen mit einer großen Anzahl alternativer funktionaler Einheiten geeignet. Im Gegensatz zu früheren exakten phasengekoppelten Codeerzeugungsverfahren sind die in dieser Arbeit vorgestellten Optimierungen nicht auf Basisblockgrenzen beschränkt. Ein weiterer Schwerpunkt liegt auf der Entwicklung ILP-basierter Approximationen durch die

die Berechnungen beschleunigt werden können. Die erzeugten ganzzahligen linearen Programme können somit entweder exakt gelöst werden, wodurch beweisbar optimale Ergebnisse erzielt werden, oder durch Einsatz der approximativen Techniken. Die Grundidee der Approximationen besteht in der schrittweisen Lösung partieller Relaxationen des Originalproblems. Sie erlauben eine deutliche Reduktion der Berechnungszeit und erzielen dennoch eine sehr hohe Codequalität.

Das Propan System wurde für verschiedene repräsentative Standardprozessoren retargiert. Es wurde zur Erzeugung ILP-basierter Postpassoptimierer für zwei moderne digitale Signalprozessoren mit sehr unterschiedlichen Architektureigenschaften eingesetzt, den Analog Devices ADSP-2106x SHARC [Ana95] und den Philips TriMedia TM1000 [Phi97]. Propan kann auch als Plattform für generische Programmanalysen und benutzerdefinierte hardwareabhängige Programmoptimierungen eingesetzt werden. Propan ist in ein System zur Berechnung von Laufzeitgarantien in Realzeitsystemen integriert [FKL<sup>+</sup>99]; in diesem Zusammenhang wurde eine TDL-Beschreibung des Infineon TriCore  $\mu$ C/DSP [Inf00] entwickelt. Für die Infineon C16x-Mikroprozessorfamilie [Sie96] wurde Propan als Ausgangsbasis zur Implementierung hardwaresensitiver Postpassoptimierungen eingesetzt, die Teil eines kommerziellen Postpassoptimierers sind [Abs00a]. Verschiedene Aspekte dieser Arbeit wurden in einer Reihe von Veröffentlichungen vorgestellt [KL98, KL99, Käs99a, KW99, FKL<sup>+</sup>99, Käs00a, Käs00b].

# **Acknowledgements**

I would like to thank my advisor Prof. Dr. Reinhard Wilhelm for his invaluable advice and his guidance and support throughout my course of graduate study. His comments often unveiled new interesting aspects and perspectives. He always left me a lot of freedom and contributed much to an enjoyable and productive working atmosphere.

I like to thank Christian Ferdinand for his advice and many fruitful suggestions and comments. This work has greatly benefited from his insight and experience. The implementation uses several modules developed by Marc Langenbach; special thanks goes to him for years of excellent cooperation, the pleasant and productive working atmosphere, and many stimulating discussions. For careful proof reading of this thesis in different stages I thank Reinhold Heckmann, Marc Langenbach, Christian Ferdinand, Stephan Diehl, Friedrich Eisenbrand and Florian Martin.

I thank Henrik Theiling for adapting his control flow reconstruction algorithm to the assembly setting. I am also grateful to Nicolas Fritz and Stephan Wilhelm who were the first users of the Propan system. They suffered through several bugs and shortcomings and their comments helped improving the system. A word of thanks also goes to Steven Bashford for interesting discussions and to all members of the chair of programming languages and compiler construction for the inspiring and cooperative working atmosphere.

Also, I wish to thank the Deutsche Forschungsgemeinschaft for supporting this research by a graduate fellowship in the Graduiertenkolleg "Effizienz und Komplexität von Algorithmen und Rechenanlagen" at Saarland University.

I would like to thank Prof. Dr. Kurt Mehlhorn and the Max Planck Institute for Informatik of Saarbrücken for granting access to their CPLEX installation and their compute server. I gratefully acknowledge the support of Hans Rieder from the Fraunhofer IZFP who made available the g21k compiler for the SHARC and provided industry-relevant hand-crafted assembly programs for the experimental evaluation. I like to thank the Philips research group Eindhoven, especially Joachim Trescher and Zbigniew Chamski, for making available the Philips tmcc compiler and the development environment for the TM1000.

Finally I would like to thank my parents Hans-Dieter and Josefa and my girl-friend Sylvie for their patience and their support.

# **Contents**

| 1. | Intro | oduction                                           | 1              |

|----|-------|----------------------------------------------------|----------------|

|    | 1.1.  | The PROPAN System                                  | 3              |

|    | 1.2.  | Overview of this thesis                            | 6              |

| 2. | The   | Code Generation Problem                            | 7              |

|    | 2.1.  | Fundamental Program Representations                | 8              |

|    | 2.2.  | The Code Generation Phases                         | 13             |

|    |       | 2.2.1. Code Selection                              | 13             |

|    |       | 2.2.2. Register Allocation and Assignment          | 14             |

|    |       | 2.2.3. Instruction Scheduling                      | 15             |

|    |       | 2.2.4. The Phase Coupling Problem                  | 17             |

|    | 2.3.  | Code Generation for Embedded Processors            | 18             |

|    |       | 2.3.1. Code Generation for Irregular Architectures | 19             |

|    |       | 2.3.2. Retargetable Code Generation                | 20             |

| 3. | A CI  | lassification of Microprocessors                   | 23             |

|    | 3.1.  | •                                                  | $\frac{1}{27}$ |

|    |       | Characteristics of Digital Signal Processors       | 28             |

| 4. | A SI  | hort Introduction to Integer Linear Programming    | 31             |

|    |       | General Overview                                   | 31             |

|    | 4 2   |                                                    | 32             |

|    | 1.2.  | 4.2.1. The Theory of Linear Programming            | 33             |

|    |       | 4.2.2. The Theory of Integer Linear Programming    | 35             |

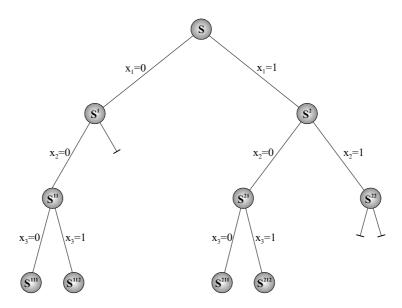

|    | 4.3.  | The Branch-And-Bound Algorithm                     | 39             |

|    |       |                                                    |                |

| 5. |       | Models for the Code Generation Problem             | 45             |

|    |       | Basic Definitions                                  | 47             |

|    | 5.2.  | The SILP Model                                     | 49             |

|    |       | 5.2.1. Basic Formulation                           | 49             |

|    |       | 5.2.2. Integration of Register Assignment          | 55             |

|    |       | 5.2.3. The Structure of the SILP Polytope          | 57             |

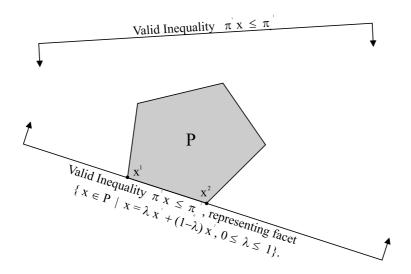

|    |       | 5.2.4. Valid Inequalities                          | 61             |

|    |       | 5.2.5. Complexity                                  | 61             |

|    | 5.3   | The OASIC Model                                    | 62             |

## Contents

|     |      | 5.3.1. Basic Formulation                        | 3 |

|-----|------|-------------------------------------------------|---|

|     |      | 5.3.2. Integrating Register Assignment          | 1 |

|     |      | 5.3.3. The Structure of the OASIC Polytope      | 2 |

|     |      | 5.3.4. Complexity                               | 5 |

|     | 5.4. | Control Flow Modelling                          | õ |

|     |      | 5.4.1. Modelling Disjunctive Constraints        | ĉ |

|     |      | 5.4.2. Representing the Control Flow Structure  | 7 |

|     | 5.5. | ILP Models and Hardware Architectures           | 9 |

| 6.  | ILP- | Based Approximation Techniques 81               | 1 |

|     | 6.1. |                                                 | 2 |

|     | 6.2. |                                                 | 4 |

|     |      | 6.2.1. Stepwise Approximation                   | 4 |

|     |      | 6.2.2. Isolated Flow Analysis                   | 7 |

|     |      | 6.2.3. Stepwise Approximation of Isolated Flows | 3 |

|     |      | 6.2.4. Approximation of Isolated Operations     |   |

|     | 6.3. | Approximations for the OASIC Formulation        |   |

| 7   | Sun  | erblock-Based Code Optimisation 95              | 5 |

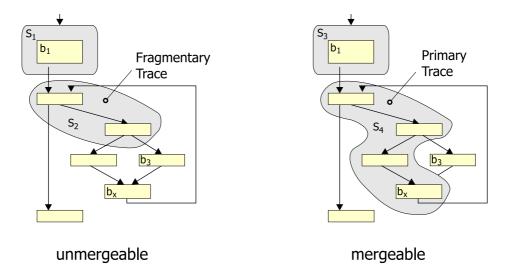

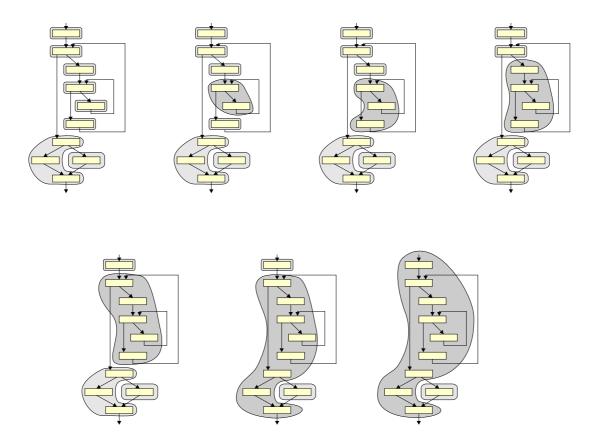

| • • | -    | The Superblock Graph                            |   |

|     | 1.1. | 7.1.1. Superblock Covering                      |   |

|     |      | 7.1.2. Superblock Merging                       |   |

|     |      | 7.1.3. Partitioning                             |   |

|     | 7.2. | The Global Register Assignment Problem          |   |

|     | 1.4. | 7.2.1. Global Heterogeneous Register Renaming   |   |

|     |      | 7.2.2. Virtual Registers and Abstract Resources |   |

|     |      | 7.2.3. Virtual Definitions and Virtual Uses     |   |

|     |      | 7.2.4. Global Lifetime Modelling                |   |

|     | 7.3. | Global Timing Constraints                       |   |

|     | 1.5. | 7.3.1. Inter-Iteration Data Dependences         |   |

|     |      | <u>-</u>                                        |   |

|     | 7.4. |                                                 |   |

|     | 1.4. | 7.4.1. Timing Synchronisation                   |   |

|     |      |                                                 |   |

|     |      | <i>v</i>                                        |   |

|     | 7.5. | 7.4.3. Resource Synchronisation                 |   |

| _   |      |                                                 |   |

| 8.  |      | Target Description Language TDL 137             |   |

|     | 8.1. | Related Work                                    |   |

|     | 8.2. | The Resource Specification                      |   |

|     | 8.3. | The Specification of the Instruction Set        |   |

|     | 0.4  | 8.3.1. The Specification of the Semantics       |   |

|     | 8.4. | The Constraint Section                          |   |

|     |      | 8.4.1. Generating Integer Linear Constraints    | 3 |

|            | 8.5.         | 8.4.2. Generating Support Functions for List Scheduling         |          |

|------------|--------------|-----------------------------------------------------------------|----------|

| ^          |              |                                                                 |          |

| 9.         |              | Implementation of the PROPAN Framework16The Structure of PROPAN | _        |

|            |              | Computing the Program Representations                           |          |

|            | <i>3.</i> ∠. | 9.2.1. The Control Flow Graph                                   |          |

|            |              | 9.2.2. The Data Dependence Graph                                |          |

|            |              | 9.2.3. The Control Dependence Graph                             |          |

|            | 9.3.         | Generic List Scheduling and Resource Allocation                 |          |

|            |              | Computing the ASAP and ALAP Control Steps                       |          |

|            |              | The Optimisation Interface                                      |          |

| 10         | .Expe        | erimental Results 18                                            | 3        |

|            | •            | Analog Devices ADSP-2106x SHARC                                 | 34       |

|            |              | 10.1.1. Architecture                                            |          |

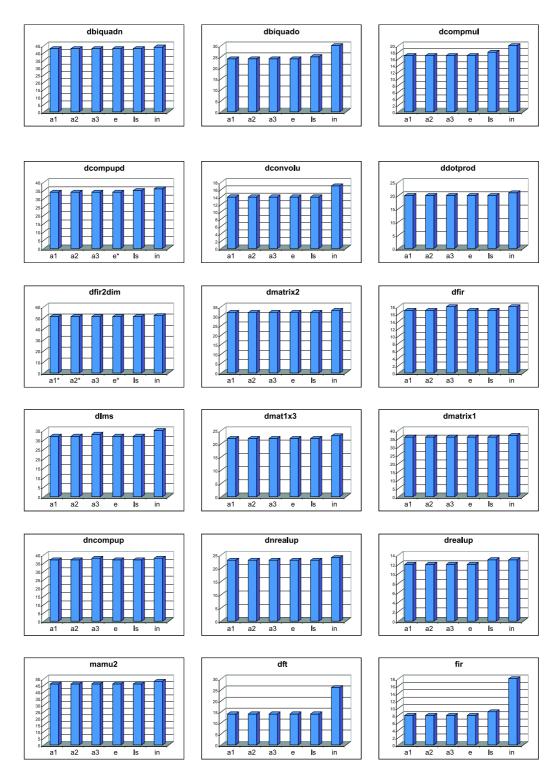

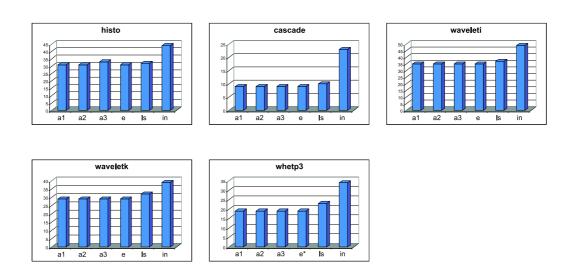

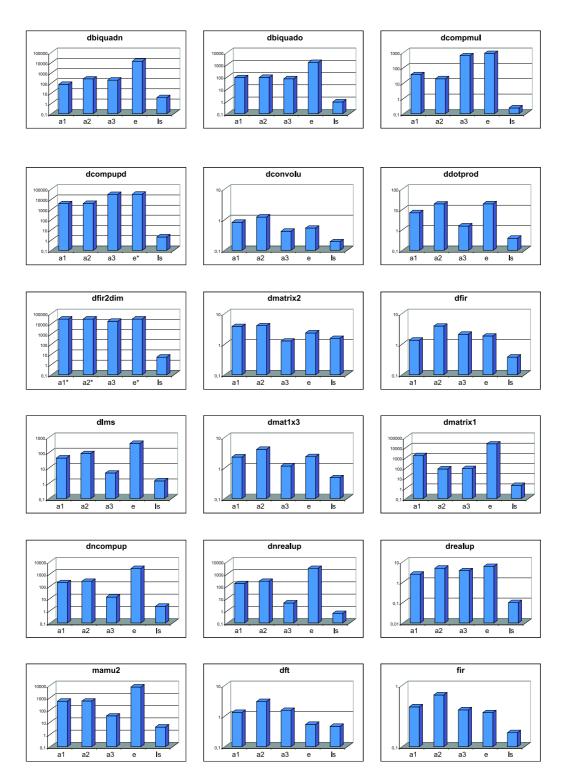

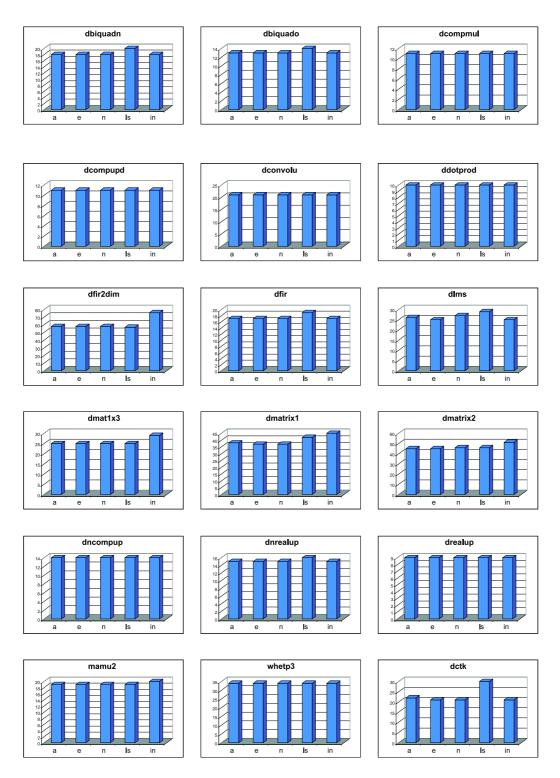

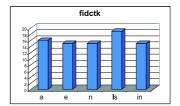

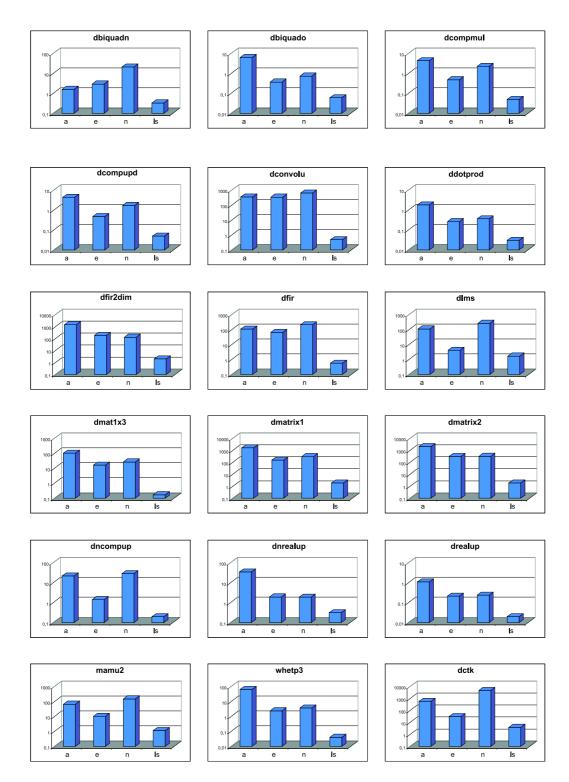

|            |              | 10.1.2. Performance of the Optimiser                            | 36       |

|            | 10.2.        | Philips TriMedia TM1000                                         |          |

|            |              | 10.2.1. Architecture                                            | )()      |

|            |              | 10.2.2. Performance of the Optimisers                           | )1       |

|            | 10.3.        | Summary                                                         | .7       |

| 11         | . Rela       | ted Work 22                                                     | <b>1</b> |

|            | 11.1.        | Retargetable Code Generation                                    | 21       |

|            |              | Heuristic Phase Coupling                                        |          |

|            | 11.3.        | Search-Based Methods in Code Generation                         | 28       |

| 12         | .Con         | clusion and Outlook 23                                          | 3        |

| 13         | . List       | of Symbols 23                                                   | 5        |

| Λ          | Δnn          | endix 23                                                        | ·7       |

| <b>~</b> : |              | Instruction Set of the SHARC                                    | -        |

|            | 11.1.        | A.1.1. Notation                                                 |          |

|            |              | A.1.2. Instruction Formats                                      |          |

|            |              | A.1.3. Compute Operations                                       |          |

|            | A.2          | Excerpts from the TDL Specification of the SHARC                |          |

|            |              | Instruction Set of the TM1000                                   |          |

|            |              | Excerpts from the TDL Specification of the TM1000               |          |

# 1. Introduction

During the last years, the markets for telecommunication, embedded systems, and multimedia applications have been rapidly growing. The distinct cost sensitivity of those markets in connection with the stringent time constraints of real-time applications have led to the development of specialised, irregular hardware architectures designed to efficiently execute typical applications of digital signal processing. Common characteristics of those architectures are, e.g., heterogeneous register files, support for low-overhead looping, and restricted interconnectivity of functional units and register sets. In the area of general-purpose processors, compiler technology has reached a high level of maturity. For irregular architectures however, the code quality achieved by traditional high-level language compilers often is not satisfactory [SCL96, ZVSM94]. Generating efficient code for irregular architectures requires highly optimising techniques which have to be aware of specific hardware features of the target processor. Since such techniques are usually not provided by standard compilers, many digital signal processing applications are developed in assembly language [SCL96]. Assembly programming is a time consuming and error-prone task that suffers from bad portability and bad maintainability thus reducing the productivity of software development. Due to the increasing complexity of embedded applications and the shrinking design cycles of embedded processors, the usage of high-level programming languages becomes more and more imperative. As a consequence a growing demand for compilation techniques that can produce high-quality code for irregular architectures has risen.

Most digital signal processors dispose of special functionality; identifying special functionality however requires bringing much architectural information into the compiler. Developing a dedicated compiler for each processor is prohibitive due to the short design cycles and the cost sensitivity of the embedded markets. Thus retargetable code generation and optimisation techniques that can be quickly adapted to different target architectures and are able to generate high-quality code for each individual target have become an active area of research [MG95].

The process of generating code for high-level language programs can be subdivided into several phases: code selection, register allocation, instruction scheduling, register assignment, and functional unit binding. Since most of these subtasks are NP-complete problems, in classical code generation methods they are addressed in separate phases by heuristic algorithms. Unfortunately the code generation phases are interdependent; decisions made in one phase impose constraints to the subsequently addressed phases. For regular architectures the quality of the classical

#### 1. Introduction

heuristic methods is satisfactory. For irregular architectures however the interdependencies between the phases usually lead to a significant decrease of code quality [ZSWS95] due to the suboptimal combination of suboptimal partial results. In heuristic phase-coupling methods a heuristic algorithm for one code generation phase typically is extended to address other subtasks based on heuristic estimates of the phase interactions. As a consequence the quality of the generated code strongly depends on the choice of the heuristics. The quality of the individual heuristics and their combined effects in turn strongly depend on the target architecture. Thus there is a conflict between the goals of retargetability and heuristic generation of high-quality code.

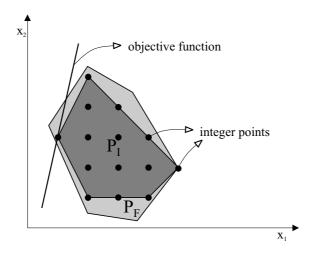

Search-based techniques such as integer linear programming allow to model the interactions of code generation phases in an exact way. In the last decade, the use of integer programming models has increased significantly which is mostly due to the advances in algorithms for solving integer programs and the availability of reliable software packages [JNS97]. Computing an optimal solution of an integer linear program is NP-complete [GJ79]. Nevertheless many large instances of such problems can be solved. Recent research has lead to an understanding of polyhedral properties that can be used to develop well-structured formulations permitting efficient computations [CWM94, Bal98]. Other advances have made it possible to improve the efficiency of ILP solving techniques by curtailing the necessary enumeration process [JNS97, Eis00]. The use of integer linear programming for phase-coupled code generation however is still rare.

Although during the last years several retargetable research compilers have been developed they are rarely used in industry. To the best of our knowledge the only commercially available retargetable compiler developed for embedded systems is the CHESS compiler [LVPK<sup>+</sup>95]. One reason is the problem of simultaneously realizing the goals of retargetability and of generating high-quality code. Another reason is that using such a system in industry mostly requires replacing the existing compiler infrastructure which causes high costs. Therefore postpass techniques are a very attractive solution since they allow to improve the quality of previously generated machine or assembly code without requiring to change the complete compilation system. The legacy compiler can be kept and yet the efficiency of the generated software is increased leading to a large cost benefit. Another advantage of postpass methods is that they make optimisations of compiler-intrinsic functions possible. Compiler-intrinsic functions are often used to embed manually written assembly code into high-level language programs. For high-level language compilers they usually represent barriers across which no program optimisation is possible. However this does not concern postpass approaches since they work on machine level anyway. Moreover the machine level is a natural stage for optimisations aiming at exploiting hardware-specific functionality of digital signal processors. Previous studies [KL99] and industrial experience [Abs00a] have shown that postpass methods can be integrated into existing tool chains with moderate effort.

In embedded systems, the software often has to meet specific requirements which necessitate complex program analyses. In real-time systems, e.g., it must be

guaranteed that tight time constraints will be met by every execution of a program. The calculation of tight time bounds for modern architectures is impeded by the use of caches and pipelines. The consequence is that hardware-dependent program analyses have to be performed which—as e.g. the static cache behaviour prediction of [Fer97]—are necessarily postpass analyses. The results of such analyses can also be used for program optimisations, e.g. by cache-sensitive task scheduling algorithms [KT98, KT99].

## 1.1. The PROPAN System

Our contribution to this situation is the Propan system (*Postpass-oriented Retargetable OPtimiser and ANalyser*) that has been designed as a retargetable framework for postpass optimisations and analyses. To the best of our knowledge, Propan is the first system where the issues of machine description driven retargetability and of search-based postpass optimisations have been combined.

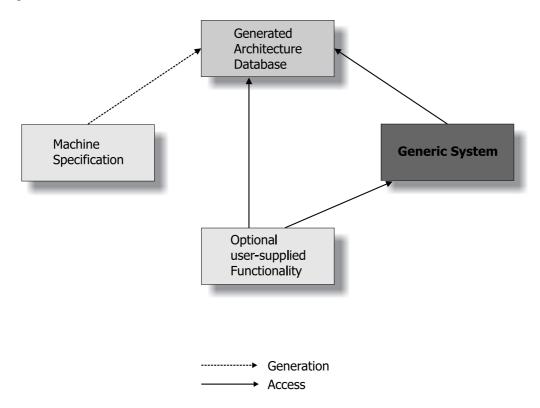

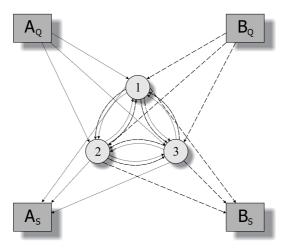

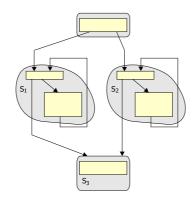

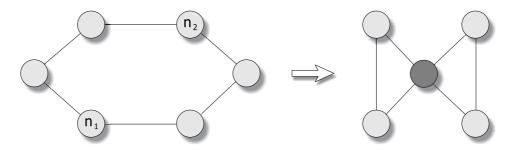

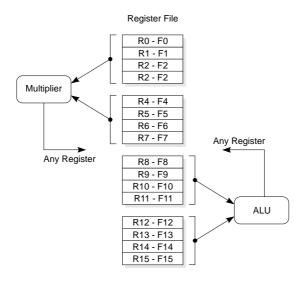

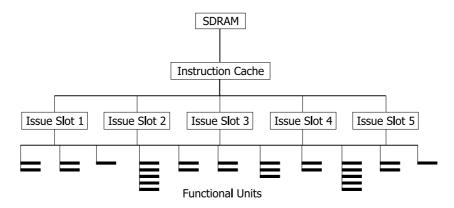

Figure 1.1.: The retargetability concept.

The retargetability concept of Propan is based on the combination of generic and generative techniques. An illustration is given in Fig. 1.1 in an abstract form. The core system is composed from generic and generated program parts. Generic program parts are independent from the target architecture and can be used for different processors without any modification. If hardware-specific knowledge is

#### 1. Introduction

required all information is retrieved in a standardised way from an architecture 'database' that is generated from a central machine description. The program parts that change with the specific target architecture are automatically generated from the machine description. Thus retargeting the system to a different architecture only requires an appropriate specification of the target machine. Additionally the integration of user-supplied functionality is supported. This may include dedicated program analyses or hardware-specific program transformations. Those external program parts can communicate with the core system via a well-defined file interface and can access the architecture database generated from the machine description.

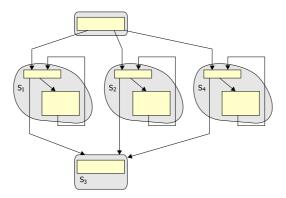

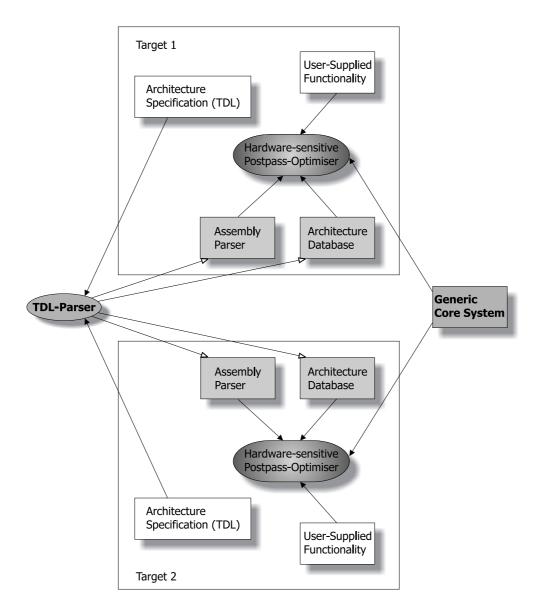

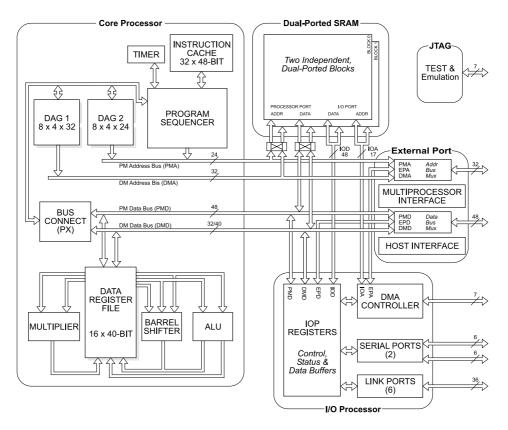

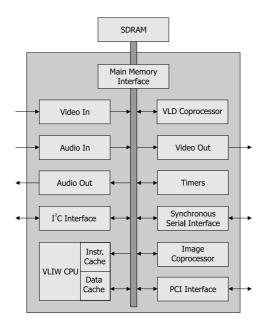

A detailed overview of the Propan framework is shown in Fig. 1.2. The input of Propan consists of a TDL-description of the target machine and of the assembly programs that are to be analysed or optimised. TDL (Target Description Language) is a dedicated machine description language that allows to specify the hardware resources of the target processor, its instruction set, the assembly language and irregular hardware constraints. Apart from the assembly orientation the main innovation of TDL is the generic modelling of the irregular hardware constraints that allows them to be exploited in generic search-based optimisation algorithms. The TDL specification is processed once for each target architecture; from the TDL description a parser for the specified assembly language and an architecture database are generated. The architecture database consists of a set of ANSI-C files where data structures representing all specified information about the target architecture and functions to initialise, access and manipulate them are defined. The core system of Propan is generic; if hardware-specific knowledge is required the architecture database is referenced. For each target architecture, the generic core system is linked with the generated files yielding a dedicated hardware-sensitive postpass optimiser.

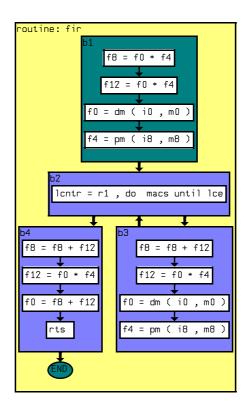

The parser reads the input programs and computes their control flow graphs that are represented in a generic intermediate language called CRL (Control Flow Representation Language) [Lan99]. The input format is not restricted to assembly files; it is also possible to specify the output format of disassemblers reading executable files, or textual representations of compiler-specific intermediate formats. The CRL interface serves as the main interface for all optimisation and analysis algorithms including additional user-supplied algorithms. From the control flow graph, the necessary program representations as, e.g., the data dependence and the control dependence graphs are calculated by generic algorithms. If required, a register renaming algorithm is executed that replaces references to physical registers of the input program by references to virtual registers. This way spurious data dependences limiting the available parallelism are removed.

The central part of the Propan system is the modelling of phase-coupled code optimisation by integer linear programming. A set of fundamental code generation subtasks is identified that can still be addressed on assembly level and phase-coupling methods are investigated that allow to compute high-quality solutions in a generic way without the necessity of reimplementing parts of the source code. In-

#### Generic computation of program representations Generation of integer linear programs Generic annotated Input program Assembly supporting phase-coupled instruction control flow graph (assembly code) scheduling, register assignment and parser (CRL) functional unit binding. TDL-specification of TDL-parser the target machine Evaluation of ILP solver (CPLEX) MILP solution Assembly Optimised assembly file reconstruction

The PROPAN System

#### Figure 1.2.: The PROPAN system.

Architecture database: target-specific data structures and functions (ANSI-C)

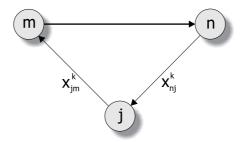

teger linear programming allows a homogeneous problem description that can fully integrate the tasks of instruction scheduling, register reassignment, and functional unit binding, or subsets thereof. Our approach is based on two well-structured ILP models developed in the area of architectural synthesis [GE92, GE93, Zha96]. We have adapted those models to the postpass optimisation problem and extended them to incorporate irregular hardware characteristics and exceed basic block boundaries. Among those models, the most appropriate formulation can be chosen individually for each target architecture. For each input program a dedicated integer linear program is generated that models the execution of the program on the specified target architecture<sup>1</sup>. In contrast to most previous approaches for search-based code generation the optimisation scope is not restricted to basic blocks. A novel superblock concept allows to extend the optimisation scope across basic block and loop boundaries. For each superblock, an individual integer linear program is generated.

Since integer linear programming is an NP-complete problem, the time for computing a provably optimal solution can grow high for large input programs. Therefore a set of ILP-based approximations has been developed that can reduce the computation time significantly and still obtain high-quality solutions. The basic idea of the ILP-based approximations is the iterative solution of heuristically

<sup>&</sup>lt;sup>1</sup>The incorporation of the register assignment task however can be considered promising only for the SILP formulation (see Chap. 5).

#### 1. Introduction

determined relaxations of the original problem. In the last step of the optimisation process the solutions of the integer linear programs are evaluated and the optimised assembly file is generated.

### 1.2. Overview of this thesis

In the next chapter an overview of code generation and optimisation is given. The fundamental code generation phases are introduced and the problem of code generation for irregular architectures is illustrated. Chap. 3 gives a classification of modern microprocessors that focuses on design characteristics and application areas of digital signal processors as one class of processors characterised by irregular architectures. Chap. 4 gives a short introduction into integer linear programming where the most important mathematical concepts required for the scope of this thesis are summarised. The ILP models used for code generation are presented in Chap. 5. Proofs of important properties of their polytope structure are given, the incorporation of the control flow structure of programs is described and the dependence between ILP modelling styles and hardware architectures is pointed out. In Chap. 6 novel ILP-based approximations are presented that allow to reduce the computation time while still retaining a high solution quality. Chap. 7 is dedicated to the superblock mechanism that allows to extend the optimisation scope across basic block boundaries. After the definition of the underlying concepts, the required extensions of the ILP models are presented and evaluated. In Chap. 8 the hardware description language TDL is presented in detail. Special attention is paid to the generation of integer linear constraints from a specification of architectural irregularities in the form of logical conditions. Implementation details of the Propan system are presented in Chap. 9. An overview of the modelled architectures is given in Chap. 10, followed by the evaluation of our experimental analyses.

Surveys of relevant publications specifically related to individual chapters of this thesis are given at the beginning of the corresponding chapters. A separated survey of retargetable compilation systems and of code generation and optimisation frameworks for irregular architectures is given in Chap. 11.

Finally, Chap. 12 concludes and gives an outlook to future research. The appendix contains a summary of the instruction sets of the Analog Devices Additional Sharc and the Philips TriMedia TM1000, together with excerpts from their Tdl specifications. A list of symbols is given at the end of this thesis.

# 2. The Code Generation Problem

Compilers for high-level programming languages aim at transforming input programs written in a certain source language into a semantically equivalent program in some target language, usually the machine or assembly code of a target processor. Conceptually, the process of compiling can be subdivided into several phases. In an initial phase, often called the compiler frontend, the syntactic structure and static semantic properties of the source program are computed. The results of this phase comprise either messages about syntactic or semantic errors in the program or an appropriate representation of the syntactic structure and the static semantic properties of the program. Subsequently many compilers perform efficiencyincreasing program transformations on this representation that, to a large degree, are machine independent. This includes tasks like constant folding, elimination of common subexpressions, elimination of dead code, loop-invariant code motion, etc. The corresponding phase is often called the middle-end of the compiler. Then a synthesis phase takes the intermediate representation produced by the middle-end and converts it into semantically equivalent target machine code. An important part of the synthesis phase is the task of code generation which consists of several subtasks:

- The goal of *code selection* is to map the intermediate representation to a semantically equivalent sequence of machine operations.

- The task of register allocation is to map the values of the intermediate representation to physical registers in order to minimise the number of memory references during program execution. It consists itself of two subtasks: Register allocation proper attempts to decide which variables and expressions of the intermediate representation are mapped to registers and which ones are kept in memory. The second subtask is called register assignment; its goal is to determine the physical registers that are used to store the values that have been previously selected to reside in registers.

- Instruction scheduling is the task of reordering the produced instruction stream in order to minimise pipeline stalls and to exploit the available instruction-level parallelism.

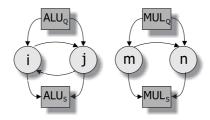

- Resource allocation is concerned with binding operations to machine resources, e.g. functional units or buses; it is also called functional unit binding.

This task is only relevant for architectures where operations can be explicitly assigned to functional units and where the binding can impose constraints to register assignment and instruction scheduling.

All code generation tasks have high worst case complexity; in general, code selection, register allocation, register assignment and instruction scheduling are NP-complete [GJ79] problems. Therefore, traditional code generation approaches rely on heuristic methods. Furthermore, a modular decomposition of code generation is advisable for reasons of software complexity. Thus in traditional approaches all code generation phases are addressed isolatedly by separate algorithms. Unfortunately this can lead to a suboptimal combination of suboptimal partial solutions resulting in a very poor code quality, especially for irregular architectures.

The remainder of this chapter is organised as follows: in Sec. 2.1 an overview of the fundamental program representations is given that are computed from the intermediate representation of the program and constitute the input of most subtasks of code generation. Subsequently the individual code generation phases are presented in more detail and the phase coupling problem is described. In Sec. 2.3, the problems associated with the compilation for irregular architectures and their consequences to the code generation process are summarised.

# 2.1. Fundamental Program Representations

The program representations introduced in this chapter can be defined either on source level, or on machine level. For the scope of this thesis it is more convenient to choose the machine-level representations. Therefore, it is necessary to introduce the concept of machine operations. In the terminology of [LDS80, Bas95] a microoperation, or machine operation, is an elementary operation that can be executed by the target processor. The notion of machine operation has to be distinguished from the concept of machine instructions. In some architectures exhibiting intraprocessor parallelism, especially in VLIW<sup>1</sup> architectures, several machine operations can be combined to form one machine instruction. The execution of all operations contained in the same instruction is started in parallel. In the following a short summary of the most important concepts is given; more detailed explanations and additional literature references can be found in [WM95, Bas95].

The control flow graph of a procedure indicates which instructions can be executed one after the other. Whether this actually occurs during program execution may depend on conditions which in general cannot be evaluated at compilation time.

**Definition 2.1 (Control Flow Graph)** The control flow graph of a procedure is a directed graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  with node and edge labels. For each instruction i of the procedure there is a node  $n_i \in N_C$  that is marked by i. The edges

<sup>&</sup>lt;sup>1</sup>Very Long Instruction Word

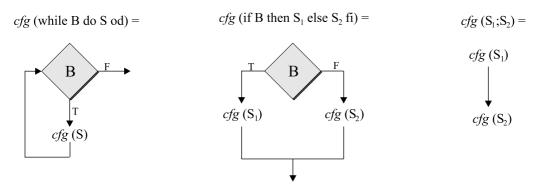

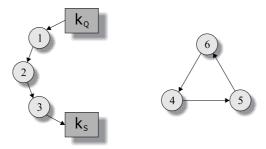

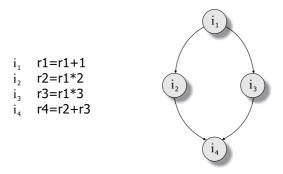

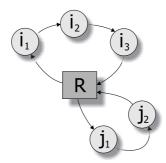

$(n, m, \lambda)$  denote the control flow of the procedure;  $\lambda \in \{T, F, \epsilon\}$  is the edge label. The subgraphs representing loops, conditional branches and sequential program flow are shown in Fig. 2.1. Edges belonging to unconditional branches lead from the

Figure 2.1.: Control flow graph for composed statements. A subgraph  $G'_C = (N'_C, E'_C, n'_A, n'_\Omega)$  is inserted as follows: All incoming edges lead to  $n'_A$ , all outgoing edges to the successor node uniquely determined by the execution context.

node of the branch to the branch destination. The node  $n_A \in N_C$  is the uniquely determined entry point into the procedure; it belongs to the first instruction to be executed.  $n_{\Omega}$  denotes the end node that is reached by any path through the control flow graph. Nodes with more than one predecessor are called joins and nodes with more than one successor are called forks.

**Definition 2.2 (Path)** A path  $\pi$  from node  $n_1$  to node  $n_k$  in a directed graph G = (N, E) is a sequence of edges, beginning with a node  $n_1 \in N$  and ending in  $n_k \in N$  where  $\pi = (n_1, n_2), (n_2, n_3), \ldots, (n_{k-1}, n_k)$  and  $(n_i, n_{i+1}) \in E$  for  $i = 1, \ldots, k-1$ . The length of  $\pi$  is defined as the number of edges on  $\pi$ , i. e.  $l(\pi) = k-1$ .

**Definition 2.3 (Basic Block)** A basic block in a control flow graph is a path of maximal length which has no joins except possibly at the beginning and no forks except possibly at the end.

If the first instruction of a basic block is executed, then in case of error-free execution (no runtime errors, exceptions, etc. ) all other operations of the basic block are executed as well.

**Definition 2.4 (Basic Block Graph)** The basic block graph  $G_B = (N_B, E_B, b_A, b_\Omega)$  of a control flow graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  is formed from  $G_C$  by combining each basic block into a node. Edges of  $G_C$  leading to the first node of a basic block, lead to the node of that basic block in  $G_B$ . Edges of  $G_C$  leaving the last node of a basic block, lead out of the node of that basic block in  $G_B$ . The node  $b_A$  denotes the uniquely determined entry block of the procedure;  $b_\Omega$  denotes the exit block that is reached at the end of any path through the procedure.

#### 2. The Code Generation Problem

When performing global analyses or optimisations the control structure of the procedure has to be taken into account. As an example, moving an operation from the *then*-block of a conditional branch to the *else*-block must be prevented in order to preserve program semantics. The control structure of a procedure is represented by the control dependence graph  $G_{CD}$ . Defining the control dependence graph requires several other definitions to be given first.

**Definition 2.5 (Dominator)** Let a control flow graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  be given. A node  $n \in N_C$  dominates a node  $m \in N_C$ ,  $n \Delta_d m$ , if and only if each path from the entry node  $n_A$  of the procedure to m contains the node n. Each node dominates itself.

**Definition 2.6 (Immediate Dominator)** Let a control flow graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  be given. A node  $n \in N_C$  is an immediate dominator of  $m \in N_C$ , if and only if

- $n \Delta_d m$

- $\exists z : n \Delta_d z \wedge z \Delta_d m \wedge z \neq n \wedge z \neq m$ .

**Definition 2.7 (Dominator Tree)** The dominator tree  $T_d$  of a control flow graph is a tree containing all nodes of the control flow graph  $G_C$ . Its root is the entry node  $n_A$  of the procedure. There is an edge between n and m if and only if n is immediate dominator of m.

**Definition 2.8 (Postdominator)** Let a control flow graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  be given. A node  $n \in N_C$  postdominates a node  $m \in N_C$ ,  $n \Delta_p m$ , if and only if each path from m to  $n_\Omega$  contains the node n. A node never postdominates itself.

**Definition 2.9 (Immediate Postdominator)** Let a control flow graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  be given. A node  $n \in N_C$  is an immediate postdominator of  $m \in N_C$ , if and only if

- $n \Delta_p m$

- $\exists z : n \Delta_p z \wedge z \Delta_p m \wedge z \neq n.$

**Definition 2.10 (Postdominator Tree)** The postdominator tree  $T_p$  of a control flow graph is a tree containing all nodes of the control flow graph  $G_C$ . Its root is the exit node  $n_{\Omega}$  of the procedure. There is an edge between n and m if and only if n is the immediate postdominator of m.

The postdominator tree can be calculated as the dominator tree of the inverse control flow graph; an algorithm is given in [Käs97, ASU86].

**Definition 2.11 (Control Dependence)** Let  $G_C = (N_C, E_C, n_A, n_\Omega)$  be a control flow graph. A node  $n \in N_C$  has control dependence on  $m \in N_C$ ,  $n \delta_c^a m$ , if the following conditions hold:

- 1.  $(n, a, \lambda) \in E_C \text{ where } \lambda \in \{T, F, \epsilon\},\$

- 2. m does not post dominate n,  $\neg(m \Delta_p n)$ , and

- 3. there is a path p = n, a, ..., m, such that for all  $z \in p$  where  $z \neq n$ ,  $z \neq m$  holds:  $m \Delta_p z$ .

A node m is control dependent on n if and only if n  $\delta_c^a$  m.

**Definition 2.12 (Control Dependence Graph)** The control dependence graph  $G_{CD}$  of a control flow graph  $G_C = (N_C, E_C, n_A, n_\Omega)$  is a directed graph  $G_{CD} = (N_{CD}, E_{CD})$  with edge labels, such that  $(n, m, \lambda) \in E_{CD} \Leftrightarrow n \delta_c^a m$  and  $(n, a, \lambda) \in E_C$  and  $\lambda \in \{T, F\}$ .

**Definition 2.13 (Control Equivalence)** Let a control dependence graph  $G_{CD} = (N_{CD}, E_{CD})$  be given. Two nodes  $n_1, n_2 \in N_{CD}$  are control equivalent if they have the same predecessor m in the control dependence graph and the edges  $(m, n_1, \lambda_1)$  and  $(m, n_2, \lambda_2)$  have the same label, i. e.,  $\lambda_1 = \lambda_2$ .

During instruction scheduling the operations of a procedure are reordered with the goal of improving the efficiency of the program. The program semantics must not be changed by the reordering. In order to preserve the program semantics the control dependences must be respected, but additionally also the data dependences of the operations have to be taken into account. Data dependences are determined by the ordering of reading respectively writing accesses to the components of the machine state, as e.g. registers, or memory cells. Writing accesses are termed as definitions, reading accesses as uses. The data dependences of a procedure are represented by the data dependence graph.

**Definition 2.14 (Data Dependence Graph)** Let  $G_C = (N_C, E_C, n_A, n_\Omega)$  be a control flow graph. Its data dependence graph is a directed graph  $G_D = (N_D, E_D)$  with node and edge labels whose nodes are labelled by the operations of the procedure. The set of edges is defined as  $E_D \subseteq N_D \times N_D \times \mathcal{R} \times T$  where  $\mathcal{R}$  denotes the storage resources of the target processor and  $\mathcal{T} = \{t, a, o\}$  denotes the type of the data dependence. An edge runs from the node of an operation i to the node of an operation j, if i has to be executed before j, i. e. if there is a path from i to j in the control flow graph and if

- i defines a resource r, j uses it and the path from i to j does not contain other definitions of r (true dependence):  $(i, j, r, t) \in E_D$

- i uses a resource, j defines it and the path from i to j does not contain any definitions of r (anti dependence):  $(i, j, r, a) \in E_D$

- i and j use the same resource and the path from i to j does not contain any uses nor any definitions of r (output dependence):  $(i, j, r, o) \in E_D$ .

Let  $E_D^t$  denote the set of all true dependences,  $E_D^a$  the set of all anti dependences and  $E_D^o$  the set of all output dependences, then the edge set of the data dependence graph can be rewritten as follows:

$$E_D = E_D^t \cup E_D^a \cup E_D^o.$$

Programs that contain loops must be handled with care, since their data dependence graph may contain cycles. Each data dependence must be classified as loop-carried if the dependence is caused by the repeated execution of a loop body, i.e. the operation instances belong to different loop iterations, or otherwise as loop-independent.

**Definition 2.15 (Loop)** Let a basic block graph  $G_B$  and its dominator tree  $T_d$  be given. A loop  $G_L = (N_L, E_L, h_L)$  is a subgraph of  $G_B$  where  $N_L \subseteq V_G$  and  $E_L \subseteq N_L \times N_L$  such that  $E_L \subseteq E_G$ .  $G_L$  must satisfy two conditions:

- There must be a unique entry point, the loop header  $h_L$ , that dominates all blocks of the loop, i. e.  $h_L \Delta_d b \forall b \in N_L$ .

- There must be at least one path starting from the loop header  $h_L \in E_L$  that leads back to itself.

The edges  $(b, h_L) \in E_L$  are denoted backward edges of  $G_L$ ; all others forward edges. The body of the loop  $G_L$  is defined as  $N_L - \{h_L\}$ .

A loop  $G_{L'}$  is said to enclose another loop  $G_L$ , if  $N_L \subseteq N_{L'}$ . The loop nesting depth  $l_L$  of a loop  $G_L$  is defined to be the number of loops  $G_{L'} \neq G_L$  such that  $G_{L'}$  encloses  $G_L$ . The data dependences are classified as loop-independent or loop-carried with the help of the reduced transitive hull  $G_B^+$  of the basic block graph.

### Definition 2.16 (Reduced Transitive Hull of the Basic Block Graph)

Let the basic block graph  $G_B = (N_B, E_B, b_A, b_\Omega)$  of a procedure be given and let  $E_B^-$  denote the set of all forward edges in  $E_B$ . Then the reduced transitive hull of the basic block graph is defined as  $G_B^+ = (N_B, E_B^+, b_A, b_\Omega)$ . There is an edge (b, g) in  $E_B^+$  if and only if one of the following conditions is met:

- there is a path from b to g in  $E_B^-$ , or

- there is a loop  $G_L = (N_L, E_L, h_L)$  with  $b \in N_L$ ,  $g \notin N_L$  such that there is a path from  $h_L$  to g in  $E_B^-$ .

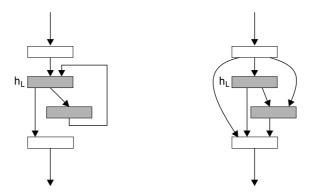

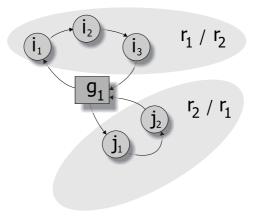

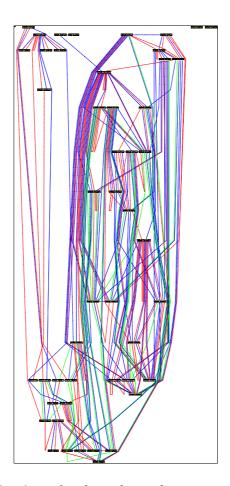

As an illustration, a basic block graph and its reduced transitive hull are shown in Fig. 2.2. The shaded blocks form a loop L whose header is block  $h_L$ .

From the control flow graph  $G_C$  and the reduced transitive hull of the basic block graph, the reduced transitive hull of the control flow graph  $G_C^+$  can be derived. All incoming edges into a block  $b \in G_B$  are represented by edges leading into the first node of  $E_C$  that belongs to b; all outgoing edges of b are represented

Figure 2.2.: A basic block graph and its reduced transitive hull.

by outgoing edges of the node for the last instruction in b. The edges between instructions of the same basic block are the same as in  $G_C$ . Then, each dependence from an operation i to another operation j  $((i, j, r, \tau) \in E_D)$  where the instruction containing i is no predecessor of the instruction containing j in  $G_C^+$  is a loop-carried dependence.

### 2.2. The Code Generation Phases

#### 2.2.1. Code Selection

The input of the code selection phase is the intermediate representation of the input program, typically in the form of expression trees. The implementation of a code selector can be simplified by using code selector generators with appropriate descriptions of the target machine and its correspondence to the intermediate representation. The basic idea of code selector generators can be formalised by the theory of tree parsing and tree automata [FSW94, WM97]. The instruction set of the target machine is described by a regular tree grammar. The right-hand side of a rule describes the meaning of an operation in the form of tree patterns of the intermediate representation. The terminals correspond to the nodes of the intermediate representation, the non-terminals denote storage resources of the target machine. From such a machine grammar, expression trees of the intermediate representation can be derived. The derivation tree of an expression tree describes a semantically equivalent sequence of machine operations. In order to deal with ambiguous machine grammars, the rules are annotated with costs such that among different derivation trees for the same expression tree the cheapest one can be selected. Another theoretical foundation has been given by the theory of term rewriting systems [PL88, Emm92]. Early implementations based on [GG78, Hen84] used LR-parsing techniques driven by a specification of the target machine by a context-free gram-The code selector was generated by a parser generator. The limitation however was that the code selection for ambiguous instruction sets could not be modelled conveniently. A solution of this problem is to combine pattern matching

algorithms with dynamic programming to determine locally optimal operation sequences [AG85, WW89, HD89a] or extend the pattern matcher to directly selecting locally optimal operation sequences [PLG88, HD89b]. Examples for contemporary code generators are BEG [Emm89], Twig [AGT89], iburg [FHP92], and OLIVE [SPA97].

A drawback of the code selection by tree parsing is caused by the necessity of processing expression or syntax trees. If due to common subexpressions, the intermediate representation takes the form of a directed acyclic graph (DAG), usually heuristics are used to break up the DAG into a forest of trees. For architectures with a complex instruction set or with irregular hardware features the independent covering of the expression trees may result in a decrease of code quality [LDKT95]. This is covered in more detail in Sec. 2.2.4.

### 2.2.2. Register Allocation and Assignment

There is a large and continuously increasing gap between the processing speed of the CPU and the memory access time [Fer97]. Therefore the program execution can be accelerated by keeping the largest possible number of values of live program variables and live intermediate results, often called symbolic registers, in fast processor registers. Liveness of a variable or result means that its current value will potentially be needed again later during the program execution. The number of simultaneously live symbolic registers usually exceeds the number of physical registers. Hence, a resource optimisation problem results. Those values should be kept in processor registers that produce the highest benefits for the execution time. Register allocation proper attempts to determine which symbolic registers are mapped to physical registers and which ones are stored in memory. The task of register assignment is to select a particular physical register. For architectures with heterogeneous register files the register assignment problem includes the problem of selecting an appropriate register bank. Often the term register allocation is used to denote both the phases of register allocation proper and register assignment.

The input of the register allocation is an intermediate representation of the program where each operation and each modified variable is associated with a symbolic register. The same physical register must never be assigned to two different symbolic registers if they are simultaneously live and might contain different values. In the following the most important definitions and concepts of register allocation are summarised; a more detailed introduction is given in [WM97].

**Definition 2.17 (live, life range)** A symbolic register r is live at a program point p, if there is a program path from the entry node of the procedure to p that contains a definition of r and there is a path from p to a use of r on which r is not defined. The life range of a symbolic register r is the set of the program points at which r is live.

Definition 2.18 (interference, register interference graph) Two life ranges of symbolic registers interfere, if one of them is defined during the life range of the

other. The register interference graph is an undirected graph whose nodes are life ranges of symbolic registers and whose edges connect the nodes of interfering life ranges.

Typically, register allocation is performed by graph colouring algorithms as presented in [Cha82, CH90]. The problems of register allocation and assignment are translated into the problem of colouring the register interference graph by kcolours where k denotes the number of available physical registers. Different colours must be assigned to directly connected nodes. Since for k > 2 the problem of deciding whether an arbitrary graph can be coloured by k colours is NP-complete, [Cha82, CH90] suggest the use of heuristics. The basic idea of the graph colouring method is the following: if the interference graph contains a node n with a degree less than k, then n can definitively be assigned a colour that is different from the colours of all its neighbours. The node n is removed from G and a new graph G' is obtained that contains one node and several edges fewer. If no k colouring can be found, heuristics have been proposed to introduce spill code [Cha82], or to split life ranges [CH90]. While the algorithms of [Cha82, CH90] are restricted to basic block level, global register allocation algorithms exceed basic block boundaries and take the control flow structure of the program into account. Examples of global register allocation algorithms based on heuristics are the packing algorithm of [Ben94], the probabilistic register allocation of [PF92] and the optimistic graph colouring approach of Briggs et al. [BCT94].

### 2.2.3. Instruction Scheduling

Most contemporary microprocessors offer intraprocessor parallelism, e.g., parallel functional units and/or pipelines. Instruction scheduling attempts to reorder the (sequential) machine operation sequences produced by previous phases in order to exploit these parallel capabilities. A program dependence analysis determines data and control dependences in the program. These limit the ways the operations of the program can be reordered.

The data dependence graph defines a partial order among the operations of the input program. A precedence relation  $\prec$  on  $N_D$  can be defined where

$$i \prec j \iff i \xrightarrow[G_D]{+} j$$

Thus,  $i \prec j$  holds if operation j depends directly or indirectly on operation i. The resulting problem is to rearrange the instructions of the input program so that the execution time is minimised, but no precedence constraints are violated. In its simplest form, instruction scheduling corresponds to the classical problem of precedence constrained scheduling. Let a set  $\mathcal{T}$  of tasks of length 1 be given, m machines, an arbitrary partial order  $\prec$  on  $\mathcal{T}$ , and an upper bound T on the schedule length. The goal is to find a schedule  $\sigma: \mathcal{T} \to \{1, \ldots, T\}$ , so that for all  $t \in \{1, \ldots, T\}$  where  $|\{i \in \mathcal{T}: \sigma(i) = t\}| \leq m$  holds:

$$i \prec j \qquad \Rightarrow \qquad \sigma(i) < \sigma(j)$$

#### 2. The Code Generation Problem

This optimisation problem is already NP-complete for m=2, if each task has to be executed by a dedicated machine [GJ79]. In the problem of instruction scheduling the tasks correspond to machine operations and the machines represent parallel functional units of the underlying processor, e.g. ALUs, multipliers, etc.

For real-world hardware architectures, the problem usually is more complex. One reason is that the assumption that each task has length 1 in general is not valid. If the assumption holds and each task can be executed by any of the available m machines the scheduling problem can be solved in polynomial time if m=2. This problem already becomes NP-complete if both tasks lengths 1 and 2 are allowed. In instruction scheduling each task has to be executed by one specific machine and the task length in general can be any nonnegative integer. Another complication is that many architectures exhibiting instruction-level parallelism dispose of several identical functional units that represent instances of one functional unit type. In this case additional resource constraints have to be taken into account such that in the classification of [GJ79] the instruction scheduling problem corresponds to precedence and resource constrained scheduling. The complexity further rises if the assignment of operations to functional units is not uniquely determined, and if irregular restrictions of parallelism have to be taken into account.

Several heuristic scheduling methods are in use for instruction scheduling, e.g. list scheduling [LDS80, Fis81, Gas89], trace scheduling [Fis81], region scheduling [GS90], and percolation scheduling [Nic85]. The list scheduling algorithm [LDS80] starts with an empty list of instructions. A microoperation is inserted into the last instruction of the list if it satisfies the following three conditions:

- It is ready, i.e. all predecessors in the data dependence graph have already been scheduled.

- Its priority is the highest among all ready microoperations. Different heuristics have been proposed to determine the priority, e.g., the time an operation remains in the data ready set, or the length of the longest path from an operation in the data dependence graph (highest-level-first heuristic).

- The insertion into the last instruction is feasible, i.e. all operations already contained in it can be executed in parallel to the current operation.

If there is no ready operation that can be inserted into the last instruction, a new instruction is appended to the list. List scheduling is the most common algorithm for local instruction scheduling; its worst-case time complexity is  $\mathcal{O}(n^2)$  for n microoperations [LDS80].

An algorithm for global instruction scheduling is Fisher's trace scheduling algorithm. The basic idea of this approach is to schedule the operations of consecutive basic blocks jointly in order to increase the available parallelism. Basic blocks that are frequently executed directly after one another should be addressed jointly. For this, the code generator retrieves information about the execution frequencies of the basic blocks in a procedure by measurements or heuristic estimates. The algorithm

decomposes the control flow graph of a procedure into disjoint subpaths. First it considers the most frequently executed block. Then it decides whether a preceding or subsequent basic block is scheduled jointly with the current block. During the scheduling of the resulting trace, operations can be moved from the original basic block beyond control flow forks and joins. In basic blocks leading into or out of this trace, compensation code has to be inserted. Then the most frequently executed block that has not been scheduled yet is selected and the algorithm iterates until all basic blocks of the procedure have been scheduled.

#### 2.2.4. The Phase Coupling Problem

The classical code generation methods described above address each code generation subtask in a separate phase. Unfortunately the code generation tasks are interdependent; decisions made in one phase impose constraints to the subsequently executed phases. For regular architectures the quality of the heuristic methods is satisfactory. For irregular architectures however the interdependencies between the phases usually lead to a significant decrease of code quality [ZSWS95]. In the following some basic interdependencies between the code generation phases are described; the next section then focuses specifically on code generation for irregular architectures.

The goal of code selection is to select the cheapest instruction sequence for a given subgraph of the intermediate representation. Memory accesses increase the cost of the instruction sequence. Therefore the code selector will use as many registers as possible. Since code selection usually takes place before register allocation and assumes an infinite number of registers it is in conflict with register allocation that has to cope with a limited number of registers. Since the costs of spill code are not considered during code selection, the chosen operation sequence may turn out to be disadvantageous due to the insertion of spill code. Moreover the conventional heuristic of breaking up directed acyclic graphs into trees suitable for tree-based code selection may introduce unnecessary stores of intermediate values.

A similar conflict exists between register allocation and instruction scheduling. For instruction scheduling it is profitable to use many different registers since this leads to a reduction of the anti and output dependences. Those dependences are often termed false dependences since they are caused by the reuse of physical registers and are not dictated by the program semantics. Nevertheless they restrict the available parallelism. Since the goal of register allocation is to minimise the number of memory accesses it will try to reuse as many registers as possible whereas for instruction scheduling it would be better to use different registers as long as this does not lead to the insertion of spill code. Thus, if register allocation is performed first, it can limit the available parallelism by introducing false data dependences. If instruction scheduling precedes register allocation, the number of simultaneously live values can be increased so much that many of these values have to be stored in main memory which may deteriorate the code quality considerably.

Several heuristic methods have been developed that take into account the re-

quirements of other code generation subtasks with the help of estimations. A detailed overview of those methods is given in Sec. 11.2. Since for regular architectures heuristic methods usually produce satisfactory results, exact phase-coupling methods integrating different code generation phases in a homogeneous approach have not been estimated promising. The possible increase of code quality has not been considered worth the increase of compilation time associated with more powerful solution algorithms. However for irregular architectures the situation is different.

### 2.3. Code Generation for Embedded Processors