# Eine graphische Arbeitsumgebung für den parametrisierten Entwurf integrierter Schaltkreise

#### DISSERTATION

zur Erlangung des Grades des Doktors der Naturwissenschaften der Technischen Fakultät der Universität des Saarlandes von

**Thomas Burch**

Saarbrücken 1994 Tag des Kolloquiums: 29. Juni 1995

Dekan: Prof. Dr. H. Bley

Vorsitzender: Prof. Dr. J. Petersen

1. Berichterstatter: Prof. Dr. G. Hotz

2. Berichterstatter: Prof. Dr. W. J. Paul

Akademischer Mitarbeiter: Dr. J. Sellen

# Inhaltsverzeichnis

|   | Einleitung                                         |                                     |                                                          |    |  |  |  |

|---|----------------------------------------------------|-------------------------------------|----------------------------------------------------------|----|--|--|--|

| 1 | Graphische Eingabe großer Schaltungen              |                                     |                                                          |    |  |  |  |

|   | 1.1                                                | -                                   |                                                          |    |  |  |  |

|   | 1.2                                                | dlagen des Netzkalküls              | 19                                                       |    |  |  |  |

|   |                                                    | 1.2.1                               | Die Bikategorie der logisch-topologischen Netze          | 19 |  |  |  |

|   |                                                    | 1.2.2                               | Rekursive Netzgleichungssysteme                          | 26 |  |  |  |

|   | 1.3                                                | Graph                               | nische Eingabe von Gleichungssystemen über Netzvariablen | 30 |  |  |  |

|   |                                                    | 1.3.1                               | Syntaktische Strukturen                                  | 32 |  |  |  |

|   |                                                    | 1.3.2                               | Eine Datenstruktur für graphische Netzgleichungen        | 38 |  |  |  |

|   | 1.4                                                | Konfig                              | gurierbare Schaltkreisbeschreibungen                     | 55 |  |  |  |

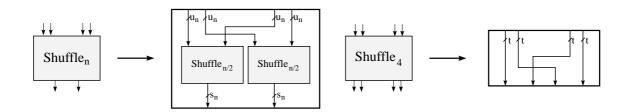

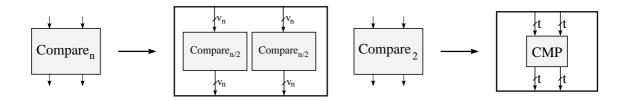

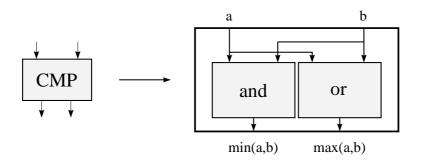

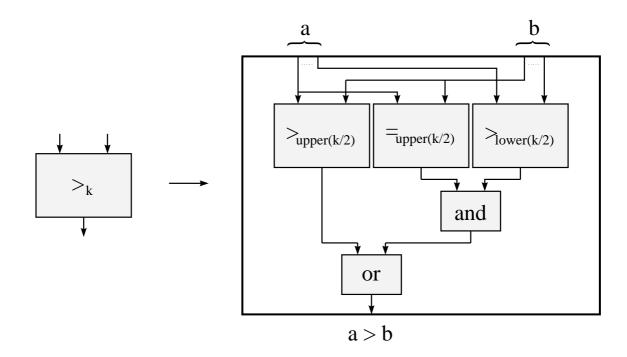

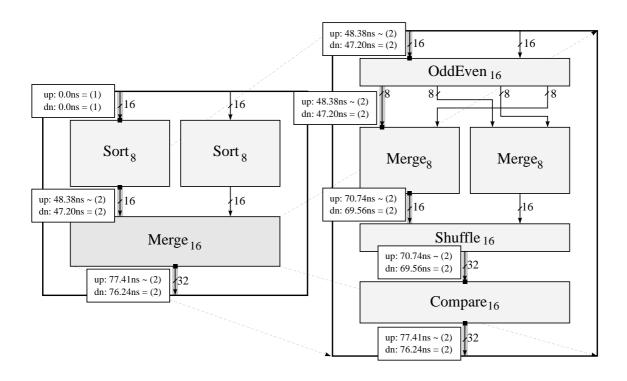

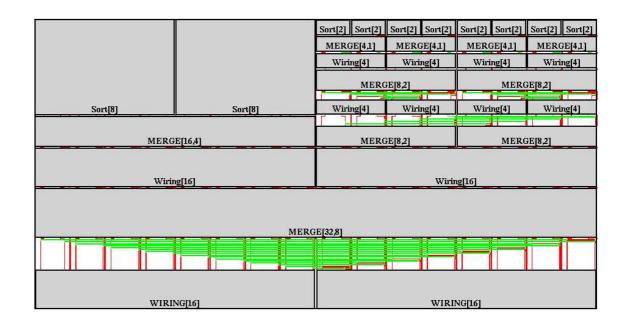

|   |                                                    | 1.4.1                               | Odd-Even-Mergesort                                       | 55 |  |  |  |

|   |                                                    | 1.4.2                               | Parallele Präfix-Berechnung                              | 63 |  |  |  |

|   | 1.5                                                | Zusan                               | nmenfassung                                              | 68 |  |  |  |

| 2 | Effiziente hierarchische Schaltkreisdarstellung 69 |                                     |                                                          |    |  |  |  |

|   | 2.1                                                | Aufba                               | u der hierarchischen Datenstruktur                       | 71 |  |  |  |

|   |                                                    | 2.1.1                               | Erzeugung der Hierarchieebenen                           | 71 |  |  |  |

|   |                                                    | 2.1.2                               | Wahl der anwendbaren Netzvariable                        | 77 |  |  |  |

|   |                                                    | 2.1.3                               | Auswertung der parametrisierten Ausdrücke                | 78 |  |  |  |

|   | 2.2                                                | .2 Berechnung der Leitungsvariablen |                                                          |    |  |  |  |

|   |                                                    | 2.2.1                               | Herleitung der Gleichungen                               | 81 |  |  |  |

|   |                                                    | 2.2.2                               | Lösung des Gleichungssystems                             | 84 |  |  |  |

|   |                                                    | 2.2.3                               | Beispiel                                                 | 85 |  |  |  |

|   |                                                    | 2.2.4                               | Fehlerbehandlung                                         | 86 |  |  |  |

|   | 2.3                                                | Zusan                               | nmenfassung                                              | 89 |  |  |  |

| 3 | Systembeschreibung 9                               |                                     |                                                          |    |  |  |  |

|   | 3.1                                                | Die gr                              | raphische Oberfläche                                     | 92 |  |  |  |

|   |                                                    | 3.1.1                               | Funktionale Gliederung der Oberfläche                    | 92 |  |  |  |

|   |                                                    | 3.1.2                               | Graphische Grundfunktionen                               | 94 |  |  |  |

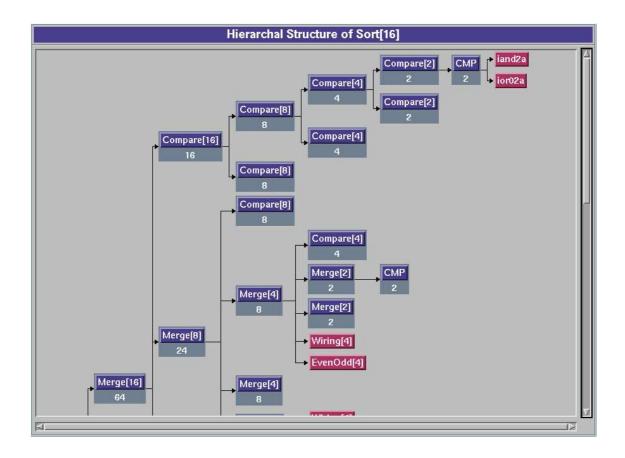

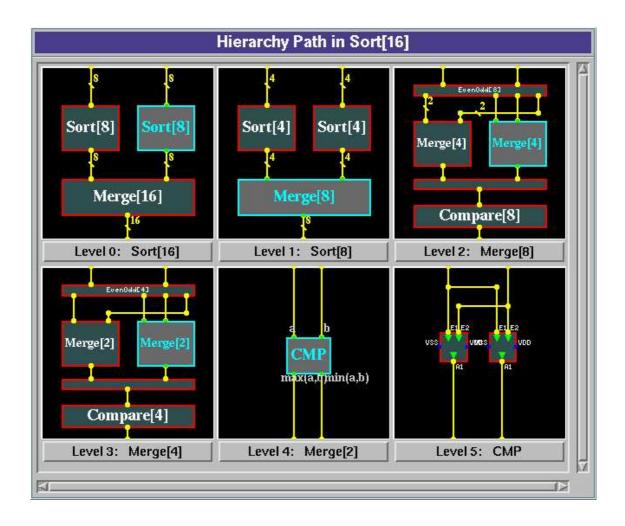

|   |                                                    | 3.1.3                               | Visualisierung der Hierarchiestruktur                    | 95 |  |  |  |

|   |                                                    | 3.1.4                               | Schema der Integration                                   | 98 |  |  |  |

|   | 3.2                                 | Analy     | se-Werkzeuge                                         |  |  |  |  |

|---|-------------------------------------|-----------|------------------------------------------------------|--|--|--|--|

|   |                                     | 3.2.1     | Logiksimulation                                      |  |  |  |  |

|   |                                     | 3.2.2     | Signallaufzeitanalyse                                |  |  |  |  |

|   | 3.3                                 | Synthe    | ese-Werkzeuge                                        |  |  |  |  |

|   |                                     | 3.3.1     | Schichtzuweisung                                     |  |  |  |  |

|   |                                     | 3.3.2     | Versorgungsnetze                                     |  |  |  |  |

|   |                                     | 3.3.3     | Geometrisches Layout                                 |  |  |  |  |

|   | 3.4                                 | Testwe    | erkzeuge                                             |  |  |  |  |

|   | 3.5                                 | Modifi    | ikation der Hierarchie                               |  |  |  |  |

|   |                                     | 3.5.1     | Expansion einer Instanz                              |  |  |  |  |

|   |                                     | 3.5.2     | Geeignete graphische Darstellung                     |  |  |  |  |

|   |                                     | 3.5.3     | Drehung von Instanzen                                |  |  |  |  |

|   |                                     | 3.5.4     | Auflösung von Bussen                                 |  |  |  |  |

|   | 3.6                                 | Das S     | ystem im praktischen Einsatz                         |  |  |  |  |

|   |                                     | 3.6.1     | Schnittstellen zu kommerziellen Systemen             |  |  |  |  |

|   |                                     | 3.6.2     | Konkrete Entwürfe                                    |  |  |  |  |

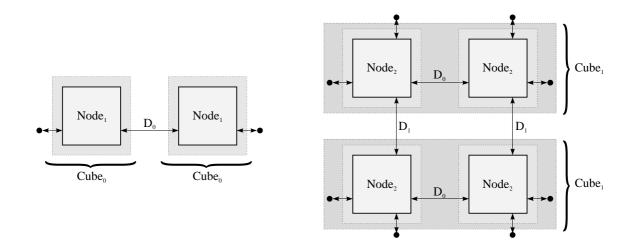

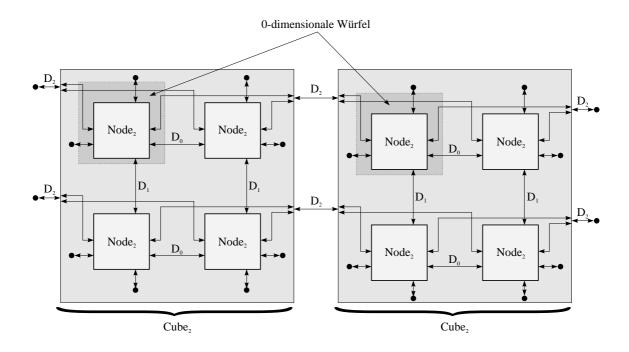

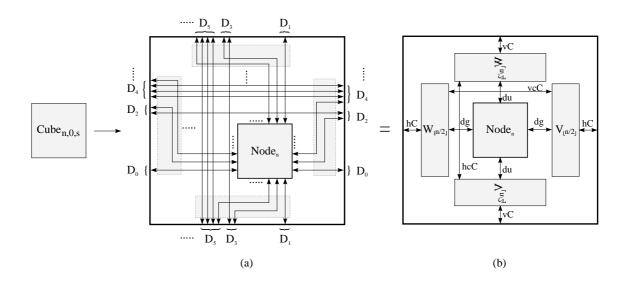

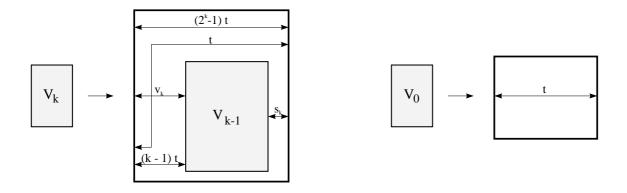

| 4 | Parallele Netzwerkarchitekturen 145 |           |                                                      |  |  |  |  |

|   | 4.1                                 |           | -dimensionale Würfel                                 |  |  |  |  |

|   |                                     | 4.1.1     | Parametrisierte Beschreibung der Topologie           |  |  |  |  |

|   |                                     | 4.1.2     | Paralleles Sortieren durch Column–Sort               |  |  |  |  |

|   | 4.2                                 | Das $n$ - | -dimensionale Gitter                                 |  |  |  |  |

|   |                                     | 4.2.1     | Parametrisierte Beschreibung der Topologie           |  |  |  |  |

|   |                                     | 4.2.2     | Ein Elementarknoten für die Matrixmultiplikation 161 |  |  |  |  |

|   | <i>1</i> 3                          | Zusam     | menfassing 163                                       |  |  |  |  |

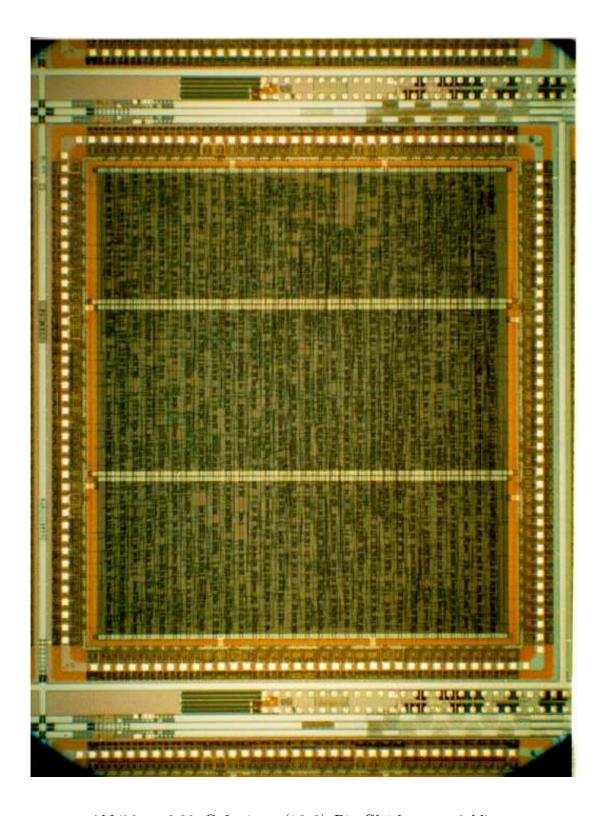

Als Miniaturisierung bezeichnet man die Entwicklungsrichtung im Bereich der Elektronik, die den Fortschritt der letzten Jahrzehnte – die vielzitierte "zweite industrielle Revolution" – entscheidend gefördert hat. Ausgelöst wurde das Miniaturisierungsstreben durch den wachsenden Bedarf an komplexen elektronischen Einrichtungen in fast allen technischen Disziplinen, die eine drastische Verkleinerung der elektronischen Bauelemente erzwangen. Diese Entwicklung begann in den sechziger Jahren mit Schaltungen in SSI-Technologie (small scale integration), die nur eine geringe Anzahl an Gatterfunktionen auf einem Halbleiterplättchen zuließen. Über MSI- (medium scale integration) und LSI-Schaltungen (large scale integration) führte die Entwicklung zur heutigen VLSI-Technologie (very large scale integration). Die Steigerung der Integrationsdichte beruht auf dem Fortschritt in zwei unterschiedlichen Bereichen. Zum einen gelang es, immer feinere Strukturen zu produzieren, zum anderen konnten bei immer größeren Chipflächen akzeptable Ausbeuten an funktionsfähigen Chips erzielt werden. Die Folge war, daß seit 1970 etwa alle drei Jahre eine neue Generation von integrierten Schaltkreisen auf den Markt kam, die jeweils viermal soviel Elemente pro Chip enthielt wie die vorhergehende. Mit dem 4 MBit-Speicherchip wurde 1989 erstmals der "Submicron-Bereich" erschlossen, wobei die feinsten Strukturen nur noch  $0.8\mu\mathrm{m}$  breit sind. Dies liegt weit jenseits der menschlichen Erfahrungswelt, die bei der Dicke eines Haares von vielleicht  $40\mu m$  endet.

Neben der Raum- und Gewichtsersparnis sowie der beträchtlichen Verringerung von Signallaufzeiten, Wärmeentwicklung und Energiebedarf ist bei der Miniaturisierung auch die Steigerung der Fertigungsproduktivität und die Zuverlässigkeit der gefertigten Chips von großer Bedeutung. Dies läßt sich bei zunehmend komplexeren Schaltkreisen mit Millionen von Transistoren pro Chip nicht mehr ohne ausreichende Entwurfsunterstützung durch leistungsfähige Rechner wirtschaftlich rentabel bewerkstelligen. Am Beispiel der verschiedenen Generationen von Intel-Prozessoren läßt sich diese Entwicklung nachvollziehen. Während beim 8-Bit-Mikroprozessor 8080 im Jahre 1974 noch jeder der ca. 5500 Transistoren einzeln optimiert wurde, um damit die Produktionskosten zu senken, gewannen im Lauf der Zeit die Entwurfskosten und Entwurfszeiten immer größeres Gewicht. Der 32-Bit-Mikroprozessor i486 aus dem Jahre 1989 enthält ca. 1,2 Millionen Transistoren und wurde strukturiert mit Rechnerunterstützung entwickelt ([GIKN89]).

Während bis zum Anfang der achziger Jahre die Hauptanwendungsgebiete integrierter Schaltkreise im Bereich von Speicherbausteinen und Mikroprozessoren lag, die in großen Stückzahlen hergestellt wurden, geht die Tendenz seitdem immer mehr in den Bereich der anwendungsspezifischen Schaltungen (ASIC). Dieser Entwicklung standen zunächst die verhältnismäßig hohen Entwicklungskosten entgegen, die bei den für diese Schaltungen üblichen niedrigen Stückzahlen zu unvertretbar hohen Einzelstückkosten führten. Der Fortschritt in der Fertigungstechnik einerseits und die Entwicklung neuer Verfahren für den rechnerunterstützten Entwurf andererseits bewirkten aber eine drastische Senkung der Entwicklungskosten, so daß auch Chips für spezielle Anwendungen und in sehr kleiner Stückzahl interessant wurden. Mittlerweile beträgt der Anteil von ASICs am Weltumsatz integrierter Schaltkreise mehr als 20% ([Lev92]). Die Erschließung neuer Anwendungsgebiete in nahezu allen Bereichen des täglichen Lebens erfordert aber, daß die Fähigkeit zum Entwurf integrierter Schaltkreise nicht nur auf wenige hochspezialisierte Fachleute beschränkt bleiben darf. Vielmehr muß diese Fähigkeit als eine neue Anwendungstechnik – ähnlich der Programmiertechnik für Software – auch im Chip-Entwurf weniger erfahrenen Entwicklern zugänglich gemacht werden.

Ein Vergleich des Chip-Entwurfs mit der Softwareentwicklung ist allerdings nur bedingt möglich. Die automatische Durchführung des gesamten Entwurfsprozesses, d.h. die "Übersetzung" einer eingegebenen Spezifikation in eine korrekte Schaltungsimplementierung durch sogenannte Silicon Compiler, beschränkt sich heutzutage aufgrund der Komplexität der Aufgabe auf kleinere Entwürfe. Bei größeren Schaltungen wird der Entwurfsprozeß dagegen in eine Abfolge von Einzelschritten gegliedert, von denen jeder mit Rechnerunterstützung durchgeführt wird. Damit ergibt sich eine Hierarchie von Teilspezifikationen, wobei jeweils elementarere Teilfunktionen zu komplexeren Funktionen zusammengesetzt werden. Auf der niedrigsten Ebene treten nur noch Grundfunktionen auf, die aus einer entsprechenden Bausteinbibliothek entnommen werden. Die einzelnen Hierarchieebenen korrespondieren zu Beschreibungsebenen, die zur Darstellung digitaler Systeme eingeführt wurden. Auf der obersten Ebene, der Systemebene, werden Funktionsblöcke wie Prozessoren und Speicher verwendet, in der Architekturebene werden Datenpfade und Steuerwerke miteinander verbunden. Die Register-Transferebene bilden Bausteine wie Zähler, Register oder arithmetische Einheiten, die Logikebene beinhaltet elementare Zellen wie Flipflops und Gatter. Die untersten Ebenen sind durch die elektrische Ebene mit Transistoren, Widerständen und Kondensatoren und die physikalische Ebene auf Basis von dotierten Halbleiterflächen gegeben.

Die einzelnen Entwurfsebenen entsprechen also Darstellungsebenen für die Entwurfsdaten mit unterschiedlichen Abstraktionsgraden. Ein Entwurfsschritt besteht im korrekten Umsetzen der Beschreibung einer höheren Ebene in die Darstellung einer niedrigeren Ebene, wobei jeder Entwurfsschritt mehrmals die Phasen der Konstruktion und Validierung durchläuft. Unter Validierung versteht man dabei den Vergleich zwischen Spezifikation und der im Konstruktionsschritt erzeugten Implementierung. Der stattdessen häufig verwendete Begriff der Verifikation charakterisiert den formalen Beweis, daß die Implementierung eine vorgegebene Spezifikation erfüllt. In der Praxis

beschränkt man sich in der Regel auf die Überprüfung einer Implementierung für eine bestimmte Menge von Testfällen, was einer Validierung durch Simulation entspricht.

Die Effizienz des Entwurfsprozesses hängt entscheidend von den eingesetzten Entwurfswerkzeugen ab. Diese Werkzeuge sind aufgrund der Vielzahl an unterschiedlichen Teilschritten im allgemeinen sehr heterogen und können nur selten ohne Schnittstellenprobleme kombiniert werden. Durch die Einführung standardisierter Hardwarebeschreibungssprachen wie beispielsweise EDIF ([Com87]) und VHDL ([LSU89]) wurde zwar prinzipiell die Möglichkeit geschaffen, Entwurfsdaten auszutauschen. Die Erzeugung eines textuellen Austauschformates aus einer rechnerinternen Datenstruktur und die Umsetzung des Austauschformates zurück in eine andere rechnerinterne Repräsentation ist jedoch weder elegant noch effizient. Um bei entsprechender Handhabung überhaupt erst einen breiten Einsatz der Entwurfswerkzeuge zu ermöglichen, müssen die entwickelten Verfahren daher durch komfortable Entwurfsumgebungen unterstützt werden. Hierfür ist ein integriertes Entwurfssystem mit leistungsfähigen Werkzeugen innerhalb einer leicht bedienbaren graphischen Benutzeroberfläche unerläßlich. Eine solche Entwurfsumgebung muß dem Entwickler eine graphisch-interaktive Schnittstelle auf möglichst hoher Beschreibungsebene anbieten, um ihn von nicht relevanten technisch-bedingten Details freizuhalten. Dazu gehört beispielsweise das Verbergen von Informationen, die ausschließlich durch die Produktionstechnologie und die Organisation des Entwurfsprozesses gegeben sind. Darüberhinaus müssen ausdrucksstarke Methoden zur Visualisierung von Entwurfsdaten gewählt werden, um dem Entwerfer auf anschauliche Weise die Kontrolle des Entwurfsprozesses zu ermöglichen.

Da mit dem technologischen Fortschritt auch immer höhere Anforderungen an die Entwurfswerkzeuge gestellt werden, darf eine solche Entwurfsumgebung nicht als starres Programmsystem entwickelt werden. Änderungen in der Technologie oder die Entdeckung effizienterer Berechnungsverfahren machen es notwendig, daß das System leicht modifizierbar ist. Es sollte daher nach dem Prinzip einer Werkbank konzipiert werden, die dem Entwerfer eine ganze Palette von Werkzeugen anbietet. Es können für einen einzelnen Entwurfsschritt auch mehrere Werkzeuge zur Verfügung stehen, die in Abhängigkeit vom jeweiligen Entwurf ausgewählt werden. Die Konfigurierbarkeit des Entwurfssystems ermöglicht einerseits die Integration neu entwickelter Werkzeuge in eine dem Entwerfer vertraute Arbeitsumgebung und erhöht damit deren Akzeptanz. Andererseits wird der Werkzeugentwickler unterstützt, indem er grundlegende Eigenschaften der Werkbank während der Implementierung nutzen kann. Wünschenswerte Leistungsmerkmale einer solchen Werkbank bestehen in einer graphischen Spezifikationsebene mit hierarchischer Verfeinerung und Abstraktion, der Bereitstellung von komfortablen Simulationswerkzeugen für die verschiedenen Entwurfsebenen, der Konstruktion von Fertigungsdaten sowie der automatischen Generierung von Fertigungstests. Zusätzlich muß dem Entwerfer die Möglichkeit gegeben werden, den Ablauf der Werkzeuge und die berechneten Ergebnisse leicht zu beobachten und bei Bedarf interaktiv in den Entwurfsprozeß einzugreifen.

Gegenstand der vorliegenden Arbeit ist die Entwicklung einer konfigurierbaren graphischen Entwurfsumgebung für das VLSI-Entwurfssystem CADIC, welches im Rahmen des Sonderforschungsbereiches 124 "VLSI Entwurfsmethoden und Parallelität" im Teilprojekt B1 entwickelt wurde ([BHKM84],[BHK+87],[BBH+90]). Besonderer Wert wird auf die Entwicklung einer benutzerfreundlichen graphischen Arbeitsumgebung gelegt, die einen komfortablen Entwurf integrierter Schaltkreise erlaubt. Ein weiterer wichtiger Gesichtspunkt ist die Konfigurierbarkeit des Gesamtsystems, indem es leicht durch neu entwickelte Verfahren für einzelne Entwurfsschritte erweitert werden kann. Wir skizzieren zunächst die daraus resultierenden wichtigsten Leistungsmerkmale dieser graphischen Entwurfsumgebung.

#### Graphische Eingabe großer Schaltkreise

Bei kommerziellen Entwurfssystemen (etwa [CAD92], [HNS86], [SYS90]) erfolgt die Schaltungseingabe entweder graphisch über einen Schematic Editor oder textuell auf Basis einer Hardwarebeschreibungssprache. Die angebotenen graphischen Editoren stellen Entwürfe dabei in der Regel als statische Komponenten dar, so daß dem Entwerfer wenig Freiraum für einen flexiblen Entwurf gelassen wird. Sie unterstützen zwar im allgemeinen die hierarchische Eingabe von Schaltungen, beschränken sich aber auf feste Ausprägungen eines Entwurfs. Parametrisierungen sind bestenfalls bei der Auswahl bestimmter Teilkomponenten wie Speichermodulen aus einer vorgegebenen Menge von Realisierungen möglich. Änderungen in der Technologie, die beispielsweise eine Verdoppelung der Bitbreite der Operanden ermöglichen, erfordern daher eine Überarbeitung der gesamten Eingabe. Systeme, die ihre Eingabe über eine Hardwarebeschreibungssprache beziehen, arbeiten meistens mit Konstrukten, die denen aus imperativen und funktionalen Programmiersprachen sehr ähnlich sind. Diese Beschreibungssprachen, die allerdings oft auf selbstdefinierten Formaten basieren, zeichnen sich in der Regel durch eine hohe Flexibilität aus. Sie haben aber den entscheidenden Nachteil, daß Folgen, die aus einer Anderung der Eingabe resultieren, erst nach der vollständigen Umsetzung der Spezifikation erkannt werden. Da dies unter Umständen ein zeitkritischer Vorgang ist, weisen solche Systeme in der Regel kein hohes Maß an Interaktivität auf.

Demgegenüber bietet der graphische Editor von CADIC viele Vorzüge, die sich aus der Kombination der Flexibilität einer textuellen Beschreibung mit der Übersichtlichkeit einer graphischen Eingabe ergeben. Er hat im Vergleich mit anderen Beschreibungsmethoden den entscheidenden Vorteil, daß die zugrundeliegende Spezifikationsebene auf einem wohldefinierten mathematischen Kalkül ([Hot65], [Hot66], [Mol86]) basiert. Er ist dadurch besonders gut geeignet, um sehr große Schaltungen einfach zu beschreiben. So erlaubt er die Ausnutzung von Regularitäten, die den Berechnungsvorschriften einer Schaltung zugrundeliegen, um daraus rekursive Spezifikationen herzuleiten. Insbesondere lassen sich die Eingaben parametrisieren, so daß durch eine feste Menge von graphischen Eingaben ganze Familien von Schaltkreisen beschrieben werden können. Grundlegende Beispiele für rekursiv definierbare Schaltkreise sind unter anderem verschiedene Klassen von Addierern, Multiplizieren oder Sortiernetzwerken. Die

dem graphischen Editor zugrundeliegende Spezifikationsebene ist dabei so flexibel, daß algorithmische Teilstrukturen eines Entwurfs unabhängig von festen Realisierungen für bestimmte Basisoperationen definiert werden können. Dies wird durch die Verwendung sogenannter Leitungstypen erreicht, deren Werte sich erst aus der Belegung der Schaltkreisparameter und der Wahl einer bestimmten Basisoperation ergeben. Damit erhält der Entwerfer eine Möglichkeit zur Eingabe mehrfach verwendbarer Beschreibungen, die nach Bedarf konfiguriert werden können.

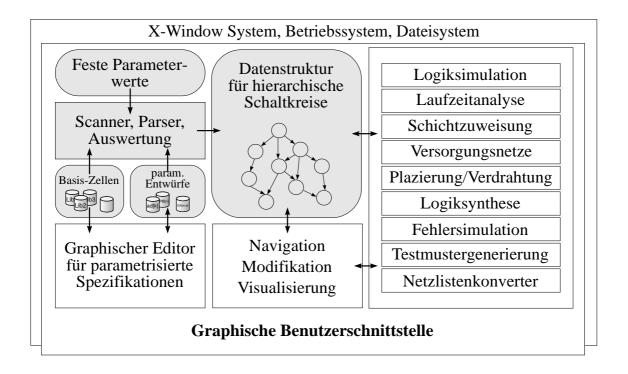

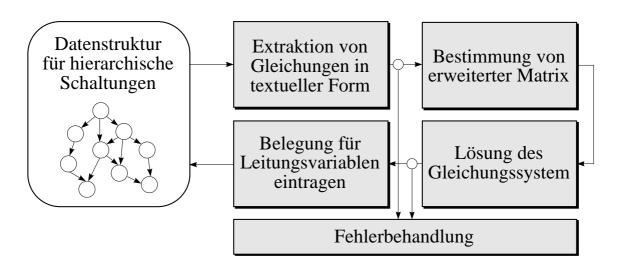

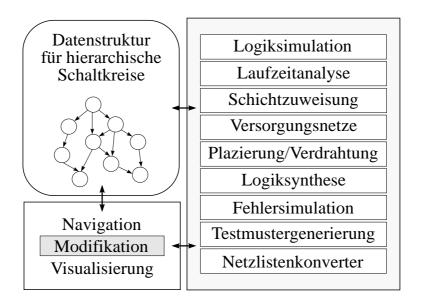

#### Effiziente hierarchische Schaltkreisdarstellung

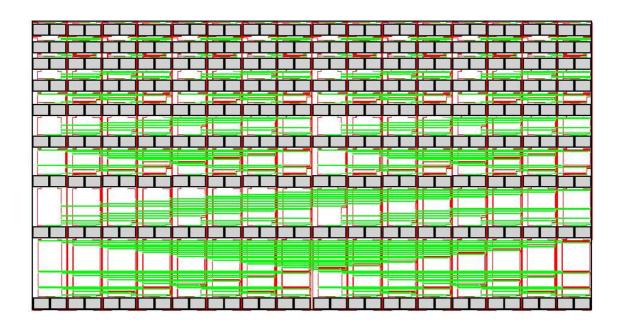

Ein prinzipielles Problem beim Entwurf großer Schaltkreise ist die Kontrolle über die Datenmengen. Hier macht man sich zunutze, daß große Schaltungen im allgemeinen einen hohen Regularitätsgrad aufweisen. Dies resultiert in einer kompakten Beschreibung, die im wesentlichen in einer Schaltkreiskonstruktion, basierend auf einer Substitution von Komponenten durch größere Teilnetze, besteht. Eine solche hierarchische Verfeinerung eines Entwurfes führt neben der Verringerung des Speicherbedarfs auch zu wesentlich kürzeren Laufzeiten während Analyse und Synthese. Wichtig ist dabei, daß sowohl die Eingabe an ein Werkzeug als auch dessen Ausgabe hierarchisch ist, damit die weiterverarbeitenden Verfahren ebenfalls auf einer hierarchischen Eingabe arbeiten können. Es darf keine Umwandlung der hierarchischen in eine nichthierarchische Darstellung notwendig werden, da diese exponentiell größer als die Eingabe sein kann. Für die Entwicklung einer integrierten Entwurfsumgebung bietet es sich aus diesen Gründen an, eine zentrale Datenstruktur zur effizienten Repräsentation der Schaltungshierarchie zur Verfügung zu stellen. In diese Datenstruktur, die in unserem Fall durch einen hierarchisch gegliederten Graphen gegeben ist, werden die berechneten Ergebnisse eingetragen. Sie wird, ausgehend von der parametrisierten Eingabe, durch schrittweise hierarchische Verfeinerung unter Ausnutzung von Faltungen erzeugt, indem mehrfach auftretende Teilstrukturen durch ein Objekt der Datenstruktur repräsentiert werden. Man erhält auf diese Weise eine hierarchische Schaltungsdarstellung in Form eines gerichteten azyklischen Graphen.

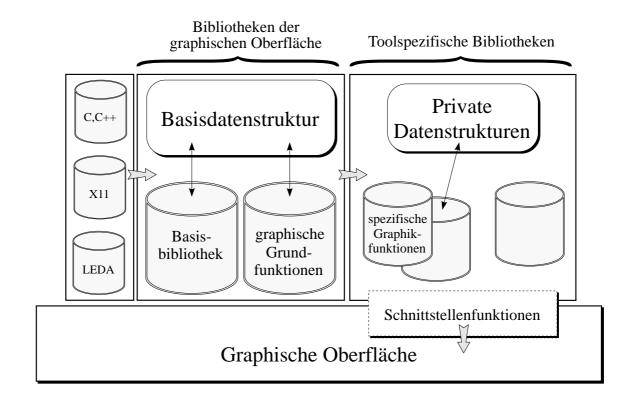

Die Datenstruktur ist hier durch eine Bibliothek von elementaren Funktionen realisiert, die eine Bearbeitung der Objekte auf einfache Weise unterstützt. Dazu gehören beispielsweise Funktionen, die eine systematische Durchmusterung der Hierarchie gestatten. Diesen Suchalgorithmen können spezielle Aktionen als Parameter übergeben werden, die für jedes Objekt der Hierarchie ausgeführt werden. Damit lassen sich beispielsweise leicht kontextfreie Verfahren implementieren, bei denen jede Teilkomponente eigenständig betrachtet wird, ohne ihren Kontext innerhalb der gesamten Schaltung zu berücksichtigen.

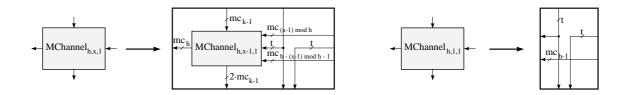

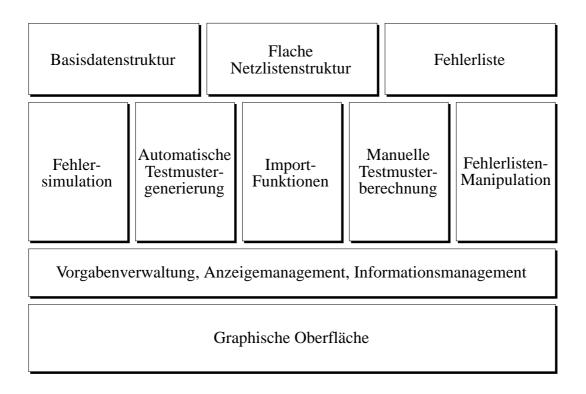

#### Konfigurierbarkeit der Entwurfsumgebung

Um die Integration neu entwickelter Entwurfswerkzeuge zu ermöglichen, ist die graphische Entwurfsumgebung von CADIC nach dem Prinzip einer Werkbank konzipiert. Das Kernstück des Systems bildet eine für alle Entwurfsschritte einheitliche graphische

Benutzeroberfläche. Sie stellt die Basis für die iterative Anwendung der Werkzeuge zur Verfügung und gewährleistet damit den oben erwähnten Wechsel zwischen Konstruktion und Validierung während der Entwurfsschritte. Beispielsweise kann der graphische Editor in Zusammenarbeit mit einem Logiksimulator benutzt werden, um einzelne Teilkomponenten vor ihrer Weiterverwendung zu überprüfen. Dies ist vergleichbar mit einer Software-Entwicklungsumgebung, wo man dem Benutzer die Eingabe, die Übersetzung in ein ausführbares Programm und das Debuggen aus einer Oberfläche heraus ermöglicht.

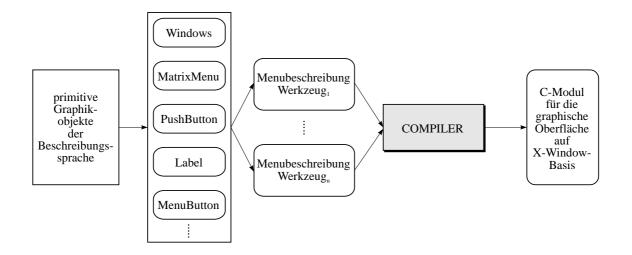

Die Konfigurierbarkeit der Entwurfsumgebung wird durch die modulare Implementierung des Gesamtsystems gewährleistet. Dazu ist jedes Werkzeug durch eigenständige Bibliotheken realisiert, die in die Umgebung eingebunden werden können. Insbesondere können damit wichtige Datenstrukturen zur Entwicklung neuer Entwurfswerkzeuge zur Verfügung gestellt werden. Die Auswahl einer bestimmten Konfiguration erfolgt über eine zu diesem Zweck definierte Beschreibungssprache. Diese Sprache erlaubt mittels einfacher Konstrukte die Konfigurierung der graphischen Oberfläche und der Schnittstellenfunktionen der integrierten Werkzeuge. Ein entsprechender Compiler übersetzt diese Spezifikation in ein Programmodul, welches die benötigten Anweisungen auf Basis des zugrundeliegenden Graphikpaketes enthält. Auf diese Weise läßt sich die Entwurfsumgebung konfigurieren, ohne daß dazu tiefgreifende Kenntnisse über spezielle Graphikfunktionen benötigt werden.

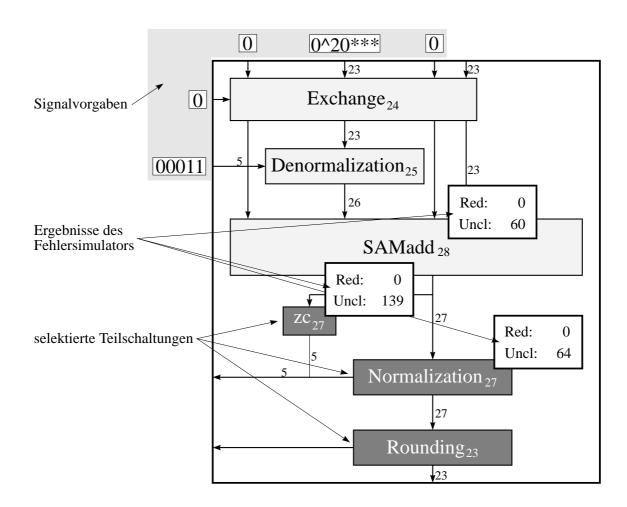

#### Visualisierung und graphische Navigation

Die von den Entwurfswerkzeugen berechneten Resultate werden in übersichtlicher Form graphisch angezeigt, wobei eine direkte Zuordnung zur graphischen Eingabe der Schaltung hergestellt wird. Dies gewährleistet dem Entwerfer einen konkreten Bezug zwischen der Spezifikation und den Ergebnissen. Eng verbunden mit der Visualisierung der Resultate ist die Navigation durch die Schaltungshierarchie. Auf diese Weise können leicht die Stellen eines Entwurfes lokalisiert werden, an denen ein Werkzeug vergleichsweise schlechte Resultate liefert. In direkter Interaktion mit dem graphischen Editor kann auf die Resultate reagiert werden, so daß eine sukzessive Korrektur der Spezifikation unterstützt wird. Im Falle des Logiksimulators lassen sich beispielsweise die Resultate eines Simulationslaufes direkt an den Ein- und Ausgängen der einzelnen Teilkomponenten ablesen. Fehler in der Spezifikation können mit Hilfe der Navigation durch die Schaltung genauestens eingegrenzt werden. In einer graphischen Bibliothek des Systems sind dazu Grundfunktionen enthalten, die von vielen Werkzeugen verwendet werden. Dazu gehören unter anderem Funktionen zur graphischen Auswahl von Objekten, zur Visualisierung der hierarchischen Schaltungsstruktur oder zur Anzeige des aktuell ausgewählten Abstiegspfades durch die Hierarchie.

#### Interaktive Modifikation der Hierarchie

Die hierarchische Arbeitsweise der in das System integrierten Werkzeuge bewirkt, daß alle Vorkommen einer Teilschaltung auf identische Weise behandelt werden. Insbeson-

dere werden die Ergebnisse aufgrund der kontextfreien Vorgehensweise für jede Teilschaltung nur einmal berechnet und an allen Vorkommen eingesetzt. Es ist dabei offensichtlich, daß die Qualität der Ergebnisse stark von der hierarchischen Struktur der Schaltung beeinflußt wird. Man muß mit Trade-Offs zwischen der Kompaktheit der Hierarchie, der Laufzeit der Algorithmen und der Qualität der Ergebnisse rechnen ([KM89]). Der Entwerfer muß also die entscheidenden Stellen in der Hierarchie erkennen, um solchen Effekten entgegenzuwirken. Das Auffinden solch kritischer Stellen ist mit Hilfe der Funktionen zur Visualisierung in Zusammenarbeit mit der Navigation durch die Hierarchie auf komfortable Weise möglich. Eine interaktive Steuerung durch Auflösung von Hierarchieebenen ist dann mittels verschiedener Operationen möglich.

#### Gliederung der Arbeit

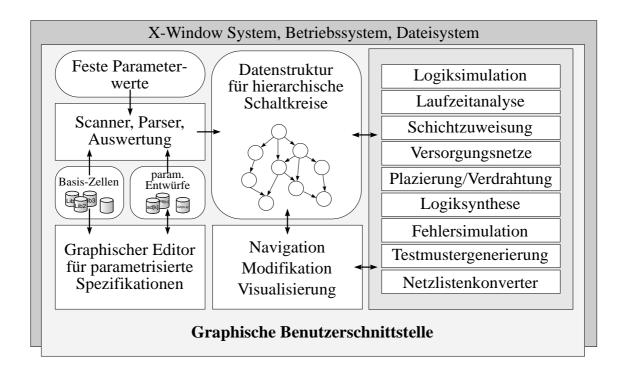

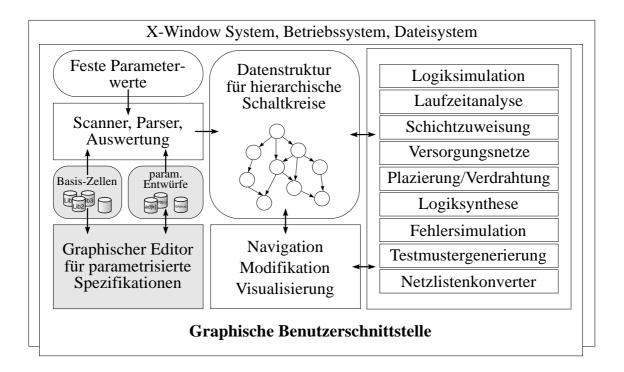

Die Integration der genannten Leistungsmerkmale in die graphische Entwurfsumgebung ist in Abbildung 0.1 dargestellt. Die Gliederung der vorliegenden Arbeit orientiert sich im wesentlichen an den dargestellten Komponenten.

Abbildung 0.1: Komponenten der graphischen Entwurfsumgebung von CADIC

In Kapitel 1 beschreiben wir den graphischen Editor. Im ersten Abschnitt wird zunächst ein kurzer Überblick über die gängigen Methoden zur Beschreibung von Schaltkreisen gegeben. Anschließend wird die unserem System zugrundeliegende Spezifikationsebene auf Basis eines wohldefinierten mathematischen Netzkalküls vorgestellt. Den zentralen Abschnitt dieses Kapitels bildet die Beschreibung einer geeigneten Datenstruktur

zur parametrisierten graphischen Eingabe von Schaltkreisen gemäß den Regeln dieses Netzkalküls. Abschließend wird anhand zweier ausführlicher Beispiele die Flexibilität dieser Beschreibungsmethode verdeutlicht.

In Kapitel 2 zeigen wir, wie aus einer parametrisierten Schaltungsbeschreibung ein spezieller Vertreter dieser Schaltkreisfamilie ausgewählt wird. Für diesen Vertreter wird nach der Belegung aller freien Parameterwerte die Darstellung in Form eines hierarchisch gegliederten Graphen erzeugt.

In Kapitel 3 beschreiben wir den Aufbau des Gesamtsystems. Neben der Grundstruktur der graphischen Oberfläche wird gezeigt, wie die Konfiguration der Entwurfsumgebung und damit die Integration von Werkzeugen unterstützt wird. Der Schwerpunkt liegt hier auf der Erläuterung der verschiedenen Möglichkeiten zur Visualisierung der von den integrierten Werkzeugen berechneten Ergebnisse in Verbindung mit den Funktionen zur graphischen Navigation. Abschließend zeigen wir anhand einiger konkreter Entwürfe, wie sich das System im praktischen Einsatz verhält. Dabei werden auch die implementierten Schnittstellen zu kommerziellen Entwurfssystemen beschrieben, mit Hilfe derer die vorgestellten Entwürfe gefertigt wurden.

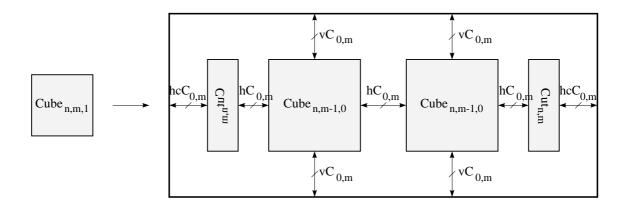

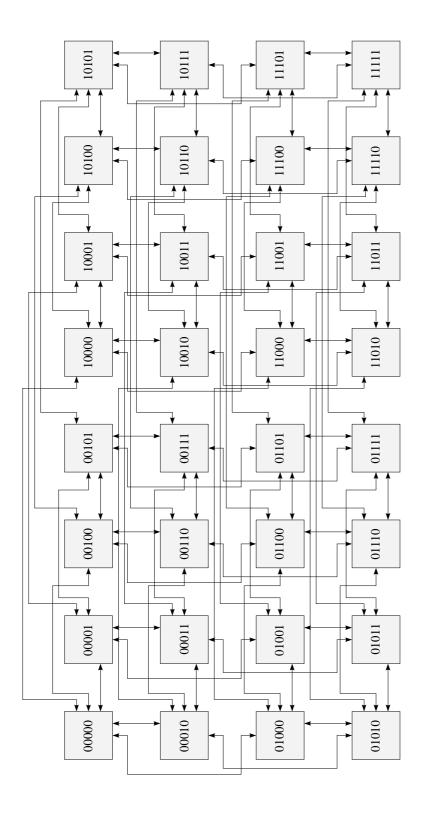

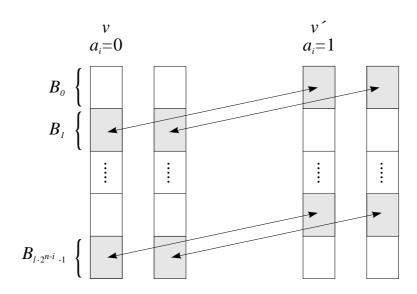

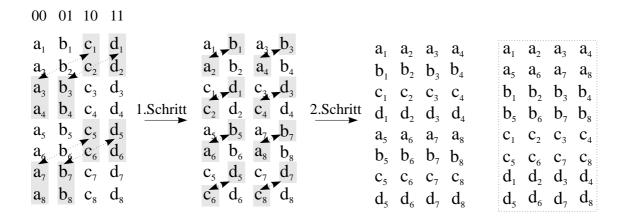

In Kapitel 4 geben wir eine weitere Anwendung der graphischen Spezifikationsebene an, indem wir zeigen, wie sie zur Beschreibung paralleler Systeme genutzt werden kann. Die Eingabe gliedert sich dabei in zwei unabhängige Stufen. Im ersten Schritt wird zunächst ein Kommunikationsschema zwischen Modulen definiert, wobei die Module selbst zunächst als "Black Boxes" aufgefaßt werden. Festgelegt wird nur ihre äußere Schnittstelle, die zur Spezifikation des Kommunikationsschemas maßgeblich ist. Im zweiten Schritt erfolgt dann die algorithmische Realisierung der Module, so daß das gesamte Netzwerk zur Berechnung eines parallelen Algorithmus konfiguriert wird. Anhand zweier Beispiele mehrdimensionaler Kommunikationsschemata wird die prinzipielle Vorgehensweise erläutert.

#### Danksagungen

An dieser Stelle möchte ich all denen danken, die mich bei der Implementierung des Systems und der Erstellung der vorliegenden Arbeit unterstützt haben. Mein Dank gilt vor allem Herrn Prof. Dr. Günter Hotz für die interessante Aufgabenstellung und die zahlreichen Anregungen während ihrer Bearbeitung. Besonders danken möchte ich Wolfgang Vogelgesang für die entscheidende Mitarbeit bei der Konzeption und Implementierung wichtiger Teilkomponenten des Systems. Desweiteren danke ich dem CADIC-Dream-Team, welches in der Besetzung Rainer Backes, Michael Biwersi, Frank Braun, Thomas Fettig, Andrea Gräber, Bernd Grande, Monika Kaiser, Michael Kreutzer, Christian Manß, Michael Meiser, Jörg Ritter, Jörg Schnabel, Oliver Stanke und Gerhard Wannemacher hervorragenden Sportsgeist bei den Implementierungsarbeiten entwickelte. Gisela Pitsch danke ich für das sorgfältige Korrekturlesen der vorliegenden Arbeit. Schließlich gilt mein Dank meinen Kolleginnen und Kollegen, die mir in den letzten Jahren hilfreich zur Seite standen.

### Kapitel 1

# Graphische Eingabe großer Schaltungen

Der Entwurf großer Schaltungen beginnt in vielen Fällen mit graphischen Skizzen in Form von Blockschaltbildern, die anschließend in algebraische Ausdrücke oder Programme umgesetzt werden. Da diese Umformung häufig automatisierbar ist, bietet es sich an, bereits die schematische Skizze als Rechnereingabe zu verwenden. Die Effizienz, mit der ein entsprechender graphischer Editor eingesetzt werden kann, hängt entscheidend von folgenden zwei Faktoren ab:

- 1. von der zugrundeliegenden Spezifikationsebene und

- 2. vom Zusammenspiel des Editors mit den übrigen Entwurfswerkzeugen.

Der erste Punkt ist maßgeblich für die Arbeitszeit, die zur Spezifikation einer Schaltung aufgewendet werden muß. Je mächtiger die Konstrukte der zugrundeliegenden Spezifikationsebene sind, desto einfacher und kürzer werden die Schaltungsbeschreibungen. Vom zweiten Punkt hängt ab, wie schnell Entwurfsfehler lokalisiert und korrigiert werden können. Dies wird entscheidend erleichtert, wenn die Ergebnisse, die von den eingesetzten Entwurfswerkzeugen berechnet werden, in einen direkten Bezug zur graphischen Eingabe gebracht werden.

Das in der vorliegenden Arbeit beschriebene System zeichnet sich dadurch aus, daß es beiden genannten Faktoren in besonderer Weise gerecht wird. Die Spezifikationsebene des graphischen Editors basiert auf einem wohldefinierten mathematischen Kalkül, dessen theoretische Grundlagen in [Hot65], [Hot66] und [Mol86] definiert wurden. Gegenüber anderen Systemen zeichnet sich diese Beschreibungsebene durch ihre besonders hohe Flexibilität aus. So sind die Eingaben parametrisierbar, was Entwürfe ganzer Familien von Schaltkreisen durch eine bestimmte Anzahl von Eingaben ermöglicht. Darüberhinaus können Berechnungsverfahren, die Teilkomponenten eines Entwurfs zugrundeliegen, unabhängig von speziellen Realisierungen ihrer Elementaroperationen beschrieben werden. Beispielsweise läßt sich ein Sortiernetzwerk zunächst unabhängig

vom Typ und von der Kodierung der zu sortierenden Elemente eingeben. Eine spezielle Art von Elementen wird später allein durch die Realisierung eines entsprechenden Basisvergleichers ausgewählt.

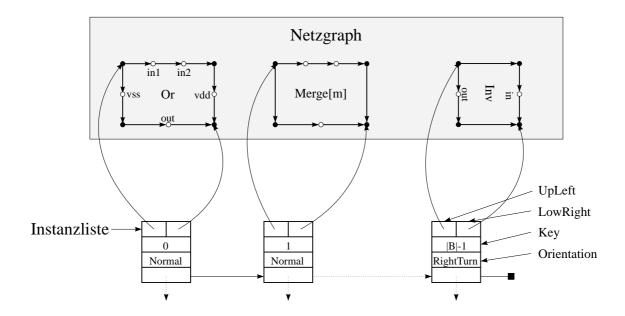

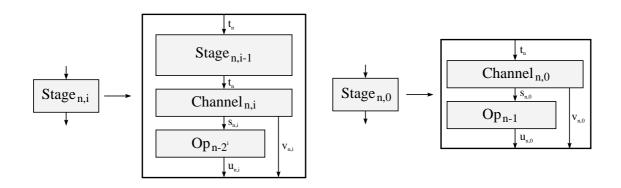

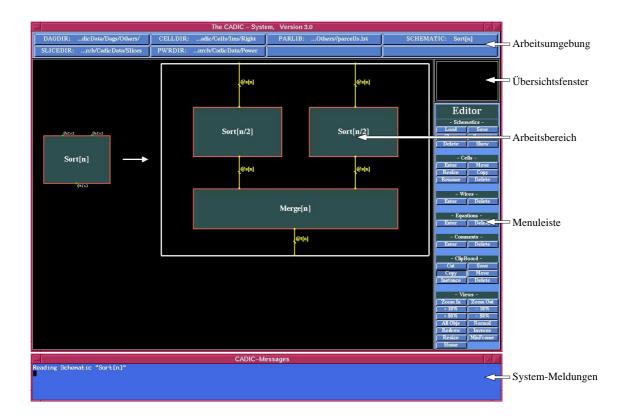

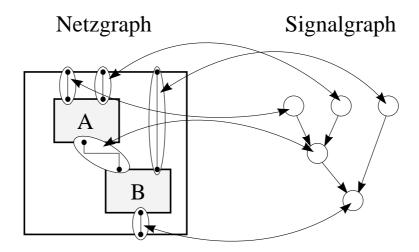

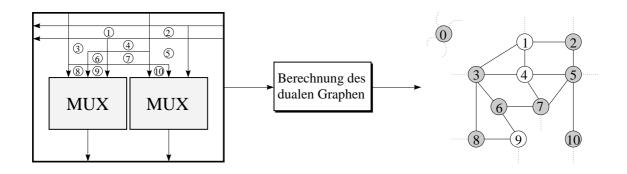

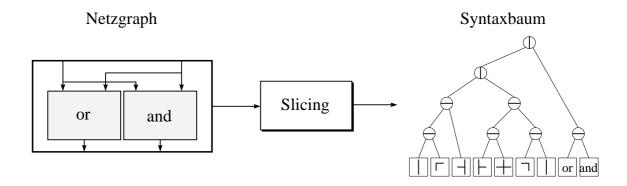

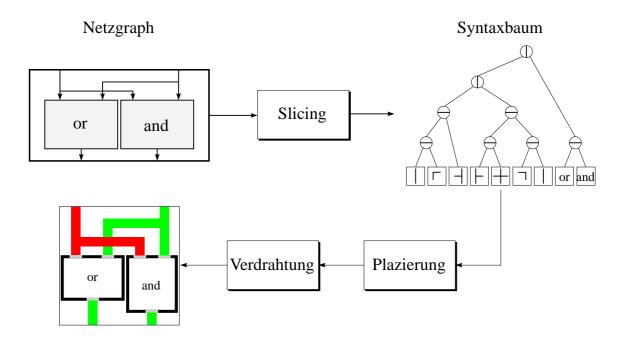

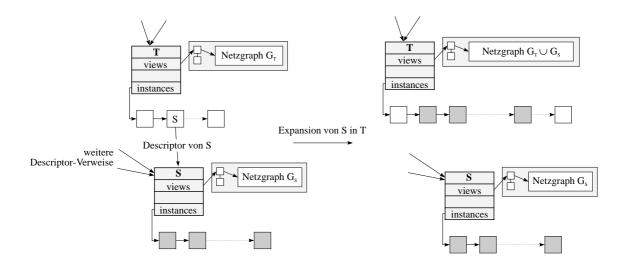

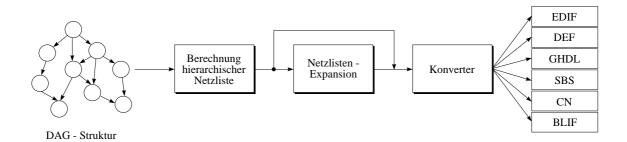

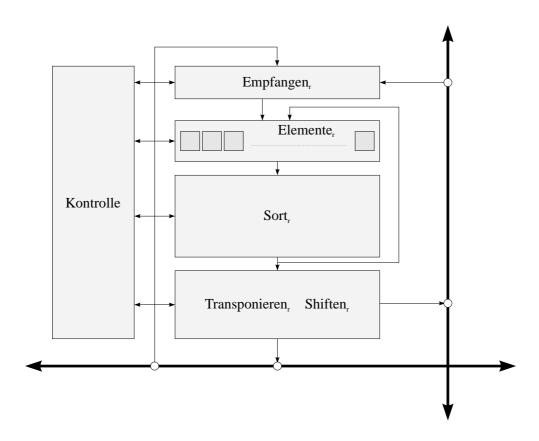

Um ein optimales Zusammenspiel des Editors mit den übrigen Entwurfswerkzeugen zu gewährleisten, ist er, wie dies in Abbildung 1.1 dargestellt ist, in die graphische Oberfläche des Gesamtsystems integriert. Er arbeitet dabei auf einer beliebig wählbaren Menge von Grundzellen, über der Bibliotheken von parametrisierten Entwürfen erstellt werden können. Die Darstellung der Eingaben erfolgt in einer zentralen Datenstruktur, die einen hierarchisch gegliederten Graphen repräsentiert. Diese Basisdatenstruktur bildet auch die Grundlage für die integrierten Werkzeuge, so daß die Visualisierung der berechneten Ergebnisse zusammen mit einer komfortablen Navigation durch die Schaltungshierarchie gewährleistet wird.

Abbildung 1.1: Integration des graphischen Editors in das Gesamtsystem

In diesem Kapitel beschreiben wir nun die Spezifikationsebene, die dem graphischen Editor unseres Systems zugrundeliegt. Zur Abgrenzung gegenüber anderen Beschreibungsformen werden im ersten Abschnitt kurz die gängigen Methoden zur Spezifikation von Hardware dargestellt. Anschließend beschreiben wir die wichtigsten Aspekte des unserem System als Basis dienenden mathematischen Kalküls. Im zentralen Abschnitt dieses Kapitels gehen wir auf die Eigenschaften der gewählten Basisdatenstruktur zur Verwaltung graphischer Netzgleichungssysteme ein. Anhand zweier ausführlicher Beispiele wird abschließend die gewählte Beschreibungsmethode erläutert.

#### 1.1 Hardware-Beschreibungsmethoden

Die Methoden zur Spezifikation integierter Schaltkreise basieren grundsätzlich auf den folgenden beiden Ansätzen:

#### Textuelle Beschreibungsmethode

In diesem Fall erfolgt die Spezifikation einer Schaltung in einer Hardwarebeschreibungssprache. Die Grundlage für solche Sprachen bilden im allgemeinen imperative oder funktionale Programmiersprachen. Man unterscheidet dabei in Abhängigkeit der dargestellten Schaltungscharakteristika drei verschiedene Klassen von Beschreibungssprachen:

- Sprachen, die eine rein funktionale Spezifikation unterstützen ohne dabei strukturelle Eigenschaften einer Schaltung zu berücksichtigen. Beispiele hierfür sind ISPS ([Bar78]) und Macpitts ([SSC82]).

- Sprachen, die sowohl funktionale als auch strukturelle Spezifikationen erlauben, wie dies in Zeus ([GL85]), Hades ([Wir82]), VHDL ([Sha82, LSU89]) und EDIF ([Com87]) möglich ist.

- Sprachen, bei denen nur strukturelle Eigenschaften berücksichtigt werden, beispielsweise HISDL ([Lim82]).

Alle diese Beschreibungssprachen erlauben eine flexible Spezifikation von Schaltkreisen. Sie unterstützen in der Regel eine prozedurale Strukturierung, indem funktionale Blöcke einer Schaltung durch entsprechende Prozeduren repräsentiert werden. Die Anschlüsse eines solchen Blockes entsprechen einem Teil der Parameter der zugehörigen Prozedur. Weitere Parameter können verwendet werden, um Varianten und Fallunterscheidungen auszudrücken. In einem Block verwendete Teilblöcke werden durch Aufrufe der diese Teilblöcke modellierenden Prozeduren umgesetzt, wodurch die hierarchische Gliederung einer Schaltung ermöglicht wird. Insbesondere sind in einigen Beschreibungssprachen auch rekursive Spezifikationen zugelassen.

Als Standardsprachen und international akzeptierte Austauschformate haben sich in erster Linie VHDL und EDIF durchgesetzt. Dabei ist VHDL geeignet, um allgemeine digitale Systeme zu beschreiben. Die Basis dieser Sprache ist ein abstraktes Modell, welches Verhaltens- und Strukturcharakteristika digitaler Systeme umfaßt. Die Syntax von VHDL entspricht der einer imperativen Programmiersprache, wie folgende Beispielbeschreibung der Antivalenz-Funktion (negiertes Exklusiv-Oder) andeutet.

#### Beispiel 1.1: VHDL-Beschreibung der Antivalenz

```

- Deklaration der äußeren Schnittstelle

entity Antivalenz is port (A: in Bit; B: in Bit; C: out Bit);

end Antivalenz;

architecture Structure of Antivalenz is

- Deklaration lokaler Komponenten

component Inverter port (In: in Bit; Out: out Bit);

end component;

component Nandgate port (In1: in Bit; In2: in Bit; Out: out Bit);

end component;

- Deklaration interner Signale

signal s1, s2, s3, s4: Bit;

begin

- Liste der Instanzen mit Abbildungen ihrer Anschlüsse

I1: Inverter port map (In1 \Rightarrow A, Out \Rightarrow s1);

I2: Inverter port map (In1 \Rightarrow B, Out \Rightarrow s2);

I3: Nandgate port map (In1 \Rightarrow A, In2 \Rightarrow s2, Out \Rightarrow s3);

I4: Nandgate port map (In1 \Rightarrow B, In2 \Rightarrow s1, Out \Rightarrow s4);

I5: Nandgate port map (In1 \Rightarrow s3, In2 \Rightarrow s4, Out \Rightarrow C);

end Structure;

```

Am Kopf der Beschreibung wird die äußere Schnittstelle der Gesamtschaltung angegeben. Der nächste Block enthält die Schnittstellen der in Bibliotheken oder anderen VHDL—Beschreibungen definierten Komponenten. Zusätzlich können interne Signale definiert werden. Danach wird die Verbindungsstruktur der Schaltung angegeben. Die mit I1 markierte Zeile legt fest, daß eine Instanz eines Inverters verwendet wird. Dessen Ausgang Out wird über das interne Signal s1 auf den Eingang In2 des Nandgates in Zeile I4 geschaltet.

Die Darstellung einer Schaltung auf Basis von Hardwarebeschreibungssprachen hat aber entscheidende Nachteile. Einerseits läßt sich topologische Information über eine Schaltung nur sehr schwer von Hand aus einer rein textuellen Beschreibung extrahieren. Zum Verständnis der Schaltungsfunktion bei großen Schaltungen ist aber neben der textuellen Beschreibung die Darstellung in Form eines Schaltbildes oft sehr hilfreich. Andererseits ist es für den Entwerfer schwer, einen Bezug zwischen seiner Eingabe und den von Entwurfswerkzeugen gelieferten Resultaten herzustellen. Im allgemeinen hat

man keine übersichtliche Darstellung der Ergebnisse, womit die Lokalisierung entwurfskritischer Stellen schwierig und zeitaufwendig ist. Dies gilt insbesondere, wenn eine hierarchische Schaltkreiseingabe intern in eine flache Darstellung transformiert werden muß, wie dies in der Regel bei Simulationswerkzeugen üblich ist. So liefert beispielsweise der Logiksimulator HILO ([Gen90]) der Firma GenRad seine Simulationsergebnisse in Form von Zeitdiagrammen. Die Zuordnung eines Diagrammes zu einem Signalnetz erfolgt dabei über die Namen von Bausteinanschlüssen, die während der Transformation der Hierarchie in die flache Darstellung eindeutig vergeben werden. Der Entwerfer muß anschließend die umgekehrte Zuordnung der Ausgabe des Simulators zu seiner hierarchischen Schaltungseingabe durchführen, was einen nicht unerheblichen Arbeitsaufwand bedeutet.

#### Graphische Beschreibungsmethode

Die Spezifikation des Schaltkreises erfolgt hier durch Interaktion mit einem graphischen Editor. Durch die graphische Eingabe wird einerseits die Struktur einer Schaltung beschrieben, wobei sowohl die Verbindungsstruktur der Module untereinander als auch topologische Information durch die Position der Module und Leitungen angegeben wird. Neben der Spezifikation der Schaltungsstruktur bieten einige Editoren auch die Möglichkeit, graphisch das Verhalten der Schaltung zu spezifizieren. Das in [DBR<sup>+</sup>88] beschriebene System Gdl erlaubt beispielsweise die Eingabe von Daten- und Kontrollfluß einer Schaltung über eine graphische Darstellung durch Petri-Netze. In den meisten Fällen wird allerdings die graphische Eingabe in ein Standardaustausch-

In den meisten Fällen wird allerdings die graphische Eingabe in ein Standardaustauschformat (VHDL, EDIF oder andere) umgesetzt, so daß das in der topologischen Information enthaltene Entwerferwissen für die weiteren Entwurfsschritte nicht ausgenutzt wird. Solche Editoren werden bei einigen kommerziellen Entwurfssystemen als Frontend eingesetzt, wie z.B. TANGATE ([SYS90]) oder VENUS ([HNS86]). Obwohl diese Editoren in der Regel den hierarchischen Entwurf unterstützen, können sie dennoch keine komfortable Eingabemöglichkeit für sehr große Schaltkreise gewährleisten. Ein Hauptgrund dafür ist, daß sie entweder gar nicht oder nur in sehr eingeschränkter Form die Ausnutzung von Regularitäten in großen Schaltungen erlauben. Der Entwerfer wird zwar von manchen Entwurfssystemen durch Generatoren für bestimmte reguläre Teilschaltungen, wie beispielsweise Speichermodule, unterstützt. Er kann diese Generatoren aber nur für eine beschränkte Auswahl aus vorgegebenen Parameterwerten aufrufen und damit nicht jede beliebige Ausprägung eines solchen Moduls in seinem Entwurf verwenden.

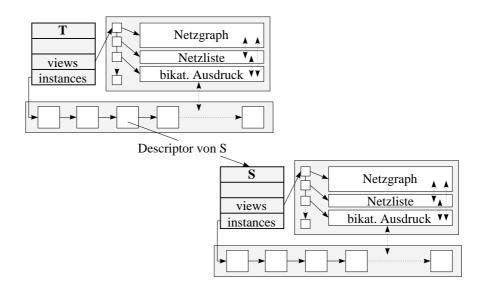

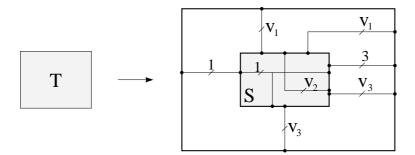

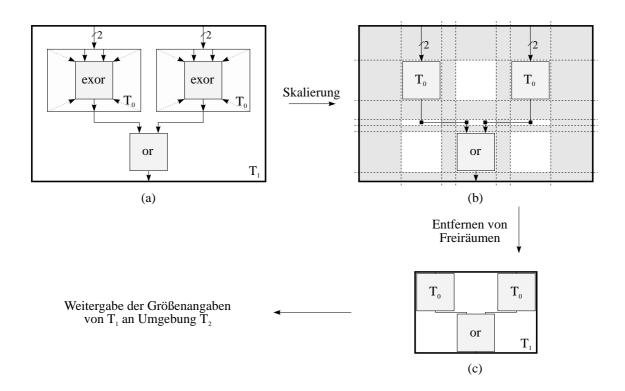

Das in [CF86] beschriebene Layoutsystem ESCHER ermöglicht die parametrisierte graphische Eingabe von Schaltungen, die auch rekursiv definiert werden können. Innerhalb einer parametrisierten Teilschaltung dürfen Gruppen von Zellen spezifiziert werden, die vergleichbar sind mit eindimensionalen Feldern in einer Programmiersprache. Jede einzelne Komponente einer solchen Gruppe wird durch einen eindeutigen Index identifiziert, der innerhalb der Gruppe von links nach rechts beziehungsweise von oben nach unten wächst. Anfangs- und Endwert können von einem Schaltkreispa-

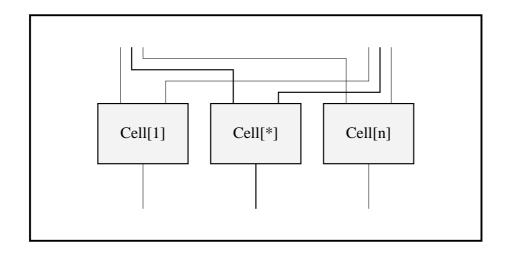

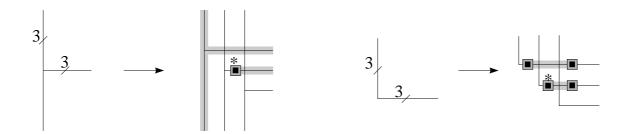

rameter abhängen, das Inkrement muß aber eine feste positive natürliche Zahl sein. Eine Gruppe, deren Länge von einem freien Parameter n abhängt, wird durch drei Zellen graphisch repräsentiert (vgl. Abbildung 1.2). Es wird jeweils eine Zelle für den Anfangs- und den Endwert eingegeben, zwischen denen eine weitere Zelle mit Index \* plaziert ist. Diese repräsentiert alle Zellen mit Indizes zwischen Anfangs- und Endwert, vergleichbar mit einer Ellipse " $i=1,\ldots,n$ ". Die an dem mit \* gekennzeichneten Baustein angeschlossenen Leitungen repräsentieren alle Leitungen der ersetzten Instanzen.

Abbildung 1.2: Darstellung einer Gruppe von n Zellen in ESCHER

Die Nachteile von ESCHER folgen aus der Tatsache, daß die Beschreibungsebene nicht auf einem wohldefinierten mathematischen Kalkül basiert. Dies äußert sich darin, daß die Topologie der Verdrahtung zwischen mehreren Gruppen von Zellen, wie sie in Abbildung 1.2 gegeben sind, nicht eindeutig ist. Darüberhinaus unterstützt ESCHER nur Rekursionen in einem Parameter. Dies stellt eine unangenehme Einschränkung dar, weil sich viele für die Praxis relevante Schaltkreise auf natürliche Weise durch Rekursion über mehreren Parametern beschreiben lassen. Ein bekanntes Beispiel hierfür ist die Beschreibung eines Wallace-Tree Multiplizierers ([Wal64]), für die von Luk und Vuillemin in [LV83] eine für den VLSI-Entwurf geeignete rekursive Darstellung in zwei Parametern angegeben wird.

Die beiden gewohnten Ansätze zur Beschreibung von Schaltkreisen besitzen also sowohl Vor- als auch Nachteile. Wir beschreiben im folgenden eine Spezifikationsebene, die die Übersichtlichkeit der graphischen Darstellung mit der Flexibilität textueller Beschreibungssprachen kombiniert. Die gewählte Grundlage eines wohldefinierten mathematischen Kalküls erweist sich als mächtiges Werkzeug zur parametrisierten Beschreibung äußerst großer Schaltkreise. Sie gestattet insbesondere eine von Basisoperationen unabhängige Spezifikation, wie sie zur Zeit von keiner anderen Beschreibungssprache unterstützt wird. Sie erhöht damit die Wiederverwendbarkeit von Teilschaltungen in an-

deren Entwürfen. Der Entwerfer kann beispielsweise einen Sortieralgorithmus zunächst unabhängig vom Typ und der Kodierung der zu sortierenden Elemente eingegeben. Der Typ der Elemente wird anschließend durch die Vergleichsfunktion festgelegt, die beliebig austauschbar ist.

#### 1.2 Grundlagen des Netzkalküls

Die Beschreibungsebene des graphischen Editors basiert auf der Darstellung von Schaltkreisen in einem Kalkül, der im Teilprojekt B1 des SFB 124 als Grundlage einer Programmiersprache zum Entwurf von integrierten Schaltkreisen entwickelt wurde. Dabei will man neben der logischen Struktur eines Schaltkreises auch Informationen über dessen geometrische Leitungsführung erfassen. Die Eigenschaften dieses Kalküls, dessen Grundlagen in [Hot65], [Hot74] vorgestellt wurden, sind in [Mol86], [Mol88] ausführlich beschrieben. Es werden nun die für die vorliegende Arbeit wichtigsten Aspekte gezeigt.

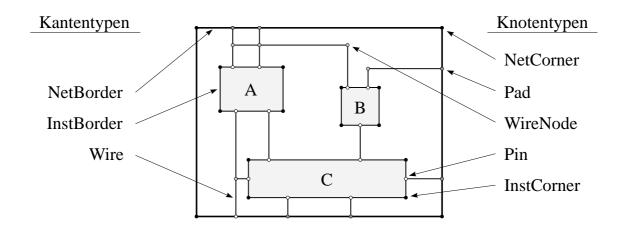

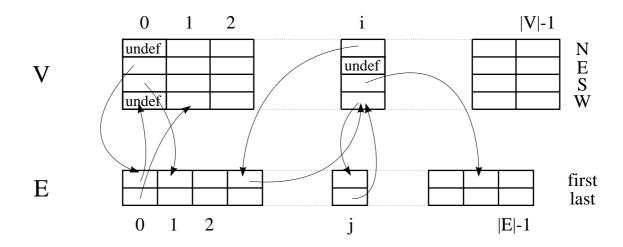

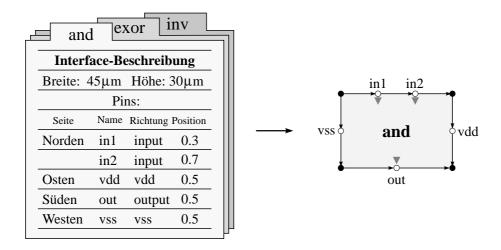

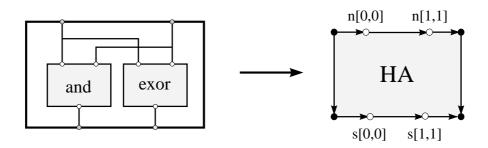

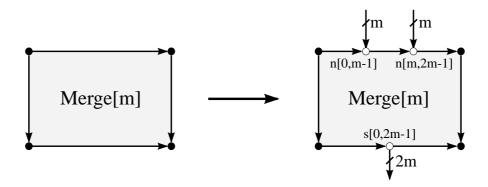

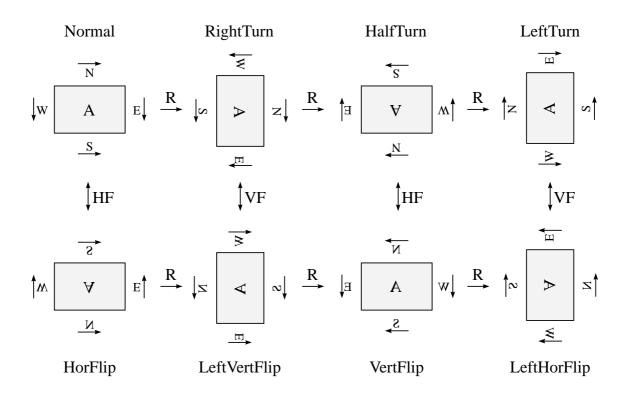

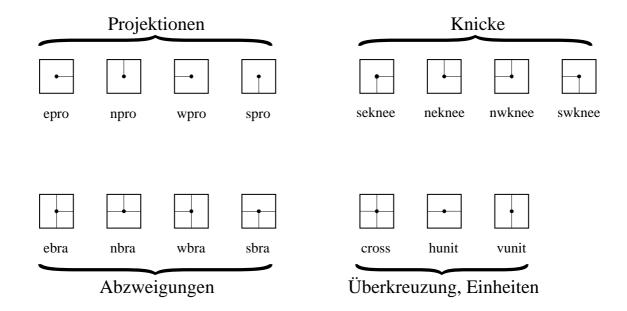

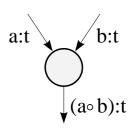

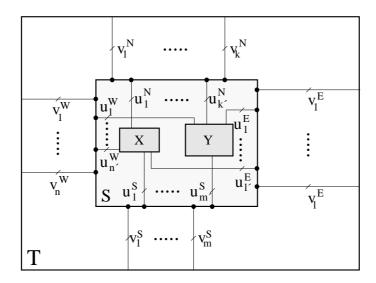

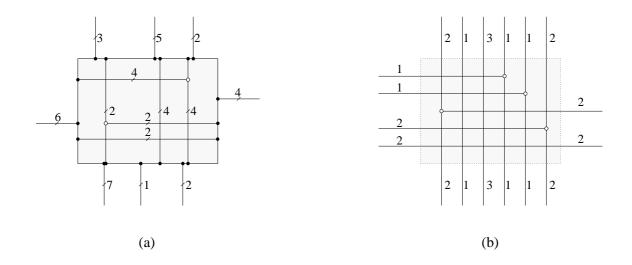

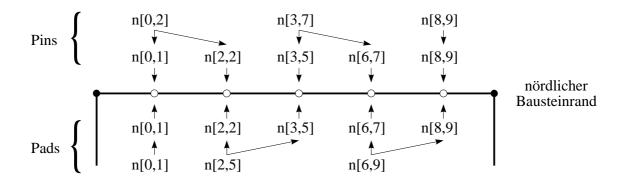

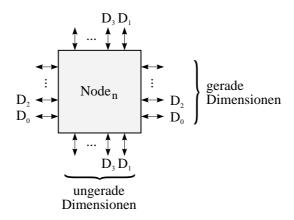

#### 1.2.1 Die Bikategorie der logisch-topologischen Netze

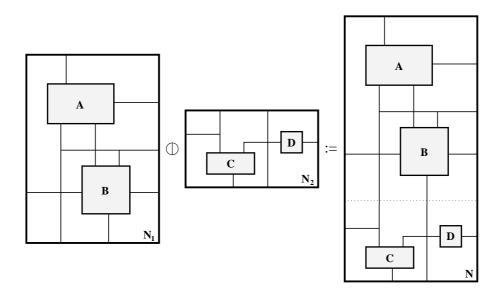

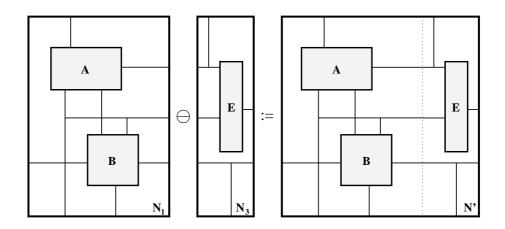

Es werden verschiedene Abstraktionen zur Beschreibung von integrierten Schaltkreisen vorgenommen: Der Schaltkreis wird in ein Rechteck R ausgelegt, auf dessen Rand sich die äußeren Anschlüsse der Schaltung befinden. Er besteht aus Leitungen und Bausteinen, die durch die Leitungen miteinander verbunden werden. Man projiziert das Layout in die euklidische Ebene und abstrahiert so von den verschiedenen Schichten, in denen die Leitungen geführt werden. Um eine planare Beschreibung zu erhalten, faßt man Abzweigungen und Überkreuzungen von Leitungen ebenfalls als Bausteine auf. Weiterhin wird von Leitungsbreiten abstrahiert. Zusätzlich betrachtet man Leitungen als Polygonzüge, die überkeuzungs- und überlappungsfrei in der Ebene verlaufen. Jeder Baustein hat, wie auch das umschließende Rechteck R der Schaltung, eine nördliche, östliche, südliche und westliche Seite. Dies bedeutet insbesondere, daß alle in R enthaltenen Bausteine parallel zu den Seiten von R ausgerichtet sind. Jeder Zelle ist dabei ein Name zugeordnet. Zellvorkommen mit dem gleichen Namen haben auf jeweils derselben Seite die gleiche Anzahl und Reihenfolge von Anschlüssen. Diese Art der Beschreibung eines Schaltkreises wird als logisch-topographisches Netz bezeichnet. Zur Beschreibung von größeren Netzen werden zwei einfache Operationen auf logischtopographischen Netzen definiert. Seien dazu  $N_1$  und  $N_2$  zwei logisch-topographische Netze. Dann ist das Übereinandersetzen (vgl. Abbildung 1.3) von  $N_1$  und  $N_2$  zu N:= $N_1 \oplus N_2$  genau dann definiert, wenn die südliche Seite von  $N_1$  und die nördliche Seite von  $N_2$  aufeinander passen. Die formale Fassung des Begriffes "aufeinander passen" erfolgt im Anschluß an diese informalen Erläuterungen.

Analog kann man das Nebeneinandersetzen (vgl. Abbildung 1.4) von  $N_1$  und  $N_2$  zu  $N := N_1 \ominus N_2$  definieren genau dann, wenn die östliche Seite von  $N_1$  mit der westlichen Seite von  $N_2$  zusammenpaßt. Als Resultat erhält man das Netz, das entsteht, wenn man die beiden Teilnetze an den betreffenden Seiten miteinander verklebt, d.h. die

Abbildung 1.3: Übereinandersetzen von zwei logisch-topographischen Netzen

Anschlußpunkte auf den beiden Seiten miteinander identifiziert und anschließend die beiden Seitenränder löscht. Mit Hilfe dieser Operationen könnte man nun, ausgehend von einer Menge von Grundbausteinen, Verdrahtungselementen und Leitungsstücken, logisch-topographische Netze sukzessive zusammenbauen.

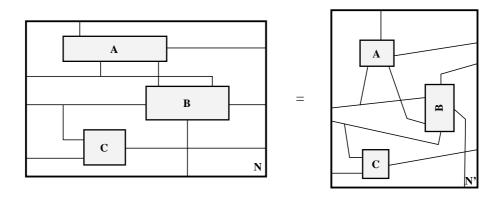

Abbildung 1.4: Nebeneinandersetzen von zwei logisch-topographischen Netzen

Ein Nachteil dieser Vorgehensweise liegt darin, daß man eine genaue Beschreibung der Topographie des zu konstruierenden Netzes benötigt. Man geht deshalb noch einen Schritt weiter und faßt zwei logisch-topographische Netze als äquivalent auf, wenn sie sich durch Anwendung einer Folge von elementaren Deformationsschritten ineinander

überführen lassen. Als elementare Deformationen sind hier Deformationen von Leitungen, Ähnlichkeitstransformationen, Verschieben, Drehen, Dehnen und Stauchen von Zellen sowie das Verschieben von Anschlüssen auf dem Rand eines Bausteines oder des Netzes erlaubt. Diese Deformationen sind nur dann zugelassen, wenn dadurch die Anzahl und Reihenfolge der Anschlüsse auf den Rändern nicht verändert wird. Ebenfalls dürfen durch diese Deformationen keine neuen Überkreuzungen von Leitungen generiert werden und alle Zwischenresultate müssen legale logisch-topographische Netze sein, d.h. es dürfen keine Überlappungen generiert werden. Eine genaue Beschreibung der erlaubten Deformationen findet sich in [Mol86].

Abbildung 1.5: Zwei Repräsentanten eines logisch-topologischen Netzes

Unter Berücksichtigung dieser Menge von Deformationen sind also die beiden in Abbildung 1.5 gezeigten Netze als äquivalent anzusehen. Mit der so gegebenen Äquivalenzrelation auf den logisch-topographischen Netzen erhält man eine Klasseneinteilung. Eine Klasse von logisch-topographischen Netzen bezeichnet man als logisch-topologisches Netz und jedes Element der Klasse als einen Repräsentanten. Das Übereinander- und Nebeneinandersetzen läßt sich auf logisch-topologische Netze erweitern, indem man, falls sie existieren, zwei geeignete Repräsentanten gemäß den oben angestellten Überlegungen miteinander verknüpft und das Resultat wiederum als Repäsentant eines logisch-topologischen Netzes betrachtet. Man sieht leicht, daß die beiden Operationen genau dann definiert sind, wenn die Anzahl der Anschlüsse auf den betreffenden Seiten der beteiligten logisch-topologischen Netze übereinstimmt. Oft will man aber nicht nur die Anzahl der Anschlüsse betrachten, sondern den einzelnen Leitungen eine Semantik innerhalb der Schaltungsbeschreibung zuordnen. Dies erfolgt mit Hilfe von Signaltypen, die jeder Leitung zugewiesen werden können. In diesem Falle sind die Operationen genau dann definiert, wenn die Folgen der Signaltypen in der Reihenfolge von links nach rechts (Übereinandersetzen) beziehungsweise von oben nach unten (Nebeneinandersetzen) an den betreffenden Seiten übereinstimmen.

Das bisher informal Beschriebene läßt sich wie folgt formalisieren: Seien A eine endliche Menge von Grundbausteinen und O eine endliche Menge von Signaltypen. Dann

bezeichnen wir mit Net(O, A) die Menge der logisch-topologischen Netze über Grundbausteinen aus A und Signaltypen aus O. Falls nur die Anzahl der Anschlüsse berücksichtigt werden soll, schreiben wir kurz Net(A). Dann geben die Abbildungen

$$N, E, S, W : Net(O, A) \to O^*$$

beziehungsweise  $N, E, S, W : Net(A) \to \mathbb{N}_0$

die Wörter über den Signaltypen der nördlichen, östlichen, südlichen und westlichen Seite, von links nach rechts beziehungsweise von oben nach unten gelesen, beziehungsweise die Anzahl der Anschlüsse an den betreffenden Seiten wieder.

**Definition 1.2:** ([Hot65]) Seien O, M Mengen,  $Q, Z : M \to O$  zwei Abbildungen und  $\circ: M \times M \to M$  eine partielle Verknüpfung. Dann heißt  $K = (O, M, Q, Z, \circ)$  eine Kategorie, falls gilt:

- $(K_1) \ \forall f,g \in M : f \circ g \ ist \ genau \ dann \ definiert, \ wenn \ Z(f) = Q(g)gilt.$

- $(K_2) \ \forall f,g \in M \ mit \ Z(f) = Q(g) : Q(f \circ g) = Q(f) \ und \ Z(f \circ g) = Z(g).$

- $(K_3) \ \forall f, g, h \in M : f \circ (g \circ h) = (f \circ g) \circ h$ , falls die Ausdrücke definiert sind.

$$(K_4) \ \forall w \in O \ \exists 1_w^{\circ} \in M \ \forall f, g \in M \ mit \ Q(f) = w, Z(g) = w : 1_w \circ f = f, \ g \circ 1_w = g.$$

O heißt Objektmenge und M Morphismenmenge von

$$K$$

.

**Bezeichnungen:** Sei  $(O, \circ)$  ein freies Monoid, dann bezeichne  $\varepsilon$  die Einheit und  $E_O$  das freie Erzeugendensystem von  $(O, \circ)$ . Für  $w_1, \ldots, w_n \in E_O$  ist

$$(w_1 \circ \cdots \circ w_n)^{-1} := w_n \circ \cdots \circ w_1 \text{ und } \varepsilon^{-1} := \varepsilon.$$

Für  $a \in E_O, v \in O$  ist

$$\mathbf{r}_{\varepsilon} = \mathbf{1}_{\varepsilon}^{\bullet}, \, \mathbf{r}_{a \circ v} = \mathbf{r}_{a} \oplus (\mathbf{1}_{a}^{\bullet} \ominus \mathbf{r}_{v}), \quad \mathbf{r}_{\varepsilon} = \mathbf{1}_{\varepsilon}^{\bullet}, \mathbf{r}_{a \circ v} = \mathbf{r}_{a} \oplus (\mathbf{L}_{v} \ominus \mathbf{1}_{v}^{\bullet})$$

$$\mathbf{L}_{\varepsilon} = \mathbf{1}_{\varepsilon}^{\bullet}, \, \mathbf{L}_{a \circ v} = (\mathbf{1}_{a}^{\bullet} \ominus \mathbf{L}_{v}) \oplus \mathbf{L}_{a}, \quad \mathbf{L}_{\varepsilon} = \mathbf{1}_{\varepsilon}^{\bullet}, \mathbf{L}_{a \circ v} = (\mathbf{L}_{a} \ominus \mathbf{1}_{v}^{\bullet}) \oplus \mathbf{L}_{v}$$

**Definition 1.3:** [Mol86] Eine Bikategorie B ist ein 8-Tupel  $(O, M, N, S, W, E, \Phi, \Theta)$ , für das folgende Axiome gelten:

- $(B_1)$   $(O, M, N, S, \oplus)$  ist eine Kategorie.

- $(B_2)$   $(O, M, W, E, \Theta)$  ist eine Kategorie.

- $(B_3)$   $(O, \circ)$  ist ein freies Monoid, wobei  $\varepsilon$  die Einheit und  $E_O$  das freie Erzeugendensystem in  $(O, \circ)$  bezeichne.

- $(B_4) \ \forall F, G \in M \ mit \ S(F) = N(G) \ gilt:$  $E(F \oplus G) = E(F) \circ E(G) \ und \ W(F \oplus G) = W(F) \circ W(G).$

- $(B_5) \ \forall F, G \in M \ mit \ E(F) = W(F) \ gilt:$  $N(F \ominus G) = N(F) \circ N(G) \ und \ S(F \ominus G) = S(F) \circ S(G).$

- $(B_6) \ \forall \, v,w \in O \ \textit{gilt:} \ 1^{\bullet}_v \ominus 1^{\bullet}_w = 1^{\bullet}_{v \circ w} \ \textit{und} \ 1^{\bullet}_v \oplus 1^{\bullet}_w = 1^{\bullet}_{v \circ w}.$

- $(B_7) \ \forall F_1, F_2, G_1, G_2 \in M \ mit \ S(F_1) = N(G_1), S(F_2) = N(G_2), \ E(F_1) = W(F_2) \ und \ E(G_1) = W(G_2) \ gilt:$   $(F_1 \ominus F_2) \oplus (G_1 \ominus G_2) = (F_1 \oplus G_1) \ominus (F_2 \oplus G_2) \ (Distributivgesetz)$

- $(B_8) \ \forall a \in E_O \ \exists \ \lrcorner_a, \, \llcorner_a, \, \lnot_a \in M, \ so \ da\beta \ gilt:$  $\ulcorner_a \ominus \lrcorner_a = 1^{\bullet}_a = \, \llcorner_a \ \ominus \lnot_a \ und \ \ulcorner_a \ominus \ \lrcorner_a = 1^{\bullet}_a = \lnot_a \ominus \, \llcorner_a.$

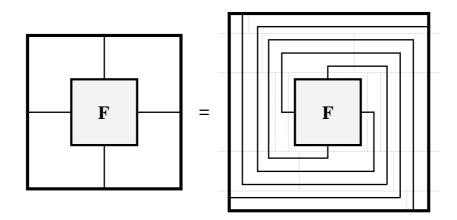

Das Axiom  $(B_9)$  steht für die Drehung eines Netzes um  $360^{\circ}$  Grad gegen den Uhrzeigersinn, wie es in Abbildung 1.6 gezeigt wird. Man sieht hier unter anderem, daß die Darstellung eines Netzes als Ausdruck über der Bikategorie im Vergleich zu einer graphischen Beschreibung sehr leicht unüberschaubar wird.

Abbildung 1.6: Drehung eines Netzes gegen den Uhrzeigersinn

Sei  $B = (O, M, N, S, W, E, \oplus, \Theta)$  eine Bikategorie. Analog zu Definition 1.1 bezeichnen wir die Elemente von O als Objekte und die Elemente von M als Morphismen von B.

durch arithmetische Ausdrücke unter Anwendung elementarer Rechenregeln beschreiben kann. In [Mol86] wird dazu gezeigt, daß

$$NET(A) = (\mathbf{IN}_0, Net(A), N, S, W, E, \Phi, \Theta)$$

beziehungsweise

$$NET(O, A) = (O^*, Net(O, A), N, S, W, E, \oplus, \ominus)$$

Bikategorien sind. Von entscheidendem Interesse ist hier die Frage nach einem Erzeugendensystem für NET(A) beziehungsweise NET(O, A), und ob ein freies Erzeugendensystem existiert. Eine Formalisierung dieses Begriffes erfolgt zunächst in den folgenden Definitionen:

**Definition 1.4:** ([Mol86]) Sei  $B = (O, M, N, S, W, E, \oplus, \ominus)$  eine Bikategorie,  $P \subset M$ ,  $\Sigma = P \cup \{1_w^{\bullet}, 1_w^{\bullet}, \neg, \vdash, \dashv, \vdash | w \in O\} \cup \{\oplus, (,)\}$  und sei  $\Sigma^*$  das freie Monoid über  $\Sigma$ . Dann heißt der Durchschnitt aller Mengen  $L \subset \Sigma^*$  mit

- $(1) \ P \cup \{1_w^{\bullet}, 1_w^{\bullet}, \Gamma_w, \Gamma_w, \Gamma_w, \Gamma_w, \Gamma_w \mid w \in O\} \subset L$

- (2) Sind  $w_1, \ldots, w_k \in L$ , dann ist auch  $(w_1 \oplus \ldots \oplus w_k) \in L$ , falls dieser Ausdruck für die beschriebenen Morphismen definiert ist.

- (3) Sind  $w_1, \ldots, w_k \in L$ , dann ist auch  $(w_1 \ominus \ldots \ominus w_k) \in L$ , falls dieser Ausdruck für die beschriebenen Morphismen definiert ist.

die Menge der bikategoriellen Ausdrücke über P.

**Definition 1.5:** ([Mol86]) Sei  $B = (O, M, N, S, W, E, \oplus, \ominus)$  eine Bikategorie. Eine Menge  $P \subset M$  heißt Erzeugendensystem von B, falls sich jeder Morphismus aus M durch einen bikategoriellen Ausdruck über P darstellen läßt.

**Definition 1.6:** ([Mol86]) Zwei bikategorielle Ausdrücke heißen gleichartig, wennn sie sich mit den Axiomen der Bikategorie ineinander überführen lassen. Ein Erzeugendensystem P heißt frei, wenn zwei bikategorielle Ausdrücke über P genau dann den gleichen Morphismus beschreiben, wenn sie gleichartig sind.

In [Mol86] wird gezeigt, daß A sowohl freies Erzeugendensystem von NET(A) als auch von NET(O, A) ist. Im folgenden werden wir bei freien Bikategorien stets bikategorielle Ausdrücke über einem freien Erzeugendensystem betrachten.

Mit der bisher beschriebenen Methode hätte man Schwierigkeiten bei der Beschreibung sehr großer Schaltungen mit mehreren tausend Bausteinen, da die Darstellung einer Schaltung mittels bikategorieller Ausdrücke äußerst groß und unüberschaubar wird. Man nutzt nun aus, daß große Schaltungen oft regelmäßige Teilstrukturen beinhalten. Dazu kommt, daß derselbe Teilschaltkreis meist vielfach zum Aufbau einer komplexen Schaltung herangezogen wird, woraus man eine hierarchische Spezifikation ableiten kann. In der Sprache der Bikategorien bedeutet dies, daß man angeben muß,

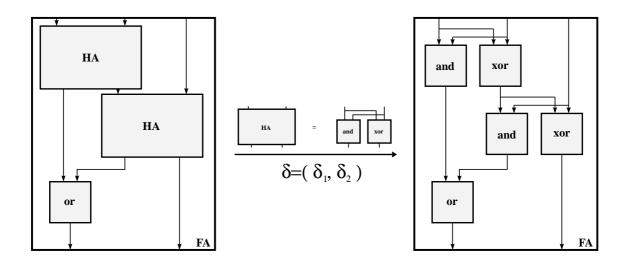

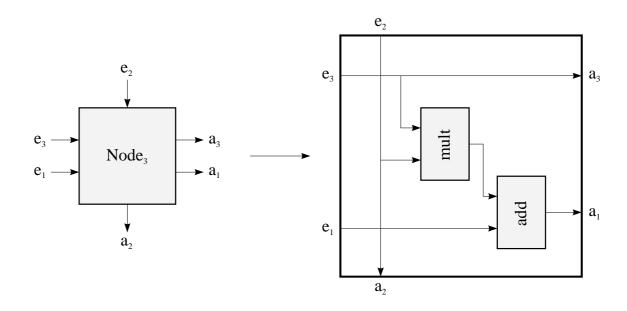

wie einem Netz über einem Bausteinsystem A ein Netz über einem Bausteinsystem B zuzuordnen ist, indem man eine genaue Beschreibung der Bausteine aus A als Netze über Bausteinen aus B angibt. Diese Zuordnung erfolgt unter Verwendung einer strukturerhaltenden Abbildung zwischen Bikategorien, die wir im folgenden als Bifunktorbezeichnen. Abbildung 1.7 zeigt ein einfaches Beispiel hierfür.

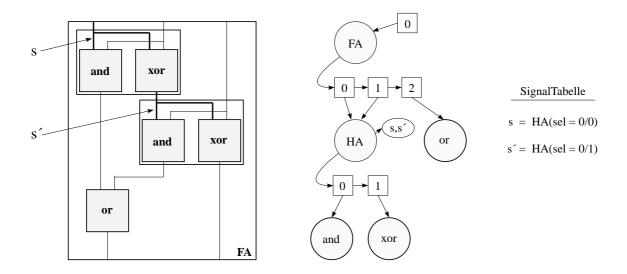

Abbildung 1.7: Anwendung des Bifunktors am Beispiel eines Volladdierers

**Definition 1.7:** ([Mol86]) Seien  $B_i = (O_i, M_i, N_i, S_i, W_i, E_i, \Phi_i, \Theta_i) (i = 1, 2)$  zwei Bikategorien. Wir nennen  $\delta = (\delta_1, \delta_2)$  Bifunktor von  $B_1$  nach  $B_2$ , falls gilt:

- (a)  $\delta_1: (O_1, \circ_1) \to (O_2, \circ_2)$  ist ein Monoidhomomorphismus,  $\delta_2: M_1 \to M_2$  ist eine Abbildung.

- (b)  $\delta_2$  erfüllt folgende Bedingungen:

(b1)

$$\forall F, G \in M_1 \text{ mit } S_1(F) = N_1(G) \text{ gilt: } \delta_2(F \oplus_1 G) = \delta_2(F) \oplus_2 \delta_2(G)$$

(b2)

$$\forall F, G \in M_1 \text{ mit } E_1(F) = W_1(G) \text{ gilt: } \delta_2(F \ominus_1 G) = \delta_2(F) \ominus_2 \delta_2(G)$$

(c) Das folgende Diagramm ist kommutativ:

$$\begin{array}{ccc} M_1 & \stackrel{N_1,S_1,W_1,E_1}{\longrightarrow} & O_1 \\ \delta_2 \downarrow & & \downarrow \delta_2 \\ M_2 & \stackrel{N_2,S_2,W_2,E_2}{\longrightarrow} & O_2 \end{array}$$

$$(d) \ \forall \, w \in O_1: \ \delta_2(1_w^{\ \oplus \ _2}) = 1_{\delta_1(w)}^{\ \oplus \ _1}, \ \delta_2(1_w^{\ \ominus \ _2}) = 1_{\delta_1(w)}^{\ \ominus \ _1}.$$

Bifunktoren lassen sicht leicht auf bikategoriellen Ausdrücken berechnen, wenn die Bilder der Erzeugenden bekannt sind. Dies ergibt sich aus den beiden letzten Definitionen, da man einen bikategoriellen Ausdruck für F in einen Ausdruck für  $\delta_2(F)$  übersetzen kann, indem man alle Vorkommen  $p \in P$  durch Ausdrücke für  $\delta_2(p)$  ersetzt, wobei P freies Erzeugendensystem der Bikategorie  $B_1$  ist. In [Mol86] wird gezeigt, daß die Verfeinerung der Netze  $r_a, r_a, r_a$  für  $a \in O$  bereits durch  $\delta_1$  eindeutig bestimmt ist. Die Spezifikation eines Bifunktors besteht also im wesentlichen aus der Definition von  $\delta_1(O)$  und  $\delta_2(A)$ . Unter Anwendung von Bifunktoren kann man auf sehr kompakte Weise hierarchische Schaltungsbeschreibungen spezifizieren.

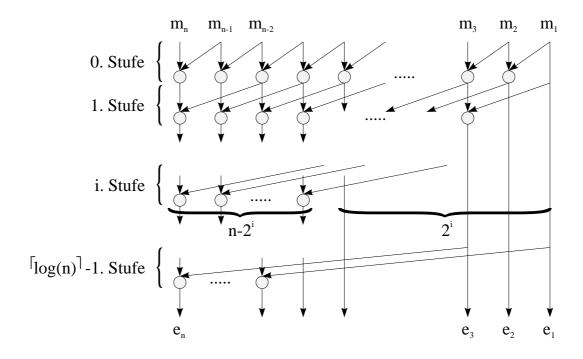

#### 1.2.2 Rekursive Netzgleichungssysteme

Wir geben nun eine Spezifikationsmethode für Schaltkreise an, die auf dem im vorangegangenen Abschnitt vorgestellten Kalkül basiert. Diese Methode nutzt aus, daß sich Schaltkreise oft besonders kurz und überschaubar definieren lassen, wenn der von ihnen berechneten Funktion ein rekursives Schema zugrunde liegt. Dazu gehören Schaltkreise, die arithmetische Funktionen berechnen wie etwa Addier- und Multiplizierwerke, aber auch Sortiernetzwerke oder andere regelmäßige Strukturen, beispielsweise Speichermodule. Rekursive Beschreibungen von Schaltungen bilden, basierend auf dem mathematischen Kalkül der Bikategorien, ein mächtiges Werkzeug beim Entwurf von sehr großen integrierten Schaltkreisen.

Wir werden nun zunächst Gleichungssysteme über logisch-topologischen Netzen beschreiben und dabei besonders auf rekursive Gleichungen eingehen. Anhand von einfachen Beispielen soll die Mächtigkeit dieser Beschreibungstechnik verdeutlicht werden.

**Definition 1.8:** ([Kol86]) Sei NET (O, A) eine freie Bikategorie logisch-topologischer Netze, und sei V eine Menge von Unbestimmten. Sei weiter R eine Menge von Gleichungen der Form l=r, wobei l,r bikategorielle Ausdrücke über Bausteinen aus A und Unbestimmten aus V darstellen. Dann heißt G=(V,R) ein Gleichungssystem über NET (O,A) mit Unbestimmten aus V.

Sei  $\zeta: V \to \operatorname{Net}(O, A)$  eine beliebige Abbildung, die jeder Unbestimmten aus V ein Netz aus Net(O, A) zuordnet. Man betrachte die freie Bikategorie NET $(O, A \cup V^{\zeta})$ , die man erhält, indem man alle Elemente aus V als Bausteine hinzunimmt und

$$N, S, E, W(X) := N, S, E, W(\zeta(X))$$

für alle  $X \in V$  setzt. Dann definiert  $\zeta$  einen Bifunktor

$$\tau = (\tau_1^{\zeta}, \tau_2^{\zeta}) : NET(O, A \cup V^{\zeta}) \rightarrow NET(O, A) \ mit$$

(1)  $\tau_1^{\zeta}$  ist Identität auf O und

(2)

$$\tau_2^{\zeta}(X) := \begin{cases} X & falls \ X \in A \\ \zeta(X) & falls \ X \in V \end{cases}$$

$\zeta$  hei $\beta$ t Lösung von G genau dann, wenn für jede Gleichung  $l = r \in R$  gilt:  $\tau_2^{\zeta}(l) = \tau_2^{\zeta}(r)$ . Wir nennen  $\tau^{\zeta}$  den Einsetzungsfunktor von  $\zeta$ . Ein Gleichungssystem hei $\beta$ t (eindeutig) lösbar, wenn es (genau) eine Lösung besitzt.

Hier wird also das, was man allgemein unter einem Gleichungssystem versteht, auf Netze übertragen. Dabei hat man eine Menge von Gleichungen, die durch Gleichsetzen von bikategoriellen Ausdrücken über Konstanten und Unbestimmten gegeben sind. Eine Lösung stellt dann eine Einsetzung für die Unbestimmten dar, bei der alle Gleichungen erfüllt sind.

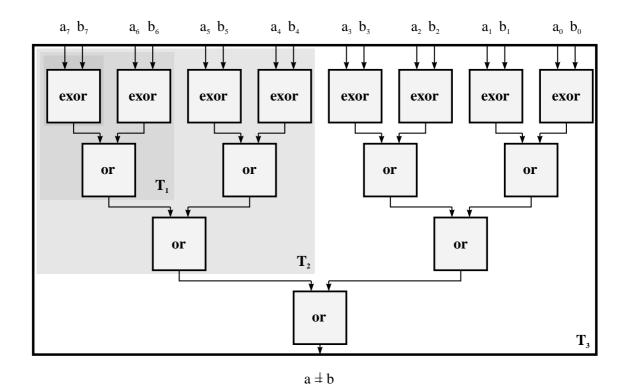

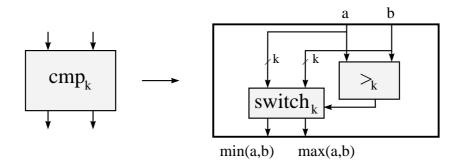

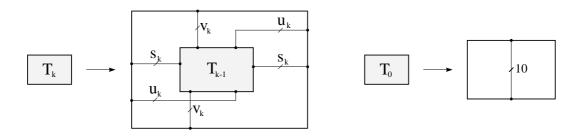

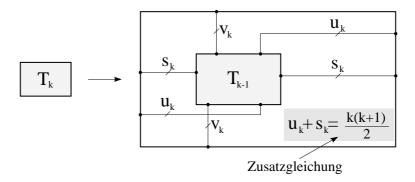

#### Beispiel 1.9: Gleichungssystem für einen binären Vergleichsbaum

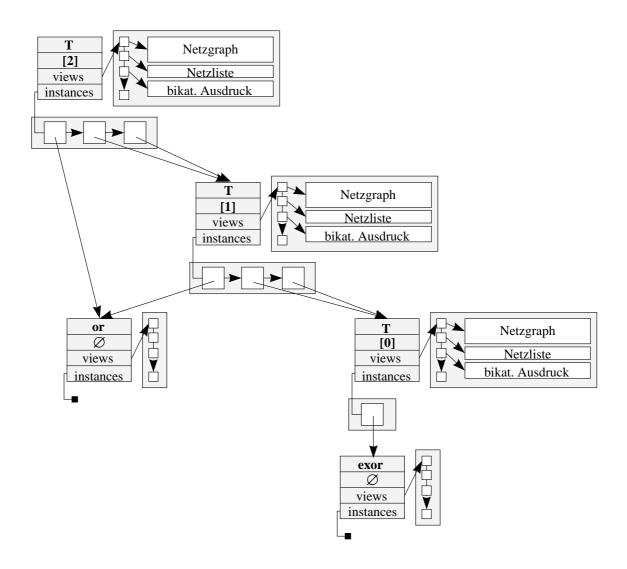

$$V = \{T_i \mid i \in \mathbb{N}_0\}, R = \{T_i = (T_{i-1} \ominus T_{i-1}) \oplus \text{ or } | i \ge 1\} \cup \{T_0 = \text{ exor } \}$$

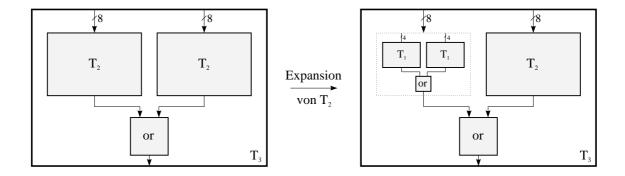

Dieses einfache Gleichungssystem ist eindeutig lösbar und definiert für  $T_i$  einen vollständigen binären Vergleichsbaum, wobei die  $2^i$  Blätter durch exor-Gatter und die inneren Knoten durch or-Gatter gebildet werden. Abbildung 1.8 zeigt die graphische Darstellung der Lösung dieses Gleichungssystems für  $T_3$ .

Abbildung 1.8: Rekursive Beschreibung eines binären Vergleichsbaumes

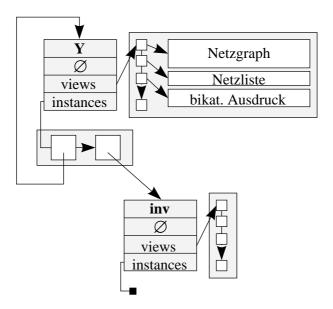

#### Beispiel 1.10: Unlösbares Gleichungsystem

$$V = \{Y\}, R = \{Y = inv \oplus Y\}$$

Dieses Gleichungssystem hat keine Lösung in Net (O, A), da die Zahl der Bausteine aus A auf der rechten Seite für jede Einsetzung stets größer ist als die Zahl der Bausteine in der für Y gewählten Einsetzung.

**Definition 1.11:** ([Kol86]) Sei G = (V, R) ein Gleichungssystem über Net (O, A). G heißt einfach genau dann, wenn jede Gleichung in R von der Form X = e ist, wobei X eine Unbestimmte und e ein bikategorieller Ausdruck über Unbestimmten aus V und Bausteinen aus A ist, und wenn es zu jeder Unbestimmten  $X \in V$  höchstens eine solche Gleichung gibt.

In [Kol86] wird gezeigt, daß für ein lösbares Gleichungssystem nach k-facher Iteration des Expansionsfunktors ein Ausdruck über Net(O,A) erzeugt werden kann. In Abschnitt 1.3.1 zeigen wir, welche syntaktischen Konstrukte zur Definition rekursiver Gleichungssysteme verwendet werden dürfen. Es soll dabei ein einfacher Ansatz gewählt werden, der dem Entwerfer aber auch die Beschreibung komplexer Schaltkreise auf einfache und prägnante Weise erlaubt.

**Definition 1.12:** ([Kol86]) Sei T ein beliebiges Alphabet und sei  $X[p_1, \ldots, p_n]$  mit  $p_i \in T^* \cup \mathbb{N}_0$  eine Netzvariable mit freien und konstanten Parametern  $p_1, \ldots, p_n$ . Dann beschreibt  $X[p_1, \ldots, p_n]$  eine Menge von Unbestimmten gemäß

$$X[p_1,\ldots,p_n] = \{X_{\varphi(p_1),\ldots,\varphi(p_n)} \mid \varphi(p_i) = \begin{cases} p_i, & falls \ p_i \in \mathbb{IN}_0 \\ \delta_i \in \mathbb{IN}_0, & sonst \end{cases} \}.$$

$X[p_1,\ldots,p_n]$  heißt dann Netzvariable der Dimension n mit freien und konstanten Parametern  $p_1,\ldots,p_n$ . Weiter sei  $P_X:=\{p_i\mid p_i\notin \mathbf{IN}_0\}$  die Menge der freien Parameter von  $X[p_1,\ldots,p_n]$ .

In dieser Definition ist  $\varphi: P_X \longrightarrow \mathbb{N}_0$  eine Abbildung, die den freien Parametern von X einen beliebigen Wert aus  $\mathbb{N}_0$  zuordnet. Für die konstanten Parametern von X ist  $\varphi$  durch die Identität gegeben. Es bezeichne  $e(P_X)$  einen bikategoriellen Ausdruck über Grundbausteinen und Netzvariablen, wobei für die Parameter der Vorkommen von Netzvariablen arithmetische Ausdrücke über  $p_i \in P_X$  stehen dürfen. Ist  $\varphi: P_X \longrightarrow \mathbb{N}_0$  eine Belegung der freien Parameter mit konstanten Werten, so verstehen wir unter  $e(\varphi(P_X))$  den bikategoriellen Ausdruck, den man erhält, indem jedes Vorkommen von  $p_j$  durch  $\varphi(p_j)$  ersetzt wird und die arithmetischen Ausdrücke zu konstanten Werten ausgewertet werden.

Wir unterscheiden zwei verschiedene Typen von Gleichungen, aus denen eine rekursive Schaltungsbeschreibung aufgebaut werden kann:

- (1) Allgemeine Gleichungen der Form  $X[p_1, \ldots, p_n] = e(P_X)$ , wobei  $\forall i : p_i \notin \mathbb{N}_0$ , also  $|P_X| = n$  gilt, d.h. es handelt sich um eine Netzvariable mit ausschließlich freien Parametern.

- (2) Abschlußgleichungen der Form  $X[p_1, \ldots, p_n] = e(P_X)$ , wobei  $\exists i : p_i \in \mathbb{IN}_0$ , also  $|P_X| < n$  gilt.

Als allgemeine Gleichungen werden also solche bezeichnet, bei denen sämtliche Parameter frei wählbar sind. Der Ausdruck auf der rechten Seite kann dabei auch nur eine Teilmenge dieser Parameter verwenden. Unter Abschlußgleichungen verstehen wir solche, bei denen mindestens ein Parameter mit einem konstanten Wert belegt ist.

**Definition 1.13:** ([Kol86]) Eine Abschlußgleichung  $X[p_1, \ldots, p_n] = e(P_X)$  heißt anwendbar auf  $X[\varphi(p_1), \ldots, \varphi(p_n)]$  genau dann, wenn

- (1)  $M_X^{\varepsilon} := |\{p_i \mid p_i \in \mathbb{IN}_0, p_i = \varphi(p_i)\}| = n |P_X| \text{ gilt, d.h. alle konstanten}$ Parameter müssen mit den betreffenden Werten, die durch die Belegung  $\varphi$  gegeben sind, übereinstimmen, und

- (2) für jede andere Schlußregel der Form  $X[p_1, \ldots, p_n] = e'(P_X')$  mit  $M_X^{\varepsilon'} = n |P_X'|$  gilt  $M_X^{\varepsilon'} < M_X^{\varepsilon}$ .

**Definition 1.14:** ([Kol86]) GL = (NV, AR, SR) mit

- (1) NV ist eine Menge von Netzvariablen,

- (2) AR eine Menge von allgemeinen Gleichungen über Netzvariablen aus NV und

- (3) SR eine Menge von Abschlußgleichungen über Netzvariablen aus NV

$hei\beta t$  System rekursiver Netzgleichungen, falls zu jeder Variablen  $X[p_1,\ldots,p_n] \in NV$

- (a) höchstens eine allgemeine Gleichung und

- (b) keine zwei Abschlußgleichungen  $X[p_1, \ldots, p_n]$  und  $X[p'_1, \ldots, p'_n]$  existieren, für die gilt:  $\forall p_i, p'_i \in \mathbb{IN}_0$   $p_i = p'_i$ . Zwei Abschlußgleichungen für dieselbe Netzvariable müssen sich damit an mindestens einem konstanten Parameter unterscheiden. Dann folgt mit Definition 1.13, daß immer höchstens eine anwendbare Abschlußgleichung existiert.

Über die Mächtigkeit rekursiver Netzgleichungen, d.h. die Frage, welche Teilmengen aus Net(O, A) man als Lösungen für eine Netzvariable  $X[p_1, \ldots, p_n]$  in einem rekursiven

Gleichungssystem erhalten kann, werden in [Kol86] folgende Aussagen bewiesen, die wir hier der Vollständigkeit halber angeben.

Satz 1.15: ([Kol86]) Sei  $f : \mathbb{N}_0 \to \mathbb{N}_0$  eine (turing-) berechenbare Abbildung. Dann gibt es ein lösbares rekursives Gleichungssystem  $G_f = (NV_f, AR_f, SR_f)$  mit Netzvariablen F[n] und E[n], so daß gilt:

$$\forall n \in \mathbb{IN}_0 : f(n) \text{ ist definiert } \Leftrightarrow \exists k \in \mathbb{IN}_0 : \phi_{G_f,2}^k(F[n]) = E[f(n)],$$

wobei  $\phi_{G_f}$  der Expansionsfunktor von  $G_f$  ist.

**Korollar 1.16:** ([Kol86]) Sei  $f : \mathbb{N}_0 \to Net(O, A)$  eine berechenbare Abbildung. Dann gibt es ein lösbares Gleichungssystem  $G_f$  und eine Netzvariable F[n] mit

$$f(n)$$

ist definiert  $\Leftrightarrow \exists k(n) : \phi_{G_f,2}^{k(n)}(F[n]) = f(n)$ .

Weiterhin wird in [Kol86] gezeigt, daß folgende Probleme für rekursive Netzgleichungssysteme nicht entscheidbar sind: Lösbarkeitsproblem, Existenz eines Expansionsfunktors, Terminierungsproblem und Wortproblem.

# 1.3 Graphische Eingabe von Gleichungssystemen über Netzvariablen

In [BHK<sup>+</sup>86] wird gezeigt, daß mit Hilfe der Beschreibungsmethode auf Basis des in den Abschnitten 1.2.1 und 1.2.2 vorgestellten Kalküls auch sehr große reguläre Schaltkreise durch Eingabe weniger Netzgleichungen beschrieben werden können. Dabei wird aber auch deutlich, daß die textuelle Eingabe von bikategoriellen Ausdrücke entscheidende Nachteile hat:

- die Erstellung eines Ausdruckes erfolgt durch den Entwerfer in der Regel nach Aufzeichnen des Netzes und anschließendem Zerlegen gemäß der Rechenregeln des zugrundeliegenden Kalküls. Der Übergang von der Zeichnung des Netzes zum Ausdruck stellt dabei einen Arbeitsschritt dar, der sich leicht automatisieren läßt.

- bereits für kleine Netze können große und unübersichtliche Ausdrücke entstehen.

- geringfügige Änderungen der Schaltungsstruktur ziehen unter Umständen umfangreiche Modifikationen der zugehörigen Ausdrücke nach sich. In der Regel bedeutet dies, daß der Entwerfer die Ausdrücke völlig neu erstellt, womit eine interaktive Arbeitsweise von vorneherein ausgeschlossen ist.

- die Eingabe ist äußerst fehleranfällig, insbesondere wenn im Netz aufwendige Verdrahtungsstrukturen auftreten.

- die Lokalisierung von Eingabefehlern (bezüglich der Rechenregeln des Kalküls) ist schwierig, da der Entwerfer erst wieder den Bezug zwischen seiner Zeichnung und der auf dem Ausdruck basierenden Fehlermeldung herstellen muß.

- eine Interaktion mit den weiterverarbeitenden Werkzeugen ist aus zwei entscheidenden Gründen nicht gewährleistet: Einerseits ist die Zuordnung der berechneten Resultate zur Eingabe ein zeitaufwendiger Arbeitsschritt, den der Entwerfer von Hand zu erledigen hat. Andererseits sind daraus resultierende Änderungen der Eingabe nur unter großem Aufwand durchführbar.

Es bietet sich daher an, die Vorteile, die sich aus der wohldefinierten Beschreibung in einem mathematischen Kalkül ergeben mit denen, die aus einer graphischen Eingabe resultieren, in geeigneter Weise zu kombinieren. Ein erster Ansatz hierzu wurde bereits in [Bur88], [BBH+90] verwirklicht. Der dort beschriebene graphische Editor für Netze erzeugt als Ausgabe eine Darstellung in Form bikategorieller Ausdrücke. Über diese Schnittstelle wurde der Editor als Frontend für die weiteren Werkzeuge von CADIC benutzt. Der Nachteil dieser isolierten Lösung besteht darin, daß man sich mit dem Übergang von der graphischen zur textuellen Beschreibungsebene die oben geschilderten Probleme bei der Auswertung von berechneten Ergebnissen einhandelt.

Der in diesem Abschnitt beschriebene graphische Editor hat den Vorteil, daß er auf einer für alle Werkzeuge zentralen Datenstruktur arbeitet. Dadurch wird eine enge Bindung zwischen der graphischen Eingabe und den weiterverarbeitenden Werkzeugen möglich, so daß ein direkter Bezug zwischen berechneten Resultaten und dem Entwurf gewährleistet wird. Die dem Editor zugrundeliegende Spezifikationsebene unterstützt dabei sämtliche in den Abschnitten 1.2.1 und 1.2.2 vorgestellten Aspekte. Ihre Syntax ist aufgrund der modularen Implementierung leicht um neue Konstrukte erweiterbar. Voraussetzung dafür ist allerdings, daß die Eigenschaft der Sprachgrammatik als LR(1)-Grammatik erhalten bleibt.

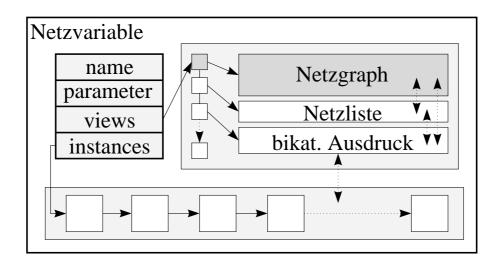

Wir zeigen nun, wie ein Gleichungssystem über Netzvariablen mit Hilfe des graphischen Editors eingegeben werden kann. Jede Gleichung soll dabei durch eine graphische Eingabe repräsentiert werden. Wir werden deshalb stets einfache Gleichungssysteme gemäß Definition 1.11 betrachten, d.h. solche Systeme, in denen stets eine Netzvariable auf der linken Seite der Gleichung durch eine graphische Beschreibung auf der rechten Seite definiert wird. Die graphische Beschreibungsebene eines solchen Gleichungssystems soll dabei sämtliche in den Abschnitten 1.2.1 und 1.2.2 gezeigten Eigenschaften unterstützen. Es soll also auch die Eingabe rekursiver und damit parametrisierter Gleichungssysteme ermöglicht werden. Insbesondere erhalten wir durch die Verwendung von Leitungsvariablen eine Beschreibungsmethode, die eine wiederverwendbare Spezifikation von Strukturen ermöglicht. Eine Beschreibungsmethode dieser Art findet sich augenblicklich in keiner bekannten Beschreibungssprache, weder auf textueller noch auf graphischer Basis.

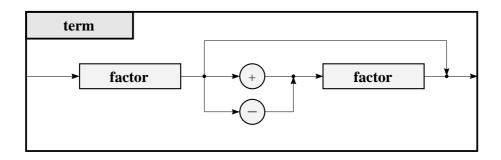

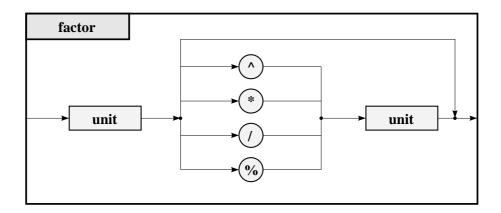

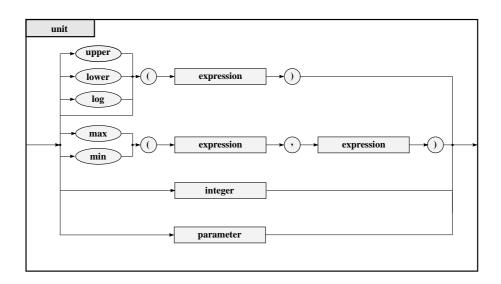

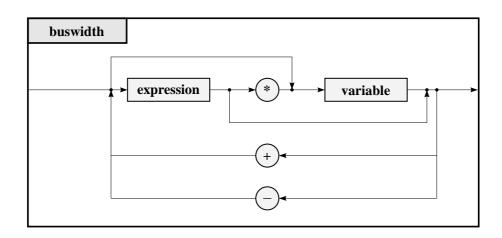

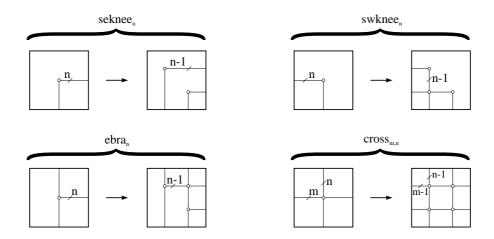

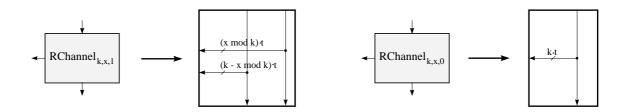

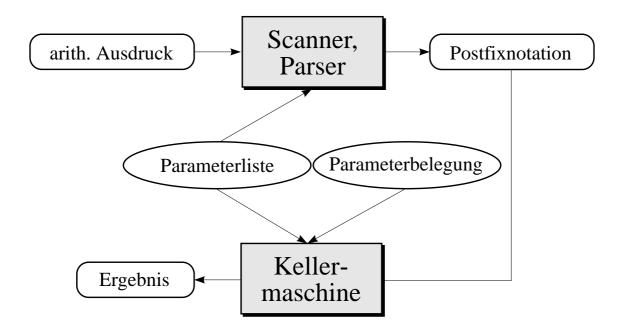

#### 1.3.1 Syntaktische Strukturen

Zur Eingabe parametrisierter Netzgleichungen benötigen wir Konstrukte, die von den formalen Netzparametern abhängen. Es handelt sich dabei um Ausdrücke zur Beschreibung von Subschaltungen, Leitungsbreiten und Randbeschreibungen. Diese syntaktischen Strukturen sind durch die erlaubten arithmetischen Operationen der Beschreibungssprache definiert. Sie werden während der graphischen Eingabe eines Netzes von einem Scanner/Parser-Modul auf syntaktische Korrektheit überprüft. Ein wichtiger Aspekt hierbei ist, daß es durch die modulare Implementierung des Gesamtsystems sehr einfach möglich ist, die Menge der erlaubten Konstrukte zu erweitern. Dies geschieht durch Erweiterung der zugrundeliegenden Grammatik, aus der Scanner und Parser automatisch generiert werden. Zu berücksichtigen sind dabei die durch den Generator bedingten Einschränkungen in Bezug auf die Grammatik ([LMB92]).

Zur Beschreibung der syntaktischen Struktur von Eingabe-Konstrukten verwenden wir Syntaxdiagramme, wie sie aus der Beschreibung von Programmiersprachen bekannt sind. Elementare Konstrukte wie *identifier* und *integer* sollen dabei ihre allgemein übliche Bedeutung besitzen.

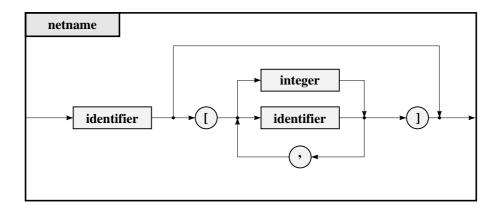

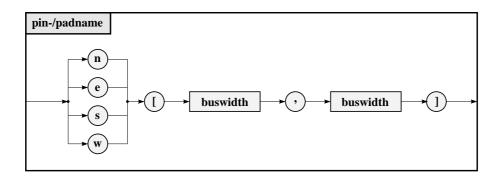

#### Linke Gleichungsseite

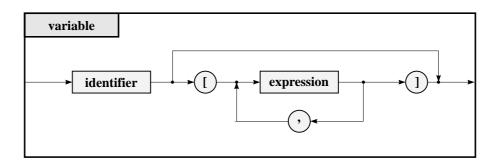

Bei der graphischen Beschreibung von Netzgleichungen entspricht der Name des einzugebenden Netzes der zu definierenden Netzvariablen  $X[p_1,\ldots,p_n]$ . Auf der linken Gleichungsseite darf nur eine einfache Netzvariable stehen, d.h. die Parameter sind entweder vom Typ identifier oder integer. Es sind hier keine komplexen Ausdrücke über den Schaltungsparametern zugelassen. Da sowohl fest belegte als auch freie Parameter auftreten dürfen, können wir damit allgemeine Gleichungen und Schlußregeln eingeben, wie dies in Definition 1.12 gefordert wurde. Das Syntaxdiagramm für die Beschreibung einer Netzvariablen ist in Abbildung 1.9 dargestellt.

Abbildung 1.9: Syntax-Diagramm für linke Gleichungsseiten

Wir bezeichnen  $X[p_1,\ldots,p_n]$  als Netzvariable der Dimension  $n,n\geq 0$  mit den Parametern  $p_1,\ldots,p_n$ . Da wir auch den Fall n=0 zulassen, ist die Parameterliste einer Netzvariablen optional. In Abbildung 1.9 ist dies ebenfalls berücksichtigt. Gemäß Definition 1.11 fassen wir die freien Parameter einer Netzvariablen  $X[p_1,\ldots,p_n]$ , d.h. die Menge der Parameter vom Typ identifier, in der Menge  $P_X$  zusammen, da wir diese bei der Beschreibung von Elementen auf der rechten Gleichungsseite verwenden dürfen.

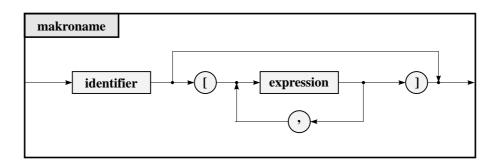

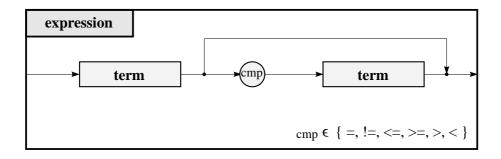

#### Rechte Gleichungsseite

Die rechte Seite einer Netzgleichung  $X[p_1,\ldots,p_n]=e(P_X)$  wird durch einen Ausdruck über  $P_X$  beschrieben. Für die graphische Eingabe von  $X[p_1,\ldots,p_n]$  bedeutet dies, daß die benutzten Subschaltungen und Leitungen von den Parametern des Netzes abhängen dürfen. Diese Abhängigkeiten werden durch arithmetische Ausdrücke über den Netzparametern beschrieben. Der Name eines verwendeten Bausteins kann also von der Form  $B[a_1,\ldots,a_m]$  sein, wobei alle  $a_1,\ldots a_m,\ m\geq 0$ , arithmetische Ausdrücke über der Menge  $P_X$  der Netzparameter sind. Wir betrachten zunächst das in Abbildung 1.10 dargestellte Syntaxdiagramm für Bausteinnamen. Auch hier ist die Parameterliste optional, d.h. neben variablen Makrozellen können auch solche verwendet werden, die nicht von den Netzparametern abhängen. Dies ist insbesondere dann der Fall, wenn Bausteine aus der Grundzellenbibliothek verwendet werden.

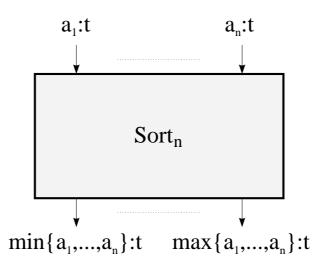

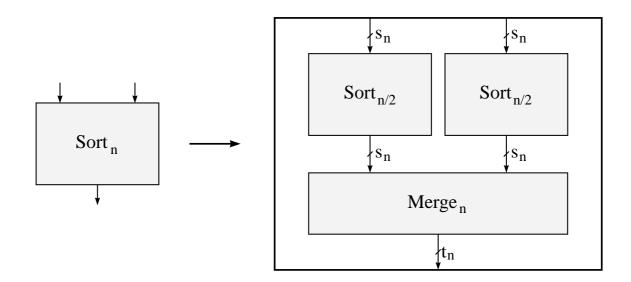

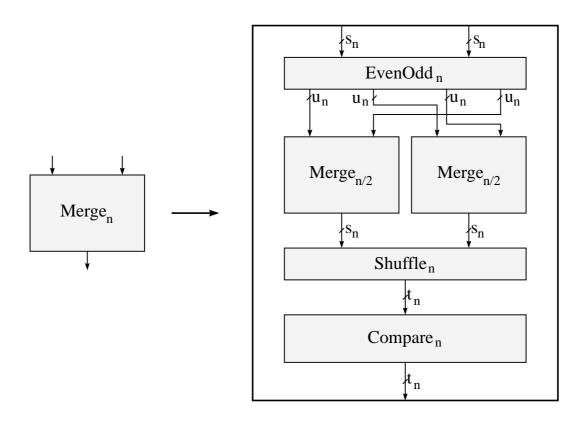

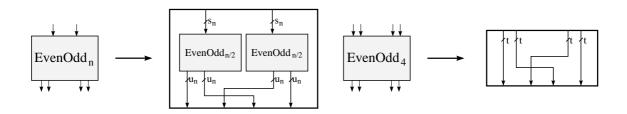

Abbildung 1.10: Syntax-Diagramm für Bausteinnamen