# New Driving Schemes of Cholesteric Liquid Crystal Display for High Speed and Uniform Gray-Scale Performance

## **Dissertation**

zur Erlangung des Grades

des Doktors der Ingenieurwissenschaften

der Naturwissenschaftlich-Technischen Fakultät II

-Physik und Mechatronik-

der Universität des Saarlandes

von

**Qiang Fu**

Saarbrücken

2012

Tag des Kolloquiums: 16.04.2013

Dekanin/Dekan: Univ.-Prof. Dr. Christian Wagner

Mitglieder des Prüfungsausschusses :

Prof. Dr. -Ing. Matthias Nienhaus

Prof. Dr. –Ing. Chihao Xu

Prof. Dr. –Ing. Michael M $\ddot{\text{o}}\text{ller}$

Dr. -Ing. Ortwin Farle

## **Eidesstattliche Versicherung**

Hiermit versichere ich an Eides statt, dass ich die vorliegende Arbeit selbstständig und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernomenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in einem Verfahren zur Erlangung eines akademischen Grades vorgelegt.

## Acknowledgment

The research work for completing my Ph.D. in University of Saarland is a challenging thing for me. It's not possible to successfully finish it without the help from others. That's why I want to sincerely thank those people who give me help in my research life in the Institute of Microelectronics of Saarland University.

First I would like to give my sincere gratitude to my supervisor, professor. Dr.-Ing Chihao Xu, who is also the head of our institute, for his long-term and serious direction in my work. During my four year's research work, professor Xu always could give me constructive suggestion and commentary when I met problems and he also gives me so much help in my daily life in Germany as a foreign student.

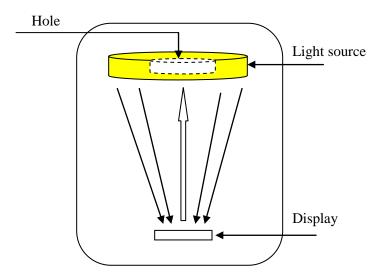

I also would like to thank former collage Christoph Drews for his help in the design and manufacture of the reflectance test set which is quite useful in our gray scale's test.

The sincere thank also should give to the former collage Hans Morgenstern for his help in the layout of the driver board for my research work. His experience and help made the experiment much easier and quicker.

As a Chinese living in Germany, I have further problems besides the research work. These problems could be solved with the help of the secretary of the institute Mrs. Therese Muse and Mrs. Brigitte Vogel. I would like to sincerely thank them here for their warmhearted help in all of my life areas. I also would like to thank other colleagues, Tobias Jung, Daniel Schaefer, Yassen Dobrev und Michael Krause for the good atmosphere and team work.

I also want to thank the German company AEG MIS for providing us the cholesteric LCD panel for the experiments and thank Dr. Supritz for the constructive talk when we visiting the company.

I also wish to express my sincere thank to Professor Karlheinz Blankenbach from Pforzheim University for his help in the reflectance's measurement.

Last but not least, I want to give my earnest thank to my wife Wan Xi as well as my parents for their long-term support and encouragement.

## Zusammenfassung

Für eine lange Zeit war das Fehlen eines effektiven Treiberschemas ein Haupthindernis für die Anwendung der Cholesterischen LCDs. Viele Treiberschemata wurden in den letzten Jahren wie das herkömmliche statische Treiberschema sowie mehrere schnelle Dynamische Treiberschemata (DDS) entworfen. Diese Treiberschemata, die in Kapitel 3 eingeführt werden, zeichnen sich entweder durch gute Bildqualität oder durch schnelle Ansteuergeschwindigkeit aus. Als Verbesserung führen wir ein verbessertes dynamisches Treiberschemata (genannt Enhanced Dynamic Driving Scheme) ein, das ermöglicht, das Ch-LCD nicht nur in den Ein- oder Aus-Zustand, sondern auch in mehrere verschiedene Graustufen anzusteuern. Im Enhanced Dynamic Driving Scheme sind die Selection und Hold Wellenformen neu gestaltet, so dass Pixels auf bestimmte Reflexionen angesteuert werden können, während die nicht selektierten Pixels untangiert bleiben. Im Gegensatz zum  $U/\sqrt{\frac{3}{2}}$  DDS Verfahren, das fünf Spannungen verwendet, werden nur drei Spannungen im neuen Enhanced Dynamic Driving Scheme ben ötigt. Die höchste Treiber-Spannung wurde um 12%, verglichen mit dem  $U/\sqrt{2}$  DDS, ebenfalls reduziert. Die Ansteuergeschwindigkeit beträgt 1.2 ms / Zeile, die höher als viele dynamische Treiberschemata ist. Das Enhanced Dynamic Driving Scheme zeigt also in fast jedem Aspekt eine bessere Leistung und bessere Parameter.

Graustufen können im bistabilen Ch-LCD realisiert werden und sind eigentlich ein Mischzustand des reflektierenden planaren Zustands (planar state) und dem streuenden fokal-konischen Zustands (focal conic state). Im Enhanced Dynamic Driving Scheme, das in Kapitel 3 eingeführt wird, werden Graustufen in der Ch-LCD mit dem effektiven Wert (root of mean square RMS) der angelegten Spannung erzeugt, anstatt die Höhe der Spannung zu modulieren. Somit können Graustufen von verschiedenen RMS-Spannungen durch Verschiebung des Tastverhältnisses der ansteuernden Wellenformen erreicht werden. Die Anzahl der Spannungsquellen könnte verringert werden, so dass die Komplexit ät und die Kosten des Treiber deutlich reduziert werden können.

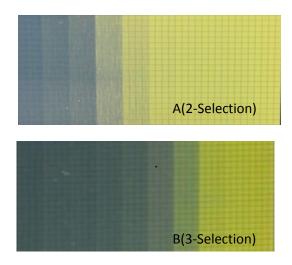

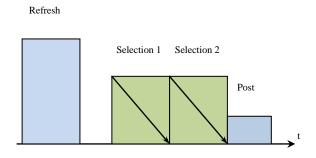

Aufgrund der intrinsischen Eigenschaften des Ch-LCD, dass der Zustandsübergang in DDS ziemlich steil ist, ist die Anzahl der Graustufen, die mit dieser Methode erzeugt wird, eher bescheiden. Um die Anzahl der Graustufen durch das Enhanced Dynamic Driving Scheme zu erhöhen, haben wir eine neue Methode, genannt Multi-Selection-Method (MSM), vorgeschlagen. Diese Methode scannt das Display zwei oder mehrere Male während eines Ansteuervorgangs. Somit kann eine Graustufe in zwei oder mehr Stufen verfeinert werden, so dass die Anzahl der Graustufen ohne erhöhte Hardwarekosten mindestens verdoppelt werden kann. Die Graustufen in dem dunklen Bereich sind auch erweitert, das die Anforderungen der nichtlinearen Gamma-Korrektur trifft. Während des Experiments wurden das Two- und das Three-Selection-Verfahren

für die Ansteuerung der Graustufen durchgeführt. Im Anbetracht der Tatsache, dass das Threeoder gar das Four-Selection-Verfahren mehr Zeit verbraucht und dafür die Anzahl der Graustufen im Vergleich mit dem Two-Selection-Verfahren nur ein wenig erhöht, wird das Two-Selection-Verfahren bevorzugt.

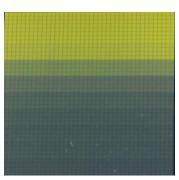

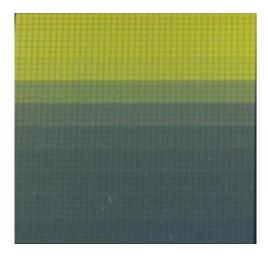

In Ansteuerung der Graustufen auf Ch-LCD ist die Gleichmäßigkeit der erzeugten Graustufen ein weiteres zu betrachtendes Thema. Leider ist die Gleichmäßigkeit der Graustufen, die durch ein DDS erzeugt werden, nicht zufriedenstellend, egal ob im One- oder Multi-Selektion-Verfahren. Um die Gleichmäßigkeit der Graustufen in einer hohen Ansteuergeschwindigkeit zu verbessern, schlagen wir ein schnelles statisches Treiberschema, genannt Fast Static Driving Scheme, vor, das auf dem Übergang von einem stabilen Zustand in einen anderen stabilen Zustand, aber nicht über einen meta-stabilen Zustand, basiert ist. Die erzeugten Graustufen zeigen gute Gleichmäßigkeit im Vergleich mit den von einem DDS erzeugten Graustufen. Weil der Übergang der Zustände an der linken Seite der R-V Kurve (Reflection-Voltage) geschieht, die sanfter als die rechte Seite verläuft, wird die Anzahl der Graustufen auch noch erhäht. Jedoch ist das Fast Static Driving Scheme etwa halb so schnell wie das Enhanced Dynamic Driving Scheme.

Ein weiteres Verfahren, um die Ansteuergeschwindigkeit zu erhöhen, ist das Multiline Addressing Verfahren, das für die PM-LCD und PM-OLED erprobt ist. Wellenformen für die zweizeilige Adressierung wurden für das Enhanced Dynamic Driving Scheme entworfen, um die vier Kombinationen der angesteuerten Zuständen zu erzielen. In Experimenten und Tests auf Ch-LCD Panel wurde ein gutes Ergebnis erzielt. Das Multiline Addressing Verfahren für das Ch-LCD reduziert die Ansteuerzeit um fast 50%, was für große Displays mit hoher Auflösung besonders bedeutsam ist.

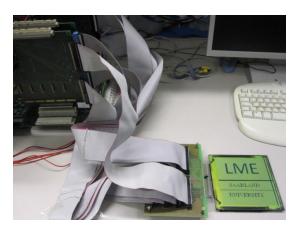

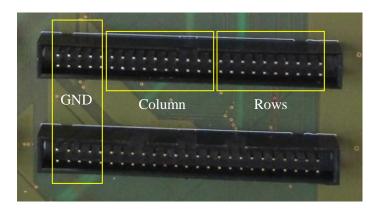

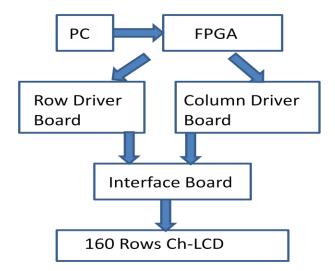

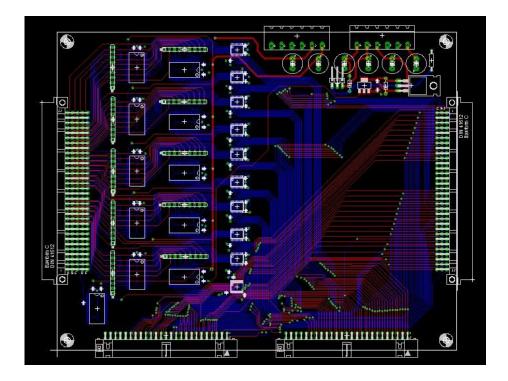

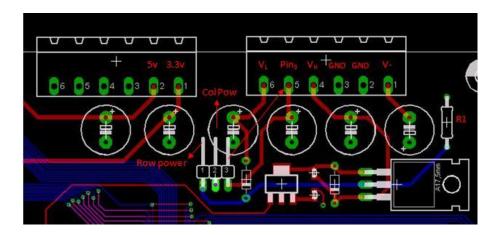

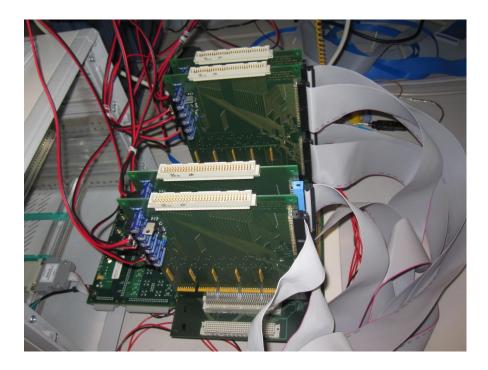

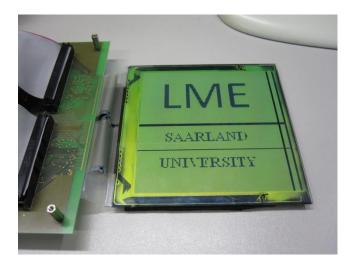

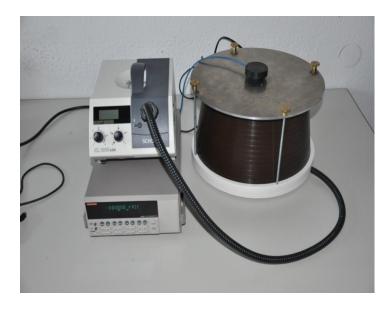

Um die Treiberschemata in dieser Arbeit zu validieren, wurden vier diskrete Treiber-Platinen entworfen und hergestellt. Alle vorgeschlagenen Treiberschemata wurden auf einem  $160 \times 160$  Ch-LCD (bereitgestellt von AEG MIS) durch die Treiber-Platinen ausgeführt. Ein Vertex 5 FPGA wurde als Signalgeber verwendet. Experimentale Ergebnisse zeigten eine sehr gute Übereinstimmung mit den Designzielen. Dies beweist, dass die neuen Treiberschemata in dieser Arbeit richtig und wirkungsvoll sind.

Durch die Synergie mit der etablierten LCD Technologie und anderen technischen Vorzügen ist das cholesterische LCD ein vielversprechender Kandidat für die nächste Generation der farbigen E-Paper Displays. Die hähere Ansteuergeschwindigkeit, hähere Graustufen-Auflösung, bessere Gleichmäßigkeit und einfache Treiber-Architektur kann ein wenig die Wettbewerbsfähigkeit der Ch-LCD stärken. In Kombination mit möglichen Verbesserungen in anderen Eigenschaften wie Reflexion und Farbwiedergabe etc., kann das Ch-LCD eine weit verbreitete E-Paper-Technologie werden.

#### **Abstract**

Electronic paper is a kind of display which is aimed to mimic the real paper. For the E-paper display, very low power consumption, high reflectance which is close to the real paper, fast driving speed and flexibility are expected. In recent years, many technologies such as Electrophoretic display, Electrowetting display and Cholesteric LCD etc. with different characteristics have been developed to meet the tremendous market demand.

Among these technologies, Cholesteric LCD (Ch-LCD) is expected to be a promising candidate in the next generation's e-paper displays. The Ch-LCD has not only the advantages such as low power consumption, good sunlight readability and high contrast ratio and resolution but also features the potential capability of color e-paper display without color filters. It is also compatible with the plastic substrate making the flexibility easy to be achieved.

For quite a long time, lacking of a fast and effective driving scheme for driving of the Ch-LCD is a primary limitation for the enhancement of the display's performance. Conventional static driving scheme could drive the Ch-LCD at only about 50 ms / line. This slow refresh speed makes the Ch-LCD unpractical especially when the resolution gets higher. Later, fast driving scheme such as dynamic driving scheme (DDS) making use of the fast transition from the meta-stable homeotropic state to the transient planer state was proposed. The DDS could increase the driving speed to about 2 ms / line so that the practicability is largely extended. However, despite the fact that several improved driving scheme based on the dynamic driving scheme have been published one after another, the driving speed and complexity are still not well balanced. Besides, how to generate the distinct and uniformed gray scale in a fast driving speed has not been solved yet.

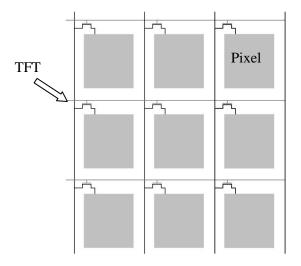

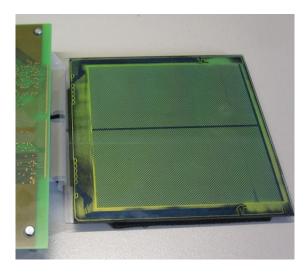

In this thesis an enhanced dynamic driving scheme with the ability of driving the Ch-LCD not only into the on-off state but also into several distinct gray scales at about 1.2 ms / line has been proposed. In this driving scheme, the waveform patterns are newly designed to ensure that pixels could be driven to certain reflectance while the unselected pixels remain unaffected. Gray scales are created by controlling the root of mean square (RMS) value of the applied voltages. There are only three voltage sources needed in the whole driving scheme which is fewer than that of other DDS schemes. The highest voltage used in the enhanced DDS was reduced by 12% comparing with the U /  $\sqrt{2}$  DDS. The enhanced DDS has been executed on a 160×160 Ch-LCD provided by AEG MIS. Binary image with good quality has been achieved.

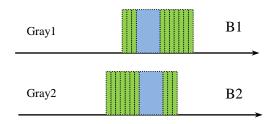

In the enhanced DDS proposed, the number of gray scale is limited. This is due to the steep transition at the right side of the R-V curve narrowing the space of gray scale's generation. A method called as multi-selection method (MSM) was proposed for the first time to enlarge the gray scale number. The MSM is based on two or more selections in the whole driving scheme. Thus,

the gray scales will be created in two or more steps. This method could effectively double the gray scale number and the gray scales in the dark side were extended which is consistent with the non-linear requirement of the gamma correction.

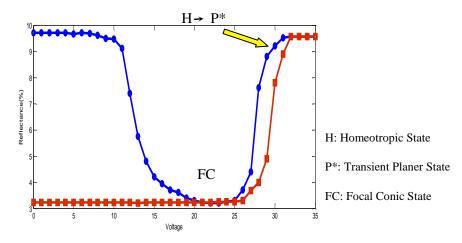

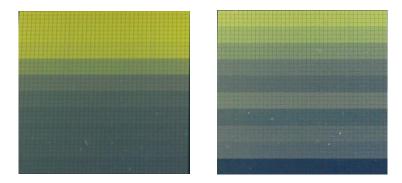

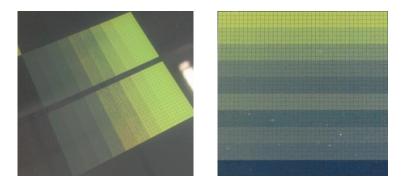

By testing this enhanced DDS, we also found that the generated gray scales are not so satisfactory in terms of uniformity. This is caused by the state transition mechanism in DDS that the stable state is achieved through the meta-stable homeotropic state and transient planer state. In order to achieve uniform gray scales we proposed a new driving scheme named novel fast static driving scheme. Gray scales in this new driving scheme are created from the stable planer state instead of the meta-stable states as in DDS. The transition happens at the smooth left side of the R-V curve. The uniformity of the gray scales is much better compared with those created by the DDS. Driving speed as fast as 2 ms / line was also achieved which is comparable with most of the DDS. Gray scale number was increased at the same time due to the smoother transition of the left side R-V curve.

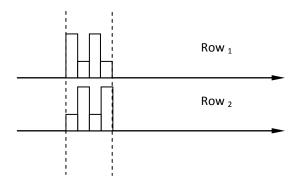

Similar to the multiline driving method used in the PM-LCD and PM-OLED, we also proposed a multiline driving scheme incorporated in the enhanced DDS. Newly designed waveform pattern allows two Ch-LCD lines to be selected at the same time, which will further increase the driving speed.

Experiments were executed to validate the new driving schemes. A discrete driver system including high-voltage and analog circuit board as well as a Vertex 5 FPGA for patter generation has been designed and built. The 160×160 Ch-LCD panel was used in experiments. For the contrast ratio and gray scale's measurement, a reflectance measurement set was developed and made. Visual results were the base for the various developments and improvements in this thesis. The analysis showed that the visual results are consistent with the expectation. The two new driving schemes allow relatively high refresh time, while reasonable gray scales are achieved. Furthermore, the novel fast static driving scheme produces uniform gray scales.

## **Table of Contents**

| 1.  | Electroni | c Paper Display Technology                     | 1  |

|-----|-----------|------------------------------------------------|----|

| 1.1 | Introdu   | action                                         | 1  |

| 1.2 | Electro   | phoretic Display                               | 2  |

|     | 1.2.1     | E-Ink Technology                               | 2  |

|     | 1.2.2     | QR-LPD (Quick Response Liquid Powder Display)  | 3  |

| 1.3 | Electro   | owetting Display                               | 4  |

| 1.4 | Choles    | teric Liquid Crystal Display                   | 6  |

| 1.5 | Other l   | E-paper Technologies                           | 8  |

|     | 1.5.1     | Electrofluidic Display                         | 8  |

|     | 1.5.2     | Electrochromic Display                         | 9  |

|     | 1.5.3     | IMOD (Interferometric Modulator Display)       | 10 |

| 1.6 | Conclu    | ision                                          | 11 |

| 2.  | Physical  | and Optical Characteristics of Cholesteric LCD | 15 |

| 2.1 | Introdu   | oction                                         | 15 |

| 2.2 | Molecu    | ale Structure of the Ch-LC                     | 16 |

| 2.3 | Stable    | States of the Ch-LC                            | 16 |

| 2.4 | Meta-s    | table States of Ch-LC                          | 18 |

| 2.5 | Materi    | al and Stability Mechanism                     | 20 |

| 2.6 | Optica    | l Properties                                   | 21 |

| 2.7 | Conclu    | ision                                          | 23 |

| 3.  | Driving S | Schemes of the Cholesteric LCD                 | 25 |

| 3 1 | Introdu   | action                                         | 25 |

| 3.2 | State 7  | Γransition of the Ch-LCD                         | 25 |

|-----|----------|--------------------------------------------------|----|

| 3.3 | Conve    | entional Driving Scheme                          | 27 |

| 3.4 | Dynan    | mic Driving Scheme (DDS)                         | 28 |

|     | 3.4.1    | DDS U/ $\sqrt{2}$                                | 31 |

|     | 3.4.2    | DDS U/ $\sqrt{3/2}$                              | 33 |

|     | 3.4.3    | Fast Dynamic Driving Scheme                      | 36 |

| 3.5 | Enhan    | ced DDS with Gray Scale's Capability             | 37 |

| 3.6 | Concl    | usion                                            | 45 |

| 4   | Gray Sca | ale Driving in Ch-LCD                            | 47 |

| 4.1 | Introd   | uction                                           | 47 |

| 4.2 | Gray S   | Scale Driving Methods                            | 48 |

|     | 4.2.1    | Pulse Height Modulation                          | 48 |

|     | 4.2.2    | RMS Control Method                               | 49 |

| 4.3 | Gray S   | Scale's Generation in the Enhanced DDS           | 49 |

|     | 4.3.1    | Gray Scale's Generation by RMS Control Method    | 49 |

|     | 4.3.2    | RMS Control in the Selection Stage               | 50 |

|     | 4.3.3    | Constant RMS Value in the Holding Stage          | 52 |

| 4.4 | Multi    | Selection Method for More Gray Scales            | 52 |

|     | 4.4.1    | Two Selections Method                            | 52 |

|     | 4.4.4    | Three Selections and More                        | 62 |

| 4.5 | Concl    | usion                                            | 63 |

| 5   | Novel Fa | ast Static Driving Scheme for Uniform Gray Scale | 65 |

| 5.1 | Introd   | uction                                           | 65 |

| 5.2 | Drivin   | g Time of Each Driving Stage                     | 67 |

| 5.3 | Waveform Patterns of All Driving Stages                  | 69  |

|-----|----------------------------------------------------------|-----|

| 5.4 | Voltage Values of the Driving Scheme                     | 70  |

| 5.5 | Gray scale Control in the Fast Static Driving Scheme     | 72  |

| 5.6 | Multi-Selection Method in the Fast Static Driving Scheme | 73  |

| 5.7 | Conclusion                                               | 75  |

| 6   | Multiline Addressing of Ch-LCD                           | 77  |

| 6.1 | Introduction                                             | 77  |

| 6.2 | Multiline Driving of the Conventional Driving Scheme     | 80  |

| 6.3 | Multiline Driving in the Enhanced Dynamic Driving Scheme | 81  |

| 6.4 | Conclusion                                               | 84  |

| 7   | Driving Circuit Design                                   | 87  |

| 7.1 | Design Philosophy                                        | 87  |

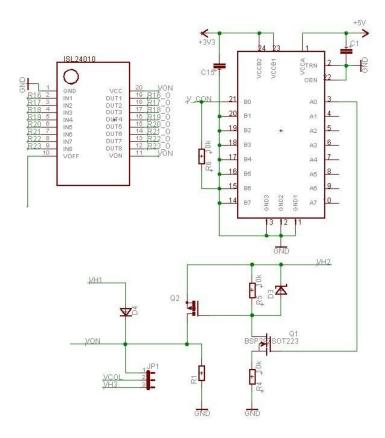

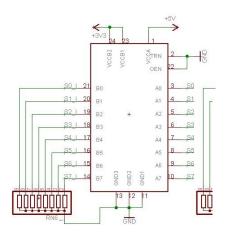

| 7.2 | Driver Circuit Design                                    | 89  |

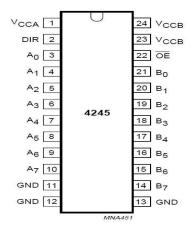

| 7.3 | Components Used In the Circuit                           | 91  |

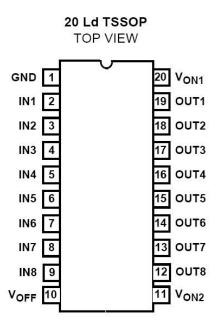

|     | 7.3.1 Transceiver IC                                     | 92  |

|     | 7.3.2 Level shifter IC                                   | 94  |

| 7.4 | Driver board                                             | 95  |

| 7.5 | Summary                                                  | 95  |

| 8   | FPGA Implementation and Measurement                      | 97  |

| 8.3 | Introduction                                             | 97  |

| 8.4 | Image Processing by MatLab                               | 97  |

| 8.5 | Verilog Coding and Results                               | 98  |

|     | 8.5.1 Two-Value Coding                                   | 98  |

|     | 8.5.2 Gray Scale Coding                                  | 99  |

| 8.6 | Reflectance Measurement                                  | 101 |

#### Table of Contents

| 8.7 | Summary    | . 103 |

|-----|------------|-------|

| 9   | Conclusion | . 105 |

| 10  | Appendix   | . 107 |

| 11  | References | . 111 |

## 1. Electronic Paper Display Technology

#### 1.1 Introduction

Electronic display is one of the most important links of input/output device for the interaction between human and computer or other machines. It has the ability to switch the electronic signals into readable information, such as character, number or image etc. After the first CRT (Cathode Ray Tube) display was made in 1922, many display technologies have been developed. Since the early 1970s LC (Liquid Crystal) display appeared, along with years of constant research and improvement, the LCD gradually replaces the CRT in the display area in the new era. Today the LCD is still the dominant display technology used in almost all application fields. Recently, a promising display called OLED (Organic Light Emitting Diode) is attracting attention. The OLED has some advantages even comparing with the current LCD in the aspects such as color gamut, wide viewing angle, high speed and power consumption [1].

Different from the displays being mentioned above, a novel display name electronic paper was first developed by Xerox's Palo Alto Research Center in United States in 1975. It uses charged polyethylene spheres suspending in oil bubbles which can be controlled by voltages. In 1996, MIT Media Lab successfully produces the first electronic paper display. In 2000, the first flexible e-paper display was officially presented by the American company E-ink and two years later the first color e-paper display was published in Tokyo [2]. From this point on, many technologies have been developed targeting on better solution.

The electronic paper display (EPD) is designed to mimic the visual effect of the character appearance of ordinary ink on a real paper. Unlike the conventional liquid crystal display, EPD is a bi-stable display in which the information can be maintained either without using electronic or magnetic field or at a negligible amount. It only consumes power if the content of the display is updated. Considering the slow progress of the battery technology, low power consumption is especially valuable for portable devices, such as electronic books or newspapers. The electronic paper display doesn't require a backlight due to its capability of controllable reflection of the ambient light. It is also convenient to be made on a plastic or some kind of organic substrate which will make the display flexible.

Once the image on the electronic paper has been set, it remains for several weeks or even months after the power has been removed. This feature makes it to an ideal candidate for display applications which do not need to be refreshed frequently, for example, electronic books or billboard. Because of the extremely low power consumption, in some outdoor applications, the power of the display could be provided by the solar cell and the information as well as the instruction could be transmitted by remote site which will make it location free [3]. However, current electronic paper displays have disadvantages such as color reproduction, refresh speed, etc.

These shortcomings demand further improvements of the display technology and give topics to be researched [4].

Many technologies of electronic paper display have been developed to fulfill the tremendous market demand, such as electrophoretic display, electrowetting display and cholesteric display, etc. Each technology has its own advantages and disadvantages. [5] At least till now, not a single technology fulfills all of the requirements and strictly dominates the rest. Therefore in the field of electronic paper, these different technologies are actually racing versus each other. In this chapter, we will briefly introduce several mainstream electronic paper technologies.

### 1.2 Electrophoretic Display

#### 1.2.1 E-Ink Technology

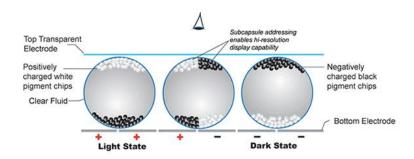

Electrophoretic is the most popular electronic paper technology today. About 90% of the commercial electronic paper devices adopt this technology. Such as Amazon's kindle e-book, Sony e-book reader and iRex reader. There are two main technologies by adopting the electrophoretic theory, which are E-ink's e-ink pearl and Bridgestone's QR-LPD. The basic schematic diagram which illustrates the working principle of the E-ink technology is shown in Figure 1-1.

Fig. 1-1 Schematic diagram of the E-ink technology for the E-paper reader (Source: E ink Corp).

The E-ink display was proposed by the MIT Media Lab and commercialized by the company named E-ink which was spun off from MIT. Unlike the liquid crystal display, the e-ink display is made up of many small capsules, each with the diameter of around 0.04mm. The charged black and white titanium dioxide particles which are nearly one micrometer in diameter are suspended in oil and can be controlled by the applied voltage. Figure 1-1 shows the schematic diagram of how the e-ink display works. As shown in Figure 1-1, the black and white color particles are suspended in oil. By applying voltage to the transparent electrode, the charged black and white particles can be moved to the top of the capsule either completely or partly and display so the black, white or gray. A similar technology was also developed by the company Sipix by using a bigger micro-cup at a

diameter of 0.15mm.

The E-ink display could mimic the real paper vividly among today's e-paper technologies. It also features such as low production cost and high reflectance. However, the refresh speed of e-ink is low. Usually it takes 0.5 s to 1 s to refresh. In the new generation of the e-ink display, active matrix and color filters have been adopted to refresh the display at a higher speed. Video content can also be displayed fluently and consequently ends up with high power consumption. [6]

Fig. 1-2 Monochromatic and color e ink reader

Figure 1-2 shows the monochromatic E-book produced by Amazon and the color E-book by E-Ink. Both use the E-Ink's technology.

#### 1.2.2 QR-LPD (Quick Response Liquid Powder Display)

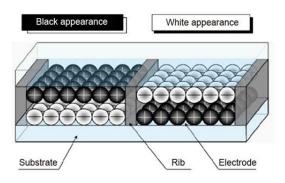

Another approach of the electrophoretic display is the QR-LPD (Quick Response Liquid Powder Display) developed by Bridgestone and Delta. Instead of moving particles in oil as achieved by E-ink, in the QR-LPD, charged particles are moved in the air. Thus the response time will be significantly shortened comparing with the E-Ink, normally a switching from black to write takes only 0.2 milliseconds. But the QR-LPD demands higher voltages to drive the particles so that the power consumption is higher than the e ink display. Passive matrix driving is feasible in the commercial application due to the fast switching speed, which cuts production cost. Besides, since the particles are moving in the air, the QR-LPD could be used in the cold outdoor environment. Figure 1-3 shows the particle structure of the QR-LPD pixel in two states.

Fig. 1-3 Structure of the QR-LPD

The color QR-LPD could be made by using different powders to reflect light. Such technology was used in Bridgestone's Aerobee display. The QR-LPD could achieve high driving speed comparing with other electrophoretic displays which was previously supposed to be the most promising e-paper candidate. However, shortcomings such as high production cost etc. have forced Bridgestone to stop the research and development of this technology.

Figure 1-4 below is a picture showing the color QR-LPD made by Delta. Good viewing angle and color reproduction have been achieved as we can see in this figure.

Fig. 1-4 Delta Color e-reader using Bridgestone's QR-LPD

## 1.3 Electrowetting Display

As a subject of the Nature in 2003, Philips proposed a video speed electronic paper display named electrowetting display (EWD). The EWD could be operated in several modes including reflective, transmissive and transflective as well as enabling the color video with a response time 70 times than the current reflective display making it a high potential candidate for the future's color

electronic paper. It also allows applications of large scale displays such as TV based on the conventional manufacturing processes.

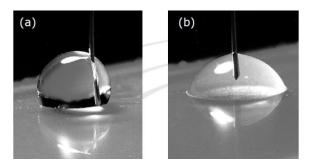

Fig. 1-5 Cross-section of the EWD

Figure 1-5 is an example to show the liquid shaped by the electric field. The switching between the two shapes could be very fast leading to fast driving speed. The Electrowetting is based on the microfluidic phenomena. It involves modifying the surface tension of liquids on a solid surface using a voltage. By applying a voltage, the wetting properties of a hydrophobis surface can be modified and the surface becomes increasingly hydrophilic. [7]

With Electrowetting displays, surface tension of colored oil is used for image display. Applied electric field could force the oil to disperse leading to a color pixel. On the other side, the charged oil could also contract as a transparent pixel. [7]

Fig. 1-6 AM-EWD made by Liquivista

Figure 1-6 is the example to show the color active matrix electrowetting display made by Liquivista. It could be observed that the resolution is quite low in the demo display. This kind of technology is still under progress now. No commercial product is available yet. [7]

## 1.4 Cholesteric Liquid Crystal Display

The cholesteric liquid crystal display is one of the promising e-paper technologies developed by Fujistu. Since it is one of the liquid crystal displays, it presents no obstacle to achieve the high resolution by using the mature LCD manufacturing process. Recently, the so called R2R (Roll to Roll) process has been introduced in the production of the cholesteric LCD to cut the cost. [8] This display consumes absolutely no power at the stable state and the image created on it could last for several months. This characteristic makes it a promising candidate in the applications such as electronic book, e-tag and electronic billboard etc. The cholesteric LCD also features good sun light readability as well as high contrast ratio. Besides, one of the biggest advantages of this display is that the cholesteric material could achieve different colors by adding certain dopant. Therefore the color display could be easily made without any color filter making it competitive in next generation's color e-papers. It also could be made in the soft plastic substrate making it flexible. Figure 1-7 shows a flexible cholesteric LCD made by ITRI<sup>1</sup>.

Fig. 1-7 Flexible Ch-LCD made by ITRI

As Figure 1-7 may indicate, the cholesteric LCD could be manufactured at large scale by using the economic R2R process. This also makes the cholesteric LCD advantageous in the application where large size panel is needed, for instance, outdoor poster. [9]

In the electronic book market, Fujistu is the leading company in developing the choltesteric LCD readers. Figure 1-8 shows the newest color cholesteric e-book published by Fujistu.

-

<sup>&</sup>lt;sup>1</sup> Flexible Ch-LCD made by ITRI using R2R process

Fig. 1-8 Fujitsu new FLEpia Ch-LCD color e book (8 inch, 4096 colors)

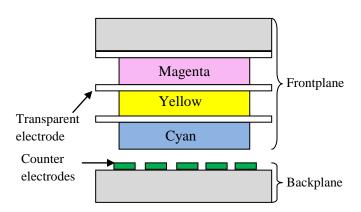

The color Ch-LCD E-Book as shown in Figure 1-8<sup>2</sup> has an 8 inch display with 4096 colors. In 2011 it was presented as the new generation FLEpia cholesteric LCD e-book featuring high brightness and rich colors. The FLEpia is made by stacking three cholesteric layers together to display color. The ambient light will be reflected in every layer to achieve three color primaries. As a counterpart, the IRTI from Taiwan also develops color cholesteric display with just one layer. The R, G and B sub-pixels are put in one and the same layer as the pixels arranged in the OLED. The color sub-pixels are made in one pixel on the plastic substrate.

Fig. 1-9 10.4 inch QVGA single layer color Ch-LCD by ITRI

Figure 1-9 shows the single layer color Ch-LCD made by IRTI<sup>3</sup>. The single layer color Ch-LCD

<sup>2</sup> Ch-LCD E-book made by Fujistu. The picture could be found at:

http://www.slashgear.com/slashgear-morning-wrap-up-july-12-2011-12164585.

Color Ch-LCD maded by ITRI; Taiwan. It was illustrated on the web page: http://www.itri.org.tw/eng/econtent/research/research03\_02.aspx?sid=23

could be made using the economical R2R process for reducing the production cost. In addition, one layer color Ch-LCD doesn't have the optical interference problem which exists in the three layer's color Ch-LCD. [10]

The cholesteric LCD is a reflective display with bi-stability. There is no need for color filter and backlight. Due to its favorable features, cholesteric LCD is expected to be a promising candidate for the next generation of e-paper application. Despite the numerous advantages, it also has its drawbacks. The contrast ratio of this kind of display should be improved. Besides, how to create enough number of gray scales with good uniformity in a fast driving scheme still remains a challenging topic. The cholesteric material is sensitive to the temperature. So in the real operation, in particular the outdoor's application, the temperature compensation circuits are usually needed.

## 1.5 Other E-paper Technologies

#### 1.5.1 Electrofluidic Display

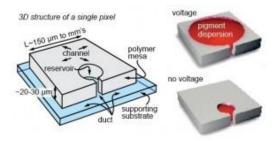

Similar to the electrowetting display, the pigment colorant which used for the printing industry were put behind the pixel surface in the electrofluidic display. Inside the display pixel, a tiny reservoir takes around 5% to 10% area of the pixel is made. The applied electric field could force the liquid into the reservoir leading to a transparent pixel.

Fig. 1-10 Pixel structure of the electrofluidic display

Figure 1-10 shows the pixel structure of the electrofluidic display. The applied voltage filed would force the color pigment out of the receiver and to disperse on the pixel's surface leading to a color pixel. After the voltage was removed, color pigment will back to the receiver as a transparent pixel.

Full color electrofluidic display technology may update the knowledge of the display industry to create reflective color. Two versions of the technology are under development. The first version provides full color operation at more than 50% brightness. The second version is projected to provide even greater color performance on-par with printed office documents. [11]

#### 1.5.2 Electrochromic Display

The chromic material was first reported in 1969. Since then, many chromic materials have been reported which have the ability to change their color reversibly when they are applied by different voltages. Figure 1-11 shows a sample of electrochromic display made by Ricoh.

Fig. 1-11 Electrochromic display (LTPS TFT 240\*320)

The technology to make a working electrochromic cell is much analogous to the technology used in LCD displays. One way to make a working cell is by placing the electrochromic material between two transparent electrodes (preferentially Indium Tin Oxide, better known as ITO). The color of the EC-material is a result of changing the potential of the cell by charging the electrodes. Some recent researches show that some of the chromic materials could switch between several colors depending on the different external voltages and it is also possible to achieve the basic color in one pixel. [12]

Fig. 1-12 3 Layers structure of the electrochromic device

The electrochromic display has numerous merits. First of all is the low power consumption. Similar

to many other the e-paper technology, the electrochromic display consumes power only when the content is refreshed. In the past, the driving of the display was troubled by the slow driving speed of switching the pixel from transparent state. In the new generation's EC display, this has been solved by adding porous electrodes. Typical switching times are now within the range of 200 milliseconds. The color display is easy to make without color filters. As shown in Figure 1-12, a molecular dye has been developed which can display red, green or blue, depending upon the applied voltage. This implies that no color filter usage is necessary, which diminish the brightness of the display. As to the mass production, the EC display also has a set of benefits. Recent studies show that existing LCD-manufacturers could easily transform their assembling machines to produce EC displays.

#### 1.5.3 IMOD (Interferometric Modulator Display)

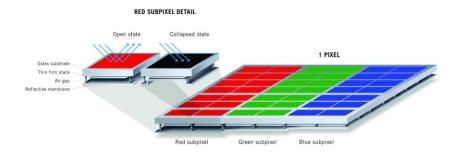

IMOD is a MEMS (Micro Electro-Mechanical Systems) based display developed by Qualcomm in USA. This display makes use of the technology named interferometric modulator to reflect specific wavelength of light to create different colors which has the same function as the color in the wing of a butterfly. The IMOD display is also bi-stable. Comparing to the LCD or OLED, the IMOD could reduce the power consumption largely, and color filter is also not needed for color display.

Fig. 1-13 Sample of IMOD pixel matrix

Figure 1-13 shows a sample of the pixel matrix of the IMOD. As shown in Figure 1-13, color pixel could be generated by different pixel's reflectance which could be achieved by varying the depth of the cavity. Black pixel could be achieved by shifting the back plane which will lead to an ultraviolent reflectance. [13]

Fig. 1-14 IMOD display by Qualcomm (5.7" XGA format (1024 x 768 pixels))

Figure 1-14 above shows the IMOD branded Mirasol made by Qualcomm. It could operate at 30 fps which allows a video speed application. In case of displaying video content, the Mirasol display consumes about 20% less power than the E-ink display. It also supports wide range of working temperatures. Because it is a MEMS based display, the temperature could vary between -30 °C and +70 °C, allowing a wide range of environment. The IMOD is still under intensive research but it is already expected to be a promising candidate in the next generation's e-paper display to compete with the E-ink technology. The production cost of this kind of display still remains high. Cutting production cost could be possible if the production could be compatible with process of the flat panel display.

However, The IMOD display currently still has deficiencies, such as small viewing angle and low color reproduction. Comparing with e-ink's technology, the viewing experience of the display is more like the LCD but not the real paper. In SID 2012, Qualcomm has shown some of devices using the Mirasol display such as e-book and smart phone with good quality by eye observation. This kind of display may have potential value in the e-paper market in the near future.

#### 1.6 Conclusion

In this chapter we introduced several main technologies of the electronic paper display. As a summary, the table below compares the advantages and challenges of these technologies as well as the R&D facilities.

|                                         |                              |                                                                                                                                     | 1                                                         |

|-----------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|                                         | R&D                          | Advantages                                                                                                                          | Challenges                                                |

| EPD (Electrophoretic) (E-Ink;QR-LPD)    | E-ink(PVI) Sipix Bridgestone | Mainstream technology in current e-book product (Commercialization) Anti-press capability                                           | Hard to make color<br>display<br>color filter needed      |

| EWP<br>(Electrowetting)                 | Liquavista(Samsung) ITRI     | Quick response good for color and video applications                                                                                | High driving voltage                                      |

| EFD<br>(Electrofluidic)                 | Gamma Dynamics               | >85% white-state reflectance<br>good visual brilliance<br>Brightness, color situation, video<br>speed                               | High power consumption                                    |

| IMOD<br>(Interferometric<br>MODulation) | Qualcomm(Mirasol)            | Fast refresh speed for video application  Low power consumption( <e-ink)< td=""><td>Small view angle Production cost</td></e-ink)<> | Small view angle Production cost                          |

| ECD<br>(Electrochromic)                 | Siemens<br>Ricoh<br>Samsung  | 70% white-state reflectance  No color filter                                                                                        | Color reproduction<br>Driving speed                       |

| Ch-LCD<br>(Cholesteric)                 | Kent Display ITRI Fujistu    | Good reflectivity  Color display without color filters  Synergy to LCD production                                                   | Temperature dependence  Low driving speed poor gray scale |

Table 1-1 Comparison of the main technologies of the electronic paper display

Electronic paper display is currently in a critical phase of its development. Many potential technologies are racing for the future's tremendous market demand. Currently the e-ink technology has achieved the leading position in the monochromatic field due to its good image quality and lower cost. When the electronic paper display comes to the color generation, e-ink's technology loses its superiority because the color filter in the electrophoretic display reduces the reflectivity which will cause the display to be dark. The IMOD display dominated by Qualcomm is good for the low power consumption and higher color reproduction. However, because Qualcomm could not manage to overcome the high production cost. The plan to commercialize this e-paper has been stopped. The Cholesteric LCD is a lower power display due to the bi-stability. The image can be maintained in the display at zero electric field for months. The color display is easy to make in the Ch-LCD by using either three layer stack method or one layer method. It is easy to compatible with the R2R process which will largely reduce the production cost and the scale will be unbounded.

As a summary, which technology would be the strongest contender remains unclear. It would be contingent upon which technology could effectively overcome its deficiencies and could be produced at an acceptable cost. In my opinion, the cholesteric LCD (Ch-LCD) is a promising

technology due to its relative advantage and bright prospect compared with other color e-paper displays. One of the obstacles to its success is lack of effective driving method and fast driving speed for this kind of display which is the scope of this thesis. In the next chapter we will discuss the intrinsic physical and optical characteristics of Ch-LCD.

## 2. Physical and Optical Characteristics of Cholesteric LCD

## 2.1 Introduction

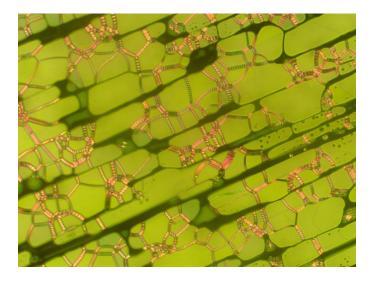

Cholesteric liquid crystal display (Ch-LCD) is a special type of liquid crystal display (LCD). The meaning of the term "cholesteric" differs from that in the medical domain. It is made by adding chiral molecules into the nematic liquid crystal to behave as a helical structure, which is similar to the molecule structure of the natural cholesteric. [14] This is also the reason why it was called the chiral nematic liquid crystal. Figure 2-1 shows a picture of the cholesteric LC cell which was taken by optical polarizing microscopy<sup>4</sup>.

Fig. 2-1 Cholesteric liquid crystal cell picture taken by optical polarizing microscopy

Unlike the conventional LC, the cholesteric liquid crystal molecules form a helical structure, which behaves as two stable states at zero electric or magnetic field. It also has two meta-stable states which could be achieved only by applying a certain voltage level. The planer state of the Ch-LC reflects the light at certain region of wavelength which could be adjusted by adding different dopants leading to different colors' texture. High contrast ratio is also possible through the reflective planer and the scatter focal conic state with a dark backplane. Several meta-stable states could be achieved only if some certain outer conditions are fulfilled, but they are critical in the fast driving schemes. Other characteristics such as the optical properties and the hysteresis are also discussed in this chapter.

15

Naturally Brilliant Color Inspired By Nature, located on the web page: http://www.qualcomm.com/mirasol/benefits

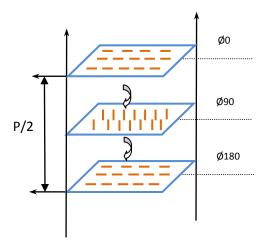

#### 2.2 Molecule Structure of the Ch-LC

The cholesteric molecules are naturally oriented in the same direction in one layer and the direction is rotated around the helical axis when it is sandwiched in the middle of two substrates. As shown in Figure 2-2, the distance for the direction in one layer to rotate 360° is called the pitch of the cholesteric LC. The pitch of the cholesteric liquid crystal could be adjusted by adding different chiral molecules as well as UV radiation, in this way different colors of cholesteric liquid crystal could be achieved. However, the negative point is that the pitch could also be changed by the environment temperature which makes it unendurable to a wide range of temperature shift. In practical applications, the temperature compensation circuit is needed to maintain the stability. [15]

Fig. 2-2 Molecule structure of the cholesteric

The pitch of the cholesteric liquid crystal could be adjusted by varying the concentration of the chiral dopants. The relationship could be expressed by equation:

$$P_0 = \frac{1}{(HTP)x}$$

The HTP denotes the helical twisting power and the x denotes the concentration of the chiral dopants. [16] In addition, the pitch of cholesteric liquid crystal could also be affected by the boundary conditions depending on the display structure and the environmental temperature.

#### 2.3 Stable States of the Ch-LC

As a bi-stable liquid crystal material, the cholesteric liquid crystal has two stable states when it is sandwiched between the two substrates, namely planer state and focal conic state. These two states could be maintained in the display up to several months without any power consumption. Before 1990 the cholesteric liquid crystal suffered many obstacles such as ultra high driving voltage, small viewing angle etc, as the potential of bi-stability was not fully recognized. After the two stable states of the material had been rediscovered in 1990, the performance of the cholesteric liquid crystal display has been improved continuously. [17]

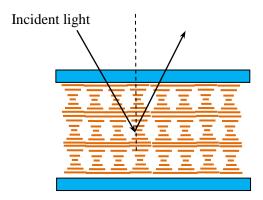

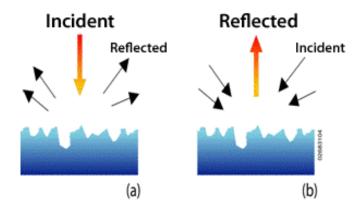

Figure 2-3 below shows the form of cholesteric liquid crystal when aligned in the brighter planer state. In the planer state, the helix axes of the texture are perpendicular to the cell surface. Thus the incident light is reflected according to the Bragg's law and the display appears white/bright.

Fig. 2-3 Molecule structure of planer state Ch-LC

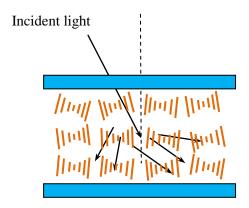

When the cholesteric liquid crystal is in the focal conic state, as depicted in Figure 2-4, the helical axes would be randomly orientated and the incident light into the liquid crystal texture would be weakly scattered.

Fig. 2-4 Molecule structure of the focal conic state Ch-LC

So, if the texture is aligned into the planer state, the cholesteric panel would appear bright due to the strong reflectance. On the other side, when the cholesteric texture is aligned into the focal conic state, the display would turn dark because the incident light is scattered. This unique characteristic is perceived as the on and off of a display cell.

Unlike the two stable states which could maintain themselves without any power supply, there also exist other intermediate states which are essential for the driving of the Ch-LCD.

#### 2.4 Meta-stable States of Ch-LC

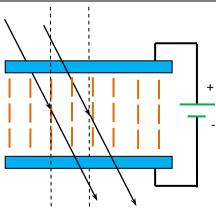

There are also two meta-stable states which can be achieved under certain voltage field crossing the cholesteric texture, namely homeotropic state and transient planer state. Inside the homeotropic state, the helical structure is broken by the applied voltage field. In this state, all liquid crystal molecules are along with the direction of the electrical field. So the liquid crystal texture becomes transparent. The homeotropic state of the cholesteric liquid crystal is meta-stable state. It could only be maintained when the applied voltage field exceeds a certain threshold value. The cholesteric texture will transform to the homeotropic state if the applied voltage field is stronger than the threshold Ec as described below independent of their initial states. In the equation below,  $K_{22}$  is the twist elastic constant,  $\epsilon$  is the dielectric anisotropy and Po is the pitch of the cholesteric liquid crystal. [18]

$$Ec = 2\pi^2 \sqrt{\frac{K_{22}}{\epsilon}} \frac{1}{Po}$$

Figure 2-5 shows the molecule structure of the homeotropic state of the cholesteric texture. When the voltage field above Ec was applied, the cholesteric liquid crystal's helical structure would be broken and the molecules would in the same direction as that of the applied voltage field as shown in Figure 2-5. In the homeotropic state of the cholesteric LC, the incident light passes through the liquid crystal. Consequently, the cholesteric liquid crystal would become transparent in this state. This transient state cannot be maintained when the voltage field is missing. After removing the applied field, depending on the speed of the removing, the homeotropic state cholesteric liquid crystal would be quickly released to the planer state or to another meta-stable state named transient planer state.

Fig. 2-5 Molecule structure of the homeotropic state of ChLC

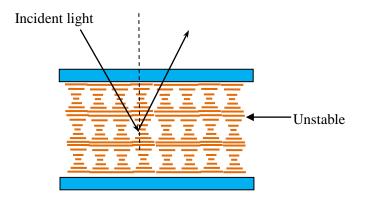

The transient planer state is also a meta-stable state. When the cholesteric texture is driven to the homeotropic state by a strong voltage field, the homeotropic state texture would shift to the planer state or the transient planer state depending on the speed of removing the applied voltage field. If the voltage field is removed slowly, the homeotropic state texture will first remain in a transient planer state. Then it will evolve to the focal conic state. In the other case, if the voltage field is removed quickly, the homeotropic state texture will migrate to the planer state. The structure of the transient planer state is depicted in Figure 2-6 below.

Fig. 2-6 Molecule structure of transient planer state Ch-LC

We can observe that the molecule structure of the transient planer state is almost the same as that in the planer state but not stable. The transient planer state is a critical state which is needed in DDS for the fast driving of the Ch-LCD [19]

The stable and meta-stable states of the Ch-LCD could be used for the fast driving of this kind of display and the bi-stability is achievable thanks to the hysteresis characteristic of the Ch-LC.

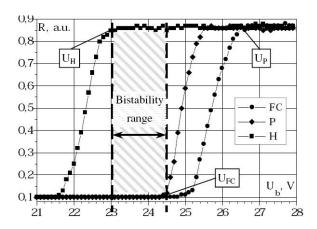

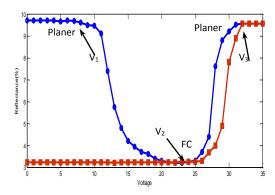

Fig. 2-7 Hysteresis characteristics of the Ch-LC

Figure 2-7 shows the hysteresis characteristics of a typical cholesteric liquid crystal material. The x coordinate defines the applied voltage and the y coordinate is the reflectivity. It could be observed from the figure above that the hysteresis between the transition from the planer to the focal conic state and the transition from the focal conic to the planer state is less than two volts. This gap is the bi-stability region. [20]

The unique characteristics of the Ch-LC are caused by the molecule structure which will be discussed below.

## 2.5 Material and Stability Mechanism

The cholesteric texture used in the display is a mixture of the nematic liquid crystal and chiral dopants.

a. Nematic Liquid Crystal 5CB

$$CH_3 - CH_2 -$$

b. Chiral Dopant CB15

Fig. 2-8 Molecule structure of the typical N-LC and chiral dopant

Figure 2-8 shows the molecule structure of the nematic liquid crystal 5CB and the chiral agent CB15 used for producing the cholesteric liquid crystal material. The molecule structures which are

listed here is the most commonly used material structure for the production of the Ch-LC display. [21]

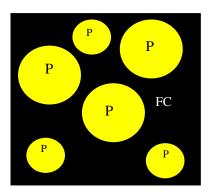

In the nematic liquid crystal such as cholesteric LC, the stable planer and focal conic state could be achieved by two major mechanisms. The first one is called surface stabilized cholesteric texture (SSCT), and the other one is polymer stabilized cholesteric texture (PSCT) developed by Kent Display. Both of the two methods are aimed to enable the cholesteric texture to achieve the two stable states at the same time. That is to say, the activation energy for both states has to be sufficiently low to form stable states. Each of the two methods is achieved by adding certain materials. Most of the cholesteric LCs are aligned in the PSCT mode. In the normal mode of PSCT cholesteric LCD, the focal conic texture is stabilized at zero electric field. The stabilized focal conic state texture is a poly-domain structure and it could scatter the incident light strongly. Moreover, the texture can be switched to the transparent homeotropic texture through an electric field. [22]

## 2.6 Optical Properties

The planer state of the cholesteric texture only reflects certain wavelengths of light. When the light is incident to the surface of the planer state texture at an angle  $\theta$ , only light having the wavelength around  $\lambda$  would be reflected. The critical wavelength could be expressed by the equation below:

$$\lambda = 2\tilde{n} \frac{Po}{2} \cos \theta = \tilde{n} Po \cos \theta$$

Where  $\tilde{n}$  denotes the average refractive index.  $\theta$ : the angle of the incident light and Po: the pitch of the cholesteric texture.

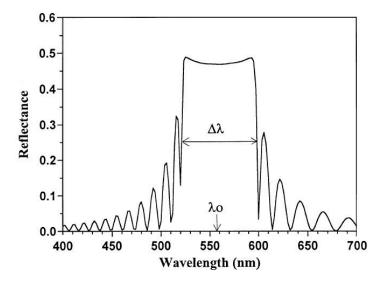

The typical reflection spectrum of the cholesteric texture could be illustrated in Figure 2-9. The horizontal axis defines the wavelength of the reflected light and the vertical axis is the ratio of the reflectance.

Fig. 2-9 Reflection spectrum of Ch-LC vs. linear polarized incident light on planer state

The  $\Delta\lambda$  here denotes the width of the reflection band. The planer state cholesteric texture could reflect about 50% of the un-polarized light. On the other side, the focal conic texture has a very dark optical appearance because the incident light is scattered. [23]

The wavelength of the reflected light can be adjusted by changing the pitch of the cholesteric texture. Normally, the method is to add certain dopant as well as to be irradiated under various ultraviolet processes. In such a way, the wavelength of the reflected light could be precisely controlled in the domain of visible light. Thus, the reflective planer state in the cholesteric LC could display different colors.

This characteristic enables the color cholesteric LCD without usage of color filter that were not possible many other E-paper technologies, giving the cholesteric LCD a natural advantage among the next generation color e-papers.

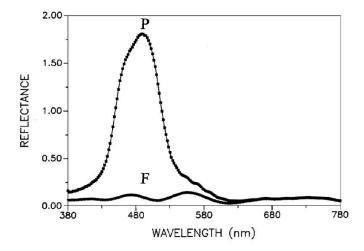

Figure 2-10 shows the reflection spectrum of the two stable states, the planer and focal conic state. In the cholesteric LCD, usually a black backplane is used to absorb the light which leads to a darker appearance as well as higher contrast ratio.

Fig. 2-10 Reflection spectrum of Ch-LC vs. wavelength of the linear polarized incident light on two stable states. (The reflectance unit is arbitrary.)

# 2.7 Conclusion

In this chapter, the basic physical and electro-optical characteristics of the cholesteric LC are shown. Two meta-stable states namely homeotropic and transient planer state are rediscovered for fast switching between the two stable states. The optical properties and stable mechanism of the cholesteric texture are also discussed. These unique characteristics of the cholesteric LC make it an ideal candidate for electronic paper that could be extended to many applications. However, the color gamut and the color saturation of cholesteric liquid crystal need to be further improved. In the lab level, the color cholesteric LCD by using 3 layers' stack has been made by Fujistu, besides, ITRI also developed the one layer color cholesteric LCD. But both still need to improve the reflectivity and the color reproduction in order to emerge as a leader in the market. We will introduce in the next chapter several driving schemes, and how to effectively drive the Ch-LCD between the two stable states.

# 3. Driving Schemes of the Cholesteric LCD

# 3.1 Introduction

It has been several decades gone since the cholesteric liquid crystal was deemed to a promising candidate for electro-optical flat plane display. However, one of the primary obstacles between the thought and realization is the lack of convenient and effective methods to switch between the two stables states which are bright planer state (P) and dark focal conic state (FC) at a high speed. [24] In this chapter, we will discuss the transition mechanism among all of the states the cholesteric LC could have. The development of the driving scheme from the conventional driving method to the fast dynamic driving method will also be introduced in details. As an improvement, an enhanced dynamic driving scheme with gray scale's capability would also be proposed.

#### 3.2 State Transition of the Ch-LCD

As a bi-stable reflective display, unlike the normal liquid crystal display, the cholesteric texture could maintain in its two stable states after removing the applied voltages. Thus the driving of the cholesteric LCD is actually to switch the cholesteric texture between the two stable states.

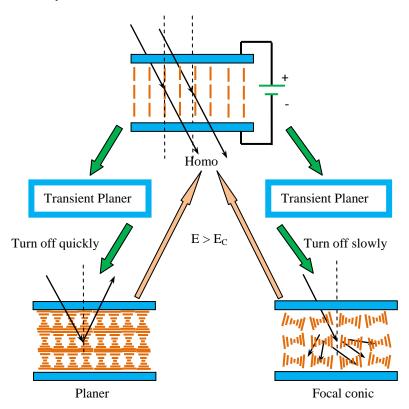

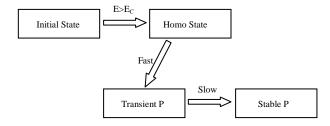

Fig. 3-1The switching sequence among several states of cholesteric LCD

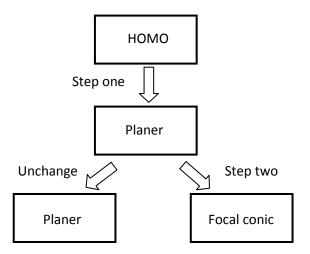

Due to the intrinsic characteristics of the cholesteric texture, the fast switching between the two stable states needs through other meta-stable states. Figure 3-1 illustrates the switch diagram of the several states of the cholesteric liquid crystal display. As we have introduced in the last chapter, planer and focal conic states are two stable states if no additional voltages are applied. In the stable states, the cholesteric molecule will aligned into a helical structure. The difference between the two stable states is that direction of the helical axis.

In the planer state's texture, the helical axis is all aligned into the same direction and perpendicular to the cell surface, thus the incident light would be reflected by the texture and the pixel would be bright. While in the focal conic state, the helical axis is randomly oriented in the texture. Then the incident light will be scattered and the pixel appears dark.

The mechanisms for switching between the two stable states are quite different. If the texture is initially in the planer state, switching from planer to the focal conic state is simple. The electric field across the display cell would make the planer texture instable because the liquid crystal will perpendicular to the field and the electric energy in the cell will be quite high. Thus the liquid crystal would be switched to the focal conic state in which the axis is parallel to the field and the electric energy would be reduced. The achieved focal conic state texture would be stable when the applied field is removed. This process usually needs around 1ms to get completed. However, if we want to switch back to the planer state from the focal conic state, the process would be more complicated. In general, it has to be performed in two steps. In the first step, the focal conic state texture has to be switched to a so called homeotropic state first by applying a voltage which exceeds certain threshold voltage which is thus high enough to make this transition. The value of the threshold voltage could be expressed below:

$$Ec = \frac{\pi^2}{P_0} \sqrt{\frac{K_{22}}{\epsilon_0 \Delta \epsilon}}$$

3-1

As expressed in equation 3-1, the threshold voltage Ec is related to several parameters.  $P_0$  is the pitch of the cholesteric texture and the  $K_{22}$  is the twist elastic constant.

Fig. 3-2 The transition diagram from the initial state to the planer state

Figure 3-2 illustrates the transition diagram of the cholesteric texture switching from the initial state to the planer state. As shown in Figure 3-2, when the applied electric field  $E > E_C$ , the field

would be high enough to unwind helical structure of the molecules. In this situation, all of the molecules will along with the direction of the electric field and the texture will become transparent. Thus, the cholesteric texture would be held in homeotropic state. If the applied field was turned off quickly, the homo state texture would relax to the planer state in two steps. In the first step, the high voltage maintained homo state texture would be switched to a transient planer state which is not stable. In the second step, the texture would be switched from the transient planer state to the stable planer state. The transient planer texture has a pitch of  $2P_0$  [25]. This transition normally needs 10 ms to 100 ms to complete depending on different cholesteric textures and conditions.

# 3.3 Conventional Driving Scheme

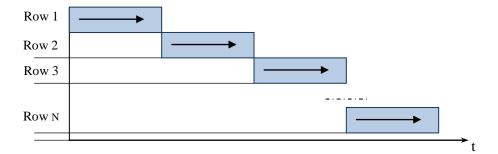

Before the meta-stable transient planer state of the Ch-LC is fully recognized by people, the cholesteric LCD was driven by the conventional way which is to switch between the two stable states directly one row after another. This driving scheme is called static driving scheme comparing to the dynamic driving scheme which will be discussed later. The static driving is to scan pixel by pixel from the top to end of the display and the timing sequence is depicted below.

Figure 3-3 shows the time sequence of the typical static driving scheme. The conventional driving method is quite slow because the next row could be scanned only when the scanning of the last row is finished.

Fig. 3-3 Timing diagram of the static driving scheme of the Ch-LCD

The static driving scheme needs more than 50 ms to refresh one row leading to a low driving speed. This driving scheme allows higher contrast ratio as well as higher image quality because the former created rows will not be affected by the driving waveforms applied to the rows after them. However, the fatal drawback of it is the awfully long driving time. For a 100 rows display, usually 5 seconds will be needed to refresh an image. [26]

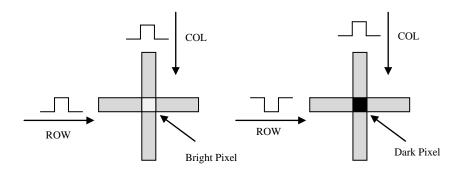

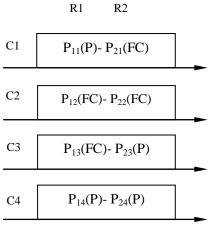

In the conventional driving scheme, the waveforms from the related row i and column j are added simultaneously to the aimed pixel  $P_{ij}$ . By adding different phases of waveforms from the row and

column lines, the resulted effective voltage field across the pixel will be either in a high or in a low level. By controlling the amount of the effective voltage field applied across the pixel, the controlled pixel could be switched either the planer state or the focal conic state. Figure 3-4 illustrates how the pixel is controlled in the conventional driving scheme.

Fig. 3-4 driving method of the conventional driving scheme

The static driving of the cholesteric is simple and easy to achieve high image quality. Besides, because the driving of one row doesn't have any influence on other rows, the crosstalk would not be a problem. The robustness against temperature's fluctuation would also be good for the static driving. However, as we have discussed previously, the awfully long driving time of this driving scheme is an obvious deficiency.

# 3.4 Dynamic Driving Scheme (DDS)

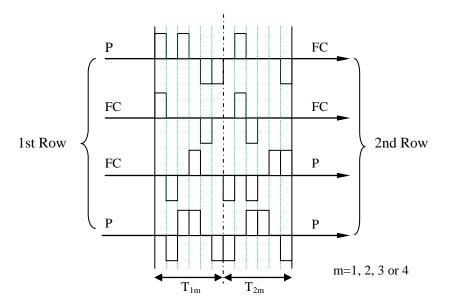

Along with the resolution of the cholesteric LCD getting higher, the conventional driving scheme costing more or less 50ms per line becomes unpractical. Considering the unique characteristics of the Ch-LC, in 1995, X.Y. Huang etc. suggested a new driving method [27] called dynamic driving scheme which has the ability to drive the cholesteric LCD as fast as 1ms per line in spite of how many lines was controlled. The dynamic driving scheme makes use of the fast transition from the meta-stable homeotropic state to the transient planer state and the hysteresis between the planer state and focal conic state.

Fig. 3-5 Driving sequence of one row in the dynamic driving scheme

Figure 3-5 shows the driving sequence of the dynamic driving scheme proposed by X.Y. Huang etc. Different from the conventional driving scheme, all pixels are firstly switched to a meta-stable homeotropic state. After that pixels are switched from the homeotropic state to a transient planer state in a quite high speed. This characteristic was introduced to drive the cholesteric LCD with a short driving time in the range of 1 millisecond.

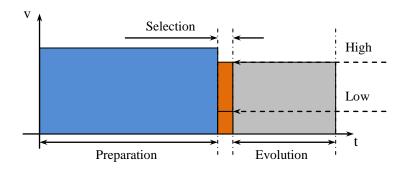

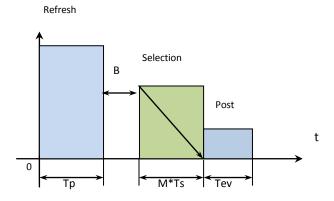

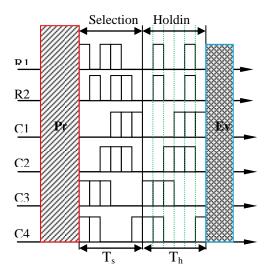

Huang etc. suggested a three stages driving sequence in the dynamic driving scheme as shown in Fig 3-5. The three stages were called preparation stage, selection stage and evolution stage. Driving waveform used in this scheme is a 1000 Hz alternating pulse wave.

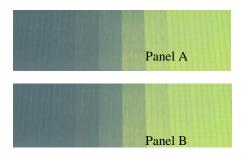

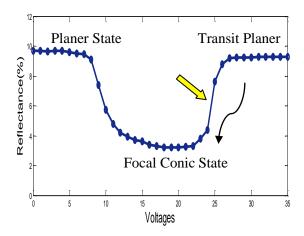

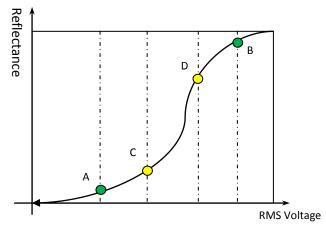

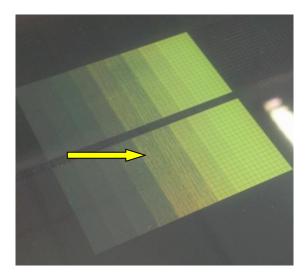

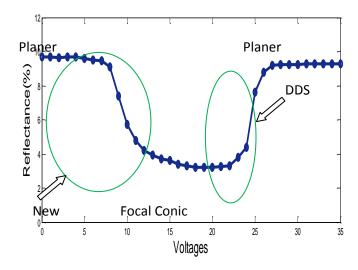

To better explain the dynamic driving scheme, we would like to introduce the R-V curve of the cholesteric LCD. Figure 3-6 shows reflectance versus applied voltage of the cholesteric texture. As marked in the image by a yellow arrow, the homeotropic state will be fast switched to a transient planer state by applying a low voltage in the selection stage. Then the selected texture will slowly evolve to the focal conic state. The evolving time could be overlapped during adjacent lines, thus the driving time increases with the number of rows only in the selection stage.

Fig. 3-6 Reflectance vs. Voltages in the Cholesteric LCD

First of all, in the preparation stage, higher driving voltage was added and sustained for 60 ms to refresh all pixels into the homeotropic state. After that, in the selection stage, driving waveform would determine that the selected pixels were switched to the planer state or eventually transferred to the focal conic state.

The selection was executed by controlling the effective electric field in the selection stage. If a higher electric field is added, the homeotropic state texture will be kept, on the contrary, if the added electric field was low enough, the homeotropic texture in the selection stage will be changed to the transit planer state.

The third stage was named evolution stage. This stage combined with the selection stage was designed to complete the process of the transition. In the selection stage, if the pixel was kept in the homeotropic state, the electric field in the evolution state will keep maintaining it at that state until the end of the driving waveform.

In the end of the driving sequence, when the evolution's electric field was turned off, the maintained homo state pixels will quickly be switched to the planer state. On the other side, if the pixel was given a low electric field in the selection stage, the achieved transit planer pixels will change to the focal conic state slowly during the process of the evolution state. After the evolution stage was turned off, stable focal conic state pixels will be achieved. [28]

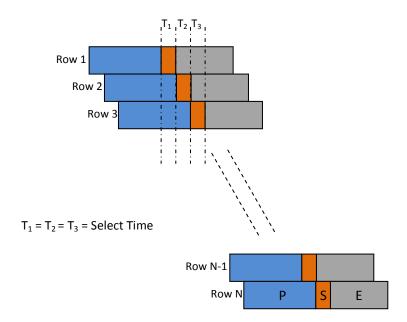

Figure 3-7 below illustrates the schematic diagram of this dynamic driving scheme. We could compare it with that of the conventional driving scheme. The specific difference is, in the dynamic driving scheme, when the first row is still in progress, the next several rows will already start to be processed.

In the dynamic driving scheme, the preparation and evolution stages are still kept in their original lengths. However, because the preparation and evolution waveforms are overlapped among lines in time, the total driving time of the whole scheme for a N rows display would be as long as the time needed for one row in the two stages (Preparation and Evolution stages) plus the  $N \times Ts$ (selection time). Considering a 1000-line Ch-LCD, only 1080 ms equals 1.08 s was needed which is much more reasonable than the conventional driving scheme. [29]

Fig. 3-7 Schematic diagram showing how the Ch-LCD is addressed in DDS

As the first try, the dynamic driving scheme proposed in 1995 has largely increased the driving speed of the cholesteric LCD. However, it still has a lot of room to improve. Firstly, the number of voltages for the driving scheme is still quite high. A common solution with four voltages in rows and two voltages in columns will increase the driver chip's complexity. Secondly, voltages used in the dynamic driving scheme are in really high values leading to high power consumption. As an improvement, a dynamic driving scheme named  $U/\sqrt{2}$  was proposed by A. Kozachenko in 1997. [30]

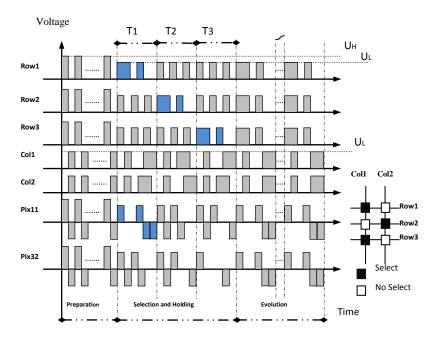

## 3.4.1 DDS $U/\sqrt{2}$

The  $U/\sqrt{2}$  dynamic driving scheme (DDS) features a quite simplistic waveform pattern and only two voltages are needed for the whole driving scheme, which are U and zero. The cross pixel's electric field have three possibilities, U, -U and zero.

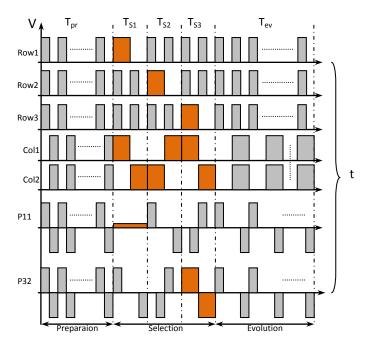

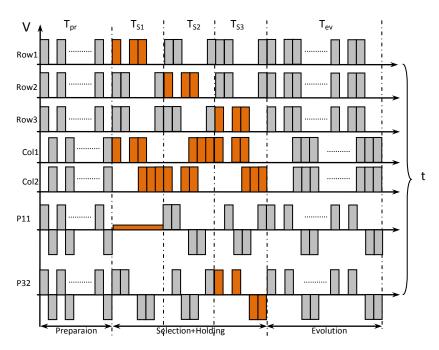

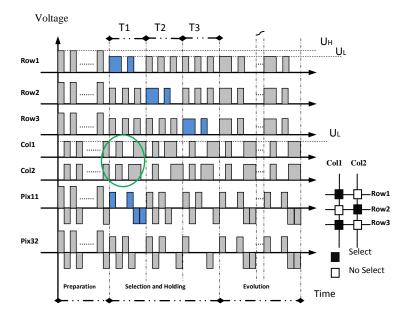

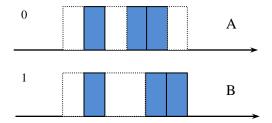

Figure 3-8 shows the waveform pattern of the  $U/\sqrt{2}$  dynamic driving scheme on a  $3\times2$  pixel matrix. The waveform part marked by orange color is the waveform in the selection stage of the driving scheme.

Fig. 3-8 Sample of the  $U/\sqrt{2}$  DDS for a 3×2 Ch-LCD pixel matrix

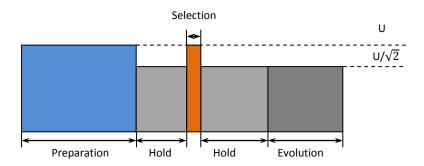

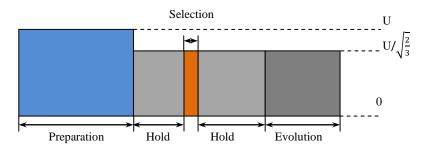

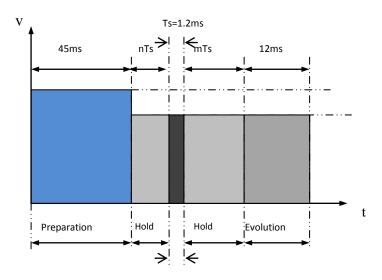

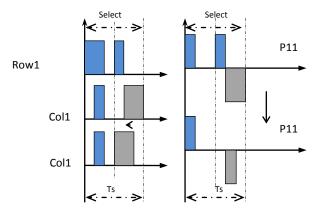

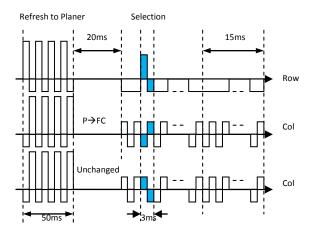

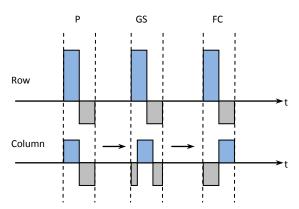

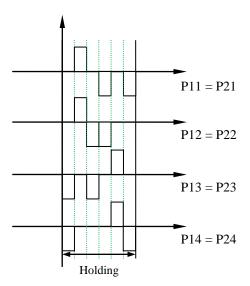

Different from the first dynamic driving scheme, in the  $U/\sqrt{2}$  dynamic driving scheme, the whole driving scheme was divided into four stages, which are preparation stage, selection stage, holding stage and evolution stage. The holding stage is placed before and/or after the selection stage to hold the cholesteric texture. The arrangement of the four stages could be observed in Figure 3-9.

Fig. 3-9 Driving stages of the  $U/\sqrt{2}$  dynamic driving scheme

The critical voltage U is used in the preparation stage to refresh all pixels of the display into the homeotropic state. The holding stage is between both of the preparation and selection stages and/or selection and evolution stages. The holding part before the selection stage is to hold the homeotropic state until the selection stage comes. Holding part after the selection stage is to combine with evolution stage to let the selected pixels evolving to the focal conic state. The RMS voltage  $U_H$  in the holding stage and the RMS voltage  $U_E$  in the evolution stage have the constant ratio with the preparation voltage U. In these two stages, the voltage is applied for half of the selection time, thus the RMS voltage in holding and evolution stage is  $U_H = U_E = U/\sqrt{2}$ . The RMS

voltage in the selection stage either in U or zero could select the pixel into the planer or focal conic state.

The  $U/\sqrt{2}$  features less number of voltages needed in the whole driving scheme. However, because the effective electric field only exists in half of the holding stages, higher driving voltages are required for achieving a high RMS electric field. In order to reduce the driving voltages in an effective way, another more effectual improvement called  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme would be discussed below. [31]

# 3.4.2 DDS U/ $\sqrt{\frac{3}{2}}$

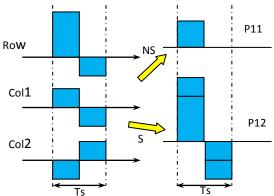

As it was named, the  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme also has constant correlations among the effective voltage values of the four driving stages. Different from the  $U/\sqrt{2}$  scheme, the number of subdivision is six in all of the stages excluding the preparation stage. As to the waveform type, the root of mean square value of effective voltage could be higher than that in the  $U/\sqrt{2}$  under the same applied voltage U. Thus, the applied voltage could actually be reduced by 18% in this scheme. The timing diagram of the  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme is depicted in Figure 3-10.

Fig. 3-10 Sample of the U/ $\sqrt{\frac{3}{2}}$  DDS for a 3×2 Ch-LCD pixel matrix

As to the timing diagram, a sample of  $3\times2$  pixel matrix was selected. From the timing diagram of the  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme we could observe that in selection, holding and evolution stages, if the pixel was planned to selected to planer state, the cross pixel's voltage is for 2/3 of the driving time high. On the contrary, if the pixel was planned to selected to the focal conic state, the cross pixel's voltage will be zero. The effective voltage field added on the pixel could be calculated according to the equation below:

$$V_{rms} = \sqrt{\frac{{V_1}^2 T_1 + {V_2}^2 T_2 + \cdots {V_n}^2 T_n}{T_s}}$$

$$= U \sqrt{\frac{T_1 + T_2 + \cdots T_n}{T_s}}$$

3-2

$T_1, T_2... T_n$  are time periods of each pulse when  $U \neq 0$ .

As it could be found in Equation 3-2, Ts is the selection time while  $T_1$  to Tn are the time of the sub divisions within one selection stage when the applied voltage is not zero. V1 to Vn are the relevant voltage levels.

Because the cholesteric liquid crystal texture responses to the root of mean square (RMS) of the applied voltages, the RMS voltage value in the selection stage of this driving scheme could be calculated from equation 3-2 that:

$$V_{S} = U_{1} / \sqrt{\frac{4}{6}} = U_{1} / \sqrt{\frac{2}{3}}$$

3-3

RMS voltage Vs calculated from Equation 3-3 is for switching the pixel to the planer state or

$$V_{S}=0$$

3-4

The Vs value in Equation 3-4 is the voltage to switch the pixel into the focal conic state.

On the other side, the RMS voltage value in the selection stage of the  $U/\sqrt{2}$  dynamic driving scheme is:

$$V_s = U/\sqrt{2}$$

3-5

Vs here in Equation 3-5 is the value which is needed to switch the pixel into the planer state in  $U/\sqrt{2}$  DDS or

$$V_{S}=0$$

3-6

The Vs in Equation 3-6 is the value to select the pixel into the focal conic state in  $U/\sqrt{2}$  DDS.

According to the equations above that the cholesteric texture response to the RMS value of the applied voltage, giving the same RMS voltage value in the selection stage. There exists:

$$U_1/\sqrt{\frac{2}{3}} = U$$

3-7

Thus, we could conclude that:

$$U_1 = U \times \sqrt{\frac{2}{3}} \approx 0.82 \text{ U}$$

3-8

$$U_1 / U \approx 0.82$$

3-9

From the computed result in 3-9 we could draw the conclusion that the voltage applied in the selection, holding and evolution stages of the  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme could be 18% less than that in the  $U/\sqrt{2}$  driving scheme.

Fig. 3-11 Driving sequence of the  $U/\sqrt{\frac{3}{2}}$  DDS

The driving sequence of the  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme includes four stages as could be observed in Figure 3-11, which is almost the same as those in the  $U/\sqrt{2}$  DDS. The effective voltage levels in the selection, holding and evolution stages all have the same correlation with the applied voltage U:

$$U_{HOLD} = U_{SEL} = U_{EVL} = U / \sqrt{\frac{3}{2}}$$

3-10

That's why this driving scheme was called  $U/\sqrt{\frac{3}{2}}$  dynamic driving scheme.

As we have calculated, the six divisions' pattern in the selection stage as shown in Figure 3-10 is more effective to make use of the applied voltage for achieving a higher RMS voltage level. Thus,

the applied voltage could be reduced comparing to that in the four divisions' driving scheme. The eight or more divisions also could be used but the effective RMS values could not get higher. Therefore the six divisions' method of the selection time is reasonable.

It has to be mentioned here that the preparation time of the  $U/\sqrt{\frac{3}{2}}$  DDS must be longer than that of the  $U/\sqrt{2}$  DDS because the preparation voltage was also reduced.

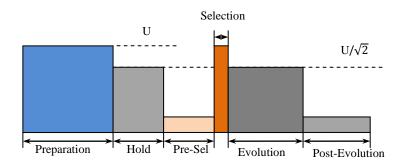

#### 3.4.3 Fast Dynamic Driving Scheme

In the pursuit of higher driver speed, an effective and reasonable solution is to reduce the selection time as short as possible. A typical approach was proposed for this by A. Rybalochka etc. in 2000. The driving scheme was named fast dynamic driving scheme which has the ability to reduce the selection time 4 to 5 times comparing to the selection time in the normal DDS, usually 1~2 millisecond. [32]

The driving sequence of the fast driving scheme is as follows:

Fig. 3-12 Driving sequence of fast driving DDS

As the driving sequence of the fast driving scheme shown in Figure 3-12, the driving scheme has six driving stage which are preparation, holding pre-selection, selection, evolution and post-evolution stages. Comparing to the  $U/\sqrt{\frac{3}{2}}$  DDS, the fast DDS has two more driving stages which are named pre-selection and post-evolution stages.

During the pre-selection stage, the  $U_{\text{pre-s}} = U_{\text{col}}$  is added to pixels. The voltage  $U_{\text{col}}$  in the pre-selection stage is set to be low enough to initiate the transition from the homeotropic state to the transient planer state. The voltage field in the selection stage will determine either the pixel will stay in the transient planer state or backing to the homeotropic state.

After the evolution stage, there is also a so called post-evolution stage with the voltage value  $U_{p\text{-ev}} = U_{\text{col}}$ . The post-evolution stage is not for driving but for the driving principles.

By adopting this driving method, driving speed could be enhanced to  $1/4 \sim 1/5 \Gamma$ , the  $\Gamma$  here is the transition time from the homeotropic state to the transient planer state of the cholesteric texture.

Along with the increasing number of the driving stages as well as complexity, the driving speed could be enhanced. However, driving voltages in these methods above are still quite high. On the other side, these DDS only concentrate on the on-off control of the cholesteric LCD but not on gray scales. Thus, DDS with gray scales' capability will be of great interesting.

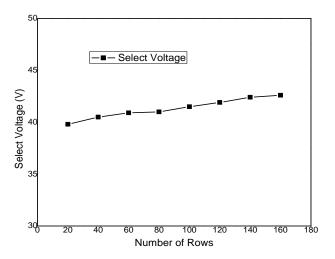

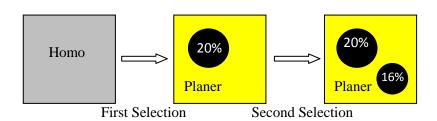

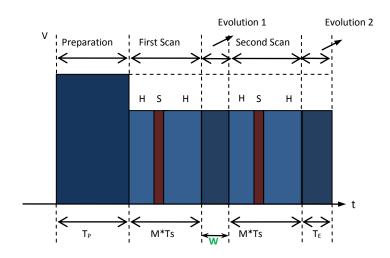

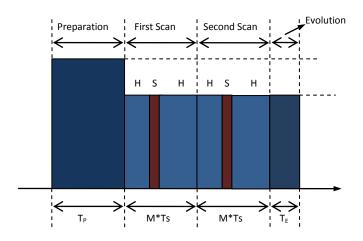

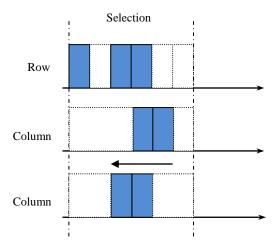

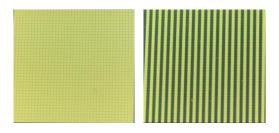

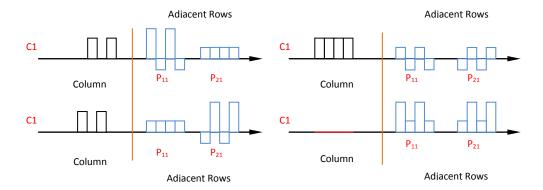

# 3.5 Enhanced DDS with Gray Scale Capability

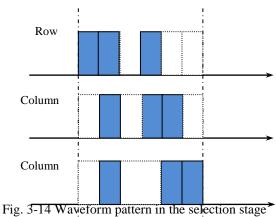

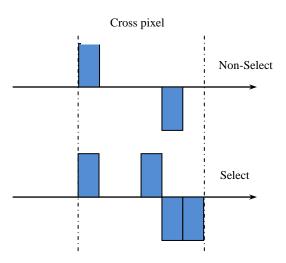

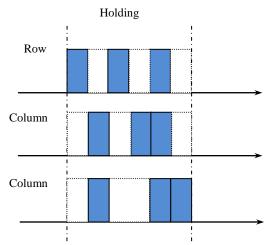

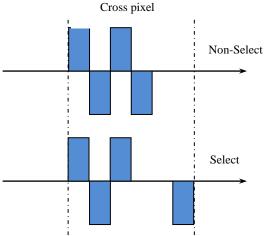

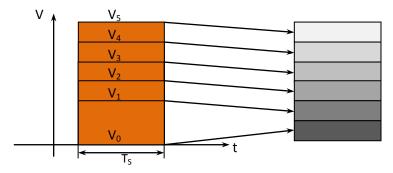

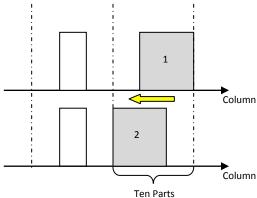

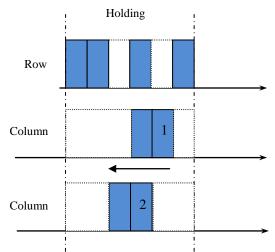

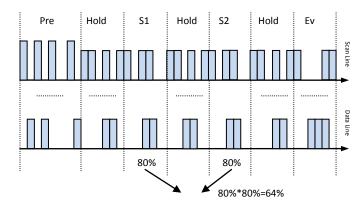

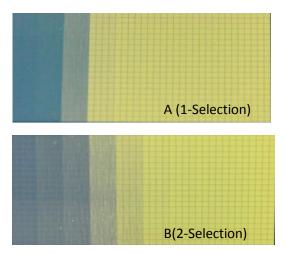

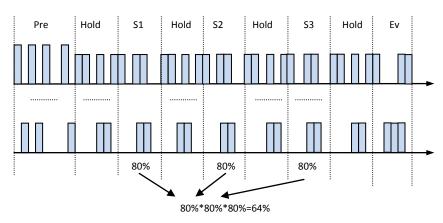

In Euro Display 2011, we proposed an enhanced dynamic driving scheme with the gray scale capability. [33] In the enhanced DDS, six divisions' waveform pattern was used in the selecting and holding stages to reduce the maximum driving voltages. The new DDS with modified preparation and selection waveforms can be easily used to drive the Ch-LCD into both the on-off state and gray scale state. The driving voltages used in this driving scheme are lower comparing to the several ones above. In addition, the number of driving stages and number of voltages needed are both smaller.